CHAPTER

6

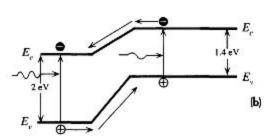

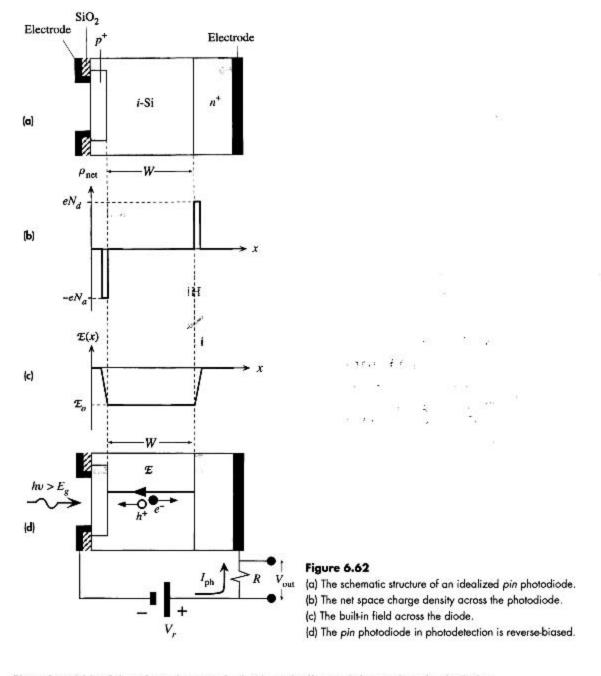

## Semiconductor Devices

Most diodes are essentially pn junctions fabricated by forming a contact between a p-type and an n-type semiconductor. The junction possesses rectifying properties in that a current in one direction can flow quite easily whereas in the other direction it is limited by a leakage current that is generally very small. A transistor is a three-terminal solid-state device in which a current flowing between two electrodes is controlled by the voltage between the third and one of the other terminals. Transistors are capable of providing current and voltage gains thereby enabling weak signals to be amplified. Transistors can also be used as switches just like electromagnetic relays. Indeed, the whole microcomputer industry is based on transistor switches. The majority of the transistors in microelectronics are of essentially two types: bipolar junction transistors (BJTs) and field effect transistors (FETs). The appreciation of the underlying principles of the pn junction is essential to understanding the operation of not only the bipolar transistor but also a variety of related devices. The central fundamental concept is the minority carrier injection as purported by William Shockley in his explanations of the transistor operation. Field effect transistors operate on a totally different principle than BJTs. Their characteristics arise from the effect of the applied field on a conducting channel between two terminals. The last two decades have seen enormous advances and developments in optoelectronic and photonic devices which we now take for granted, the best examples being light emitting diodes (LEDs), semiconductor lasers, photodetectors, and solar cells. Nearly all these devices are based on pn junction principles. The present chapter takes the semiconductor concepts developed in Chapter 5 to device level applications, from the basic pn junction to heterojunction laser diodes.

## 6.1 IDEAL pn JUNCTION

## 6.1.1 No Applied Bias: Open Circuit

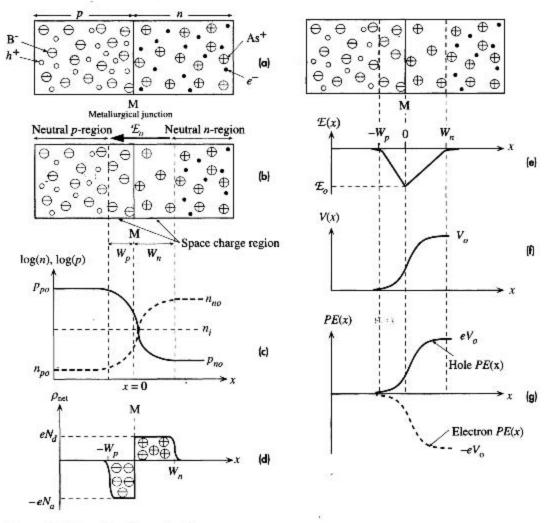

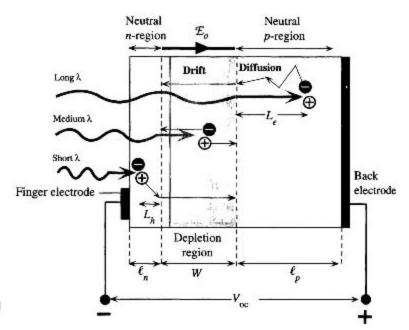

Consider what happens when one side of a sample of Si is doped *n*-type and the other *p*-type, as shown in Figure 6.1a. We assume that there is an abrupt discontinuity between the *p*- and *n*-regions, which we call the **metallurgical junction** and label as M in Figure 6.1a, where the fixed (immobile) ionized donors and the free electrons (in the conduction band, CB) in the *n*-region and fixed ionized acceptors and holes (in the valence band, VB) in the *p*-region are also shown.

Due to the hole concentration gradient from the p-side, where  $p = p_{po}$ , to the n-side, where  $p = p_{no}$ , holes diffuse toward the right. Similarly the electron concentration

Figure 6.1 Properties of the pn junction.

gradient drives the electrons by diffusion toward the left. Holes diffusing and entering the n-side recombine with the electrons in the n-side near the junction. Similarly, electrons diffusing and entering the p-side recombine with holes in the p-side near the junction. The junction region consequently becomes depleted of free carriers in comparison with the bulk p- and n-regions far away from the junction. Note that we must, under equilibrium conditions (e.g., no applied bias or photoexcitation), have  $pn = n_i^2$  everywhere. Electrons leaving the n-side near the junction M leave behind exposed positively charged donor ions, say  $As^+$ , of concentration  $N_d$ . Similarly, holes leaving the p-region near M expose negatively charged acceptor ions, say  $B^-$ , of concentration  $N_a$ . There is therefore a **space charge layer** (SCL) around M. Figure 6.1b shows the **depletion region**, or the space charge layer, around M, whereas Figure 6.1c illustrates the hole and electron concentration profiles in which the vertical concentration scale is logarithmic. The depletion region is also called the transition region.

It is clear that there is an internal electric field  $\mathcal{L}_o$  from positive ions to negative ions, that is, in the -x direction, that tries to drift the holes back into the p-region and electrons back into the n-region. This field drives the holes in the opposite direction to their diffusion. As shown in Figure 6.1b,  $\mathcal{L}_o$  imposes a drift force on holes in the -x direction, whereas the hole diffusion flux is in the +x direction. A similar situation also applies for electrons with the electric field attempting to drift the electrons against diffusion from the n-region to the p-region. It is apparent that as more and more holes diffuse toward the right, and electrons toward the left, the internal field around M will increase until eventually an "equilibrium" is reached when the rate of holes diffusing toward the right is just balanced by holes drifting back to the left, driven by the field  $\mathcal{L}_o$ . The electron diffusion and drift fluxes will also be balanced in equilibrium.

For uniformly doped p- and n-regions, the net space charge density  $\rho_{\rm net}(x)$  across the semiconductor will be as shown in Figure 6.1d. (Why are the edges rounded?) The net space charge density  $\rho_{\rm net}$  is negative and equal to  $-eN_a$  in the SCL from  $x = -W_p$  to x = 0 (where we take M to be) and then positive and equal to  $+eN_d$  from x = 0 to  $W_n$ . The total charge on the left-hand side must be equal to that on the right-hand side for overall charge neutrality, so

$$N_a W_p = N_d W_n ag{6.1}$$

Depletion widths

In Figure 6.1, we arbitrarily assumed that the donor concentration is less than the acceptor concentration,  $N_d < N_a$ . From Equation 6.1 this implies that  $W_n > W_p$ ; that is, the depletion region penetrates the *n*-side, the lightly doped side, more than the *p*-side, the heavily doped side. Indeed, if  $N_a \gg N_d$ , then the depletion region is almost entirely on the *n*-side. We generally indicate heavily doped regions with the plus sign as a superscript, that is,  $p^+$ .

The electric field  $\mathcal{E}(x)$  and the net space charge density  $\rho_{net}(x)$  at a point are related in electrostatics<sup>1</sup> by

$$\frac{d\mathcal{E}}{dx} = \frac{\rho_{\text{net}}(x)}{\varepsilon}$$

Field and net space charge density

This is called Gauss's law in point form and comes from Gauss's law in electrostatics. Gauss's law is discussed in Section 7.5.

where  $\varepsilon = \varepsilon_o \varepsilon_r$  is the permittivity of the medium and  $\varepsilon_o$  and  $\varepsilon_r$  are the absolute permittivity and relative permittivity of the semiconductor material. We can thus integrate  $\rho_{\text{net}}(x)$  across the diode and thus determine the electric field  $\mathcal{E}(x)$ , that is,

Field in depletion region

$$\mathcal{E}(x) = \frac{1}{\varepsilon} \int_{-W_0}^{x} \rho_{\text{net}}(x) \ dx$$

[6.2]

The variation of the electric field across the pn junction is shown in Figure 6.1e. The negative field means that it is in the -x direction. Note that  $\mathcal{E}(x)$  reaches a maximum value  $\mathcal{E}_n$  at the metallurgical junction M.

The potential V(x) at any point x can be found by integrating the electric field since by definition  $\mathcal{E} = -dV/dx$ . Taking the potential on the p-side far away from M as zero (we have no applied voltage), which is an arbitrary reference level, then V(x) increases in the depletion region toward the n-side, as indicated in Figure 6.1f. Its functional form can be determined by integrating Equation 6.2, which is, of course, a parabola. Notice that on the n-side the potential reaches  $V_o$ , which is called the **built-in potential**.

The fact that we are considering an abrupt pn junction means that  $\rho_{net}(x)$  can simply be described by step functions, as displayed in Figure 6.1d. Using the step form of  $\rho_{net}(x)$  in Figure 6.1d in the integration of Equation 6.2 gives the electric field at M as

Built-in field

$$\mathcal{E}_o = -\frac{eN_dW_n}{\varepsilon} = -\frac{eN_aW_p}{\varepsilon}$$

[6.3]

where  $\varepsilon = \varepsilon_o \varepsilon_r$ . We can integrate the expression for  $\mathcal{E}(x)$  in Figure 6.1e to evaluate the potential V(x) and thus find  $V_o$  by putting in  $x = W_n$ . The graphical representation of this integration is the step from Figure 6.1e to f. The result is

Built-in voltage

$$V_o = -\frac{1}{2} \mathcal{E}_o W_o = \frac{e N_a N_d W_o^2}{2\varepsilon (N_a + N_d)}$$

[6.4]

where  $W_o = W_n + W_p$  is the total width of the depletion region under a zero applied voltage. If we know  $W_o$ , then  $W_n$  or  $W_p$  follows readily from Equation 6.1. Equation 6.4 is a relationship between the built-in voltage  $V_o$  and the depletion region width  $W_o$ . If we know  $V_o$ , we can calculate  $W_o$ .

The simplest way to relate  $V_o$  to the doping parameters is to make use of the fact that in the system consisting of p- and n-type semiconductors joined together, in equilibrium, Boltzmann statistics<sup>2</sup> demands that the concentrations  $n_1$  and  $n_2$  of carriers at potential energies  $E_1$  and  $E_2$  are related by

$$\frac{n_2}{n_1} = \exp\left[-\frac{(E_2 - E_1)}{kT}\right]$$

where E = qV, where q is the charge of the carrier. Considering electrons (q = -e), we see from Figure 6.1g that E = 0 on the p-side far away from M where  $n = n_{\infty}$ , and

<sup>&</sup>lt;sup>2</sup> We use Boltzmann statistics, that is,  $n|E| \propto \exp[-E/kT]$ , because the concentration of electrons in the conduction band, whether on the n-side or p-side, is never so large that the Pauli exclusion principle becomes important. As long as the carrier concentration in the conduction band is much smaller than  $N_c$ , we can use Boltzmann statistics.

$E = -eV_0$  on the *n*-side away from M where  $n = n_{n0}$ . Thus

$$\frac{n_{po}}{n_{ro}} = \exp\left(-\frac{eV_o}{kT}\right)$$

[6.5a]

Boltzmann statistics for electrons

This shows that  $V_a$  depends on  $n_{no}$  and  $n_{po}$  and hence on  $N_d$  and  $N_a$ . The corresponding equation for hole concentrations is clearly

$$\frac{p_{no}}{p_{no}} = \exp\left(-\frac{eV_o}{kT}\right) \tag{6.5b}$$

Thus, rearranging Equations 6.5a and b we obtain

$$V_o = \frac{kT}{e} \ln \left( \frac{n_{no}}{n_{oo}} \right)$$

and  $V_o = \frac{kT}{e} \ln \left( \frac{p_{po}}{p_{no}} \right)$

We can now write  $p_{po}$  and  $p_{no}$  in terms of the dopant concentrations inasmuch as  $p_{po} = N_a$  and

$$p_{no} = \frac{n_i^2}{n_{no}} = \frac{n_i^2}{N_d}$$

so Va becomes

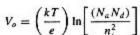

$$V_o = \frac{kT}{e} \ln \left( \frac{N_a N_d}{n_i^2} \right)$$

[6.6] Built-in voltage

Clearly  $V_o$  has been conveniently related to the dopant and material properties via  $N_a$ ,  $N_d$ , and  $n_i^2$ . The built-in voltage  $(V_o)$  is the voltage across a pn junction, going from p- to n-type semiconductor, in an open circuit. It is not the voltage across the diode, which is made up of  $V_o$  as well as the contact potentials at the metal-to-semiconductor junctions at the electrodes. If we add  $V_o$  and the contact potentials at the electroded ends, we will find zero.

Once we know the built-in potential from Equation 6.6, we can then calculate the width of the depletion region from Equation 6.4, namely

$$W_o = \left[\frac{2\varepsilon(N_a + N_d)V_o}{eN_aN_d}\right]^{1/2}$$

[6.7] Depletion region width

Notice that the depletion width  $W_o \propto V_o^{1/2}$ . This results in the capacitance of the depletion region being voltage dependent, as we will see in Section 6.3.

**THE BUILT-IN POTENTIALS FOR Ge, Si, AND GaAs pn JUNCTIONS** A pn junction diode has a concentration of  $10^{16}$  acceptor atoms cm<sup>-3</sup> on the p-side and a concentration of  $10^{17}$  donor atoms cm<sup>-3</sup> on the n-side. What will be the built-in potential for the semiconductor materials Ge, Si, and GaAs?

## **EXAMPLE 6.1**

#### SOLUTION

The built-in potential is given by Equation 6.6, which requires the knowledge of the intrinsic concentration for each semiconductor. From Chapter 5 we can tabulate the following at 300 K:

| Semiconductor | $E_g$ (eV) | $n_i  (\mathrm{cm}^{-3})$ | $V_o(V)$ |

|---------------|------------|---------------------------|----------|

| Ge            | 0.7        | $2.40 \times 10^{13}$     | 0.37     |

| Si            | 1.1        | $1.0 \times 10^{10}$      | 0.78     |

| GaAs          | 1.4        | $2.1 \times 10^6$         | 1.21     |

Using

$$V_o = \left(\frac{kT}{e}\right) \ln \left(\frac{N_d N_a}{n_i^2}\right)$$

for Si with  $N_d = 10^{17}$  cm<sup>-3</sup> and  $N_a = 10^{16}$  cm<sup>-3</sup>, kT/e = 0.0259 V at 300 K, and  $n_i = 1.0 \times 10^{10}$  cm<sup>-3</sup>, we obtain

$$V_o = (0.0259 \text{ V}) \ln \left[ \frac{(10^{17})(10^{16})}{(1.0 \times 10^{10})^2} \right] = 0.775 \text{ V}$$

The results for all three semiconductors are summarized in the last column of the table in this example.

### **EXAMPLE 6.2**

**THE**  $p^+n$  **JUNCTION** Consider a  $p^+n$  junction, which has a heavily doped p-side relative to the n-side, that is,  $N_a \gg N_d$ . Since the amount of charge Q on both sides of the metallurgical junction must be the same (so that the junction is overall neutral)

$$Q = e N_a W_p = e N_d W_n$$

it is clear that the depletion region essentially extends into the *n*-side. According to Equation 6.7, when  $N_d \ll N_a$ , the width is

$$W_o = \left[\frac{2\varepsilon V_o}{eN_d}\right]^{1/2}$$

What is the depletion width for a pn junction Si diode that has been doped with  $10^{18}$  acceptor atoms cm<sup>-3</sup> on the p-side and  $10^{16}$  donor atoms cm<sup>-3</sup> on the n-side?

#### SOLUTION

To apply the above equation for  $W_o$ , we need the built-in potential, which is

$$V_o = \left(\frac{kT}{e}\right) \ln\left(\frac{N_d N_a}{n_i^2}\right) = (0.0259 \text{ V}) \ln\left[\frac{(10^{16})(10^{18})}{(1.0 \times 10^{10})^2}\right] = 0.835 \text{ V}$$

Then with  $N_d = 10^{16}$  cm<sup>-3</sup>, that is,  $10^{22}$  m<sup>-3</sup>,  $V_o = 0.835$  V, and  $\varepsilon_r = 11.9$  in the equation for  $W_o$

$$W_o = \left[\frac{2\varepsilon V_o}{\varepsilon N_d}\right]^{1/2} = \left[\frac{2(11.9)(8.85 \times 10^{-12})(0.835)}{(1.6 \times 10^{-19})(10^{22})}\right]^{1/2}$$

$$= 3.32 \times 10^{-7} \,\text{m} \qquad \text{or} \qquad 0.33 \,\,\text{µm}$$

Nearly all of this region (99 percent of it) is on the n-side.

**BUILT-IN VOLTAGE** There is a rigorous derivation of the built-in voltage across a pn junction. Inasmuch as in equilibrium there is no net current through the pn junction, drift of holes due to the built-in field  $\mathcal{L}(x)$  must be just balanced by their diffusion due to the concentration gradient dp/dx. We can thus set the total electron and hole current densities (drift + diffusion) through the depletion region to zero. Considering holes alone, from Equation 5.38,

$$J_{\text{hole}}(x) = ep(x)\mu_h \mathcal{E}(x) - eD_h \frac{dp}{dx} = 0$$

The electric field is defined by  $\mathcal{E} = -dV/dx$ , so substituting we find,

$$-ep\mu_h dV - eD_h dp = 0$$

We can now use the Einstein relation  $D_h/\mu_h = kT/e$  to get

$$-ep\,dV - kT\,dp = 0$$

We can integrate this equation. According to Figure 6.1, in the p-side,  $p = p_{po}$ , V = 0, and in the n-side,  $p = p_{no}$ ,  $V = V_o$ , thus,

$$\int_{0}^{V_{o}} dV + \frac{kT}{e} \int_{p_{po}}^{P_{\infty}} \frac{dp}{p} = 0$$

$$V_{o} + \frac{kT}{e} [\ln(p_{no}) - \ln(p_{po})] = 0$$

$$V_{o} = \frac{kT}{e} \ln\left(\frac{p_{po}}{p_{no}}\right)$$

that is,

giving

which is the same as Equation 6.5b and hence leads to Equation 6.6.

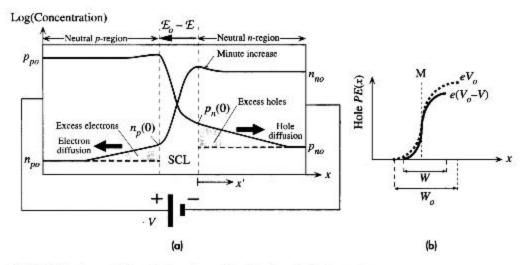

## 6.1.2 FORWARD BIAS: DIFFUSION CURRENT

Consider what happens when a battery is connected across a pn junction so that the positive terminal of the battery is attached to the p-side and the negative terminal to the n-side. Suppose that the applied voltage is V. It is apparent that the negative polarity of the supply will reduce the potential barrier  $V_o$  by V, as shown in Figure 6.2a. The reason for this is that the bulk regions outside the depletion width have high conductivities due to plenty of majority carriers in the bulk, in comparison with the depletion region in which there are mainly immobile ions. Thus, the applied voltage drops mostly across the depletion width W. Consequently, V directly opposes Vo and the potential barrier against diffusion is reduced to  $(V_o - V)$ , as depicted in Figure 6.2b. This has drastic consequences because the probability that a hole will surmount this potential barrier and diffuse to the right now becomes proportional to  $\exp[-e(V_n - V)/kT]$ . In other words, the applied voltage effectively reduces the built-in potential and hence the built-in field, which acts against diffusion. Consequently many holes can now diffuse across the depletion region and enter the n-side. This results in the injection of excess minority carriers, holes, into the n-region. Similarly, excess electrons can now diffuse toward the p-side and enter this region and thereby become injected minority carriers.

**EXAMPLE 6.3**

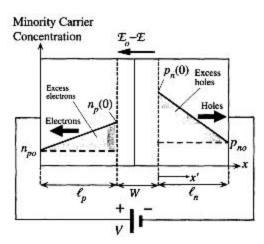

Figure 6.2 Forward-biased on junction and the injection of minority carriers.

- (a) Carrier concentration profiles across the device under forward bias.

- (b) The hole potential energy with and without an applied bias. W is the width of the SCL with forward bias.

#### The hole concentration

$$p_n(0) = p_n(x'=0)$$

just outside the depletion region at x' = 0 (x' is measured from  $W_n$ ) is due to the excess of holes diffusing as a result of the reduction in the built-in potential barrier. This concentration  $p_n(0)$  is determined by the probability of surmounting the new potential energy barrier  $e(V_n - V)$ ,

$$p_n(0) = p_{po} \exp\left[-\frac{e(V_o - V)}{kT}\right]$$

[6.8]

This follows directly from the Boltzmann equation, by virtue of the hole potential energy rising by  $e(V_o - V)$  from  $x = -W_p$  to  $x = W_n$ , as indicated in Figure 6.2b, and at the same time the hole concentration falling from  $p_{po}$  to  $p_n(0)$ . By dividing Equation 6.8 by Equation 6.5b, we obtain the effect of the applied voltage directly, which shows how the voltage V determines the amount of excess holes diffusing and arriving at the n-region. Equation 6.8 divided by Equation 6.5b is

Law of the junction

$$p_n(0) = p_{no} \exp\left(\frac{eV}{kT}\right)$$

[6.9]

which is called the **law of the junction.** Equation 6.9 is an important equation that we will use again in dealing with pn junction devices. It describes the effect of the applied voltage V on the injected minority carrier concentration just outside the depletion region  $p_n(0)$ . Obviously, with no applied voltage, V = 0 and  $p_n(0) = p_{no}$ , which is exactly what we expect.

Injected holes diffuse in the n-region and eventually recombine with electrons in this region as there are many electrons in the n-side. Those electrons lost by recombination are readily replenished by the negative terminal of the battery connected to this side. The current due to holes diffusing in the n-region can be sustained because more holes can be supplied by the p-region, which itself can be replenished by the positive terminal of the battery.

Electrons are similarly injected from the *n*-side to the *p*-side. The electron concentration  $n_p(0)$  just outside the depletion region at  $x = -W_p$  is given by the equivalent of Equation 6.9 for electrons, that is,

$$n_p(0) = n_{po} \exp\left(\frac{eV}{kT}\right)$$

[6.10]

In the p-region, the injected electrons diffuse toward the positive terminal looking to be collected. As they diffuse they recombine with some of the many holes in this region. Those holes lost by recombination can be readily replenished by the positive terminal of the battery connected to this side. The current due to the diffusion of electrons in the p-side can be maintained by the supply of electrons from the n-side, which itself can be replenished by the negative terminal of the battery. It is apparent that an electric current can be maintained through a pn junction under forward bias, and that the current flow, surprisingly, seems to be due to the **diffusion of minority carriers**. There is, however, some drift of majority carriers as well.

If the lengths of the p- and n-regions are longer than the minority carrier diffusion lengths, then we will be justified to expect the hole concentration  $p_n(x')$  on the n-side to fall exponentially toward the thermal equilibrium value  $p_{no}$ , that is,

$$\Delta p_n(x') = \Delta p_n(0) \exp\left(-\frac{x'}{L_k}\right)$$

[6.11]

where

$$\Delta p_n(x') = p_n(x') - p_{no}$$

is the excess carrier distribution and  $L_h$  is the **hole diffusion length**, defined by  $L_h = \sqrt{D_h \tau_h}$  in which  $\tau_h$  is the mean hole recombination lifetime (minority carrier lifetime) in the *n*-region. We base Equation 6.11 on our experience with the minority carrier injection in Chapter 5.<sup>3</sup>

The hole diffusion current density  $J_{D,hole}$  is therefore

$$J_{D,\text{hole}} = -eD_h \frac{dp_n(x')}{dx'} = -eD_h \frac{d\Delta p_n(x')}{dx'}$$

that is,

$$J_{D.\text{hole}} = \left(\frac{eD_h}{L_h}\right) \Delta p_n(0) \exp\left(-\frac{x'}{L_h}\right)$$

Law of the junction

Excess minority carrier profile

Excess minority carrier concentration

<sup>&</sup>lt;sup>3</sup>This is simply the solution of the continuity equation in the absence of an electric field, which is discussed in Chapter 5. Equation 6.11 is identical to Equation 5.48.

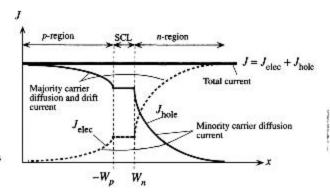

Figure 6.3 The total current anywhere in the device is constant. Just outside the depletion region, it is due to the diffusion of minority carriers.

Although this equation shows that the hole diffusion current depends on location, the total current at any location is the sum of hole and electron contributions, which is independent of x, as indicated in Figure 6.3. The decrease in the minority carrier diffusion current with x' is made up by the increase in the current due to the drift of the majority carriers, as schematically shown in Figure 6.3. The field in the neutral region is not totally zero but a small value, just sufficient to drift the huge number of majority carriers there.

At x' = 0, just outside the depletion region, the hole diffusion current is

$$J_{D,\mathrm{hole}} = \left(\frac{eD_h}{L_h}\right) \Delta p_n(0)$$

We can now use the law of the junction to substitute for  $\Delta p_n(0)$  in terms of the applied voltage V. Writing

$$\Delta p_n(0) = p_n(0) - p_{no} = p_{no} \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right]$$

and substituting in  $J_{D,hole}$ , we get

$$J_{D,\text{hole}} = \left(\frac{eD_h p_{no}}{L_h}\right) \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

Thermal equilibrium hole concentration  $p_{no}$  is related to the donor concentration by

$$p_{no} = \frac{n_i^2}{n_{no}} = \frac{n_i^2}{N_d}$$

Thus,

$$J_{D,\mathrm{hole}} = \left(\frac{eD_h n_i^2}{L_h N_d}\right) \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

There is a similar expression for the electron diffusion current density  $J_{D,\text{elec}}$  in the p-region. We will assume (quite reasonably) that the electron and hole currents do not change across the depletion region because, in general, the width of this region is narrow (reality is not quite like the schematic sketches in Figures 6.2 and 6.3). The electron

Hole diffusion current in n-side

Hole diffusion current in n-side current at  $x = -W_p$  is the same as that at  $x = W_n$ . The total current density is then simply given by  $J_{D,\text{hole}} + J_{D,\text{elec}}$ , that is,

$$J = \left(\frac{eD_h}{L_h N_d} + \frac{eD_e}{L_e N_a}\right) n_i^2 \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

OF

$$J = J_{so} \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right]$$

[6.12]

This is the familiar diode equation with

$$J_{so} = \left[ \left( \frac{eD_h}{L_h N_d} \right) + \left( \frac{eD_e}{L_e N_a} \right) \right] n_i^2$$

Reverse saturation current

Ideal diode

(Shockley) equation

It is frequently called the **Shockley equation.** The constant  $J_{so}$  depends not only on the doping,  $N_d$  and  $N_a$ , but also on the material via  $n_l$ ,  $D_h$ ,  $D_e$ ,  $L_h$ , and  $L_e$ . It is known as the **reverse saturation current density**, as explained below. Writing

$$n_i^2 = (N_c N_v) \exp\left(-\frac{eV_g}{kT}\right)$$

Intrinsic concentration

where  $V_g = E_g/e$  is the bandgap energy expressed in volts, we can write Equation 6.12 as

$$J = \left(\frac{eD_h}{L_h N_d} + \frac{eD_e}{L_e N_d}\right) \left[ (N_c N_v) \exp\left(-\frac{eV_g}{kT}\right) \right] \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right]$$

that is,

$$J = J_1 \exp\left(-\frac{eV_g}{kT}\right) \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

or

$$J = J_1 \exp \left[ \frac{e(V - V_g)}{kT} \right]$$

for  $\frac{eV}{kT} \gg 1$  [6.13] Diode current and bandgap energy

where

$$J_1 = \left(\frac{eD_h}{L_h N_d} + \frac{eD_e}{L_e N_a}\right) (N_c N_v)$$

is a new constant.

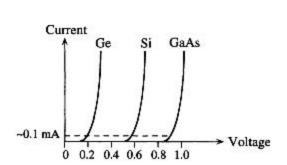

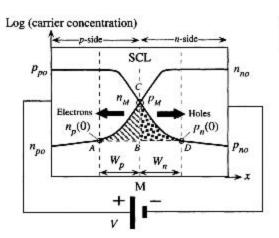

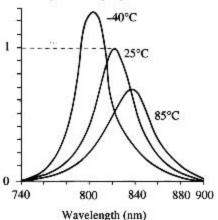

The significance of Equation 6.13 is that it reflects the dependence of I-V characteristics on the bandgap (via  $V_g$ ), as displayed in Figure 6.4 for the three important semiconductors, Ge, Si, and GaAs. Notice that the voltage across the pn junction for an appreciable current of say  $\sim 0.1$  mA is about 0.2 V for Ge, 0.6 V for Si, and 0.9 V for GaAs.

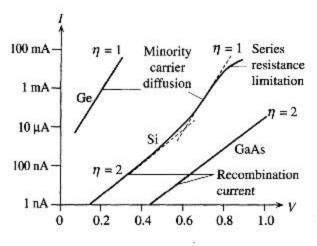

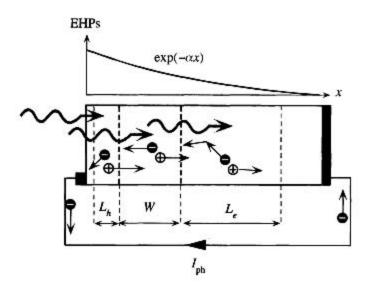

The diode equation, Equation 6.12, was derived by assuming that the lengths of the p and n regions outside the depletion region are long in comparison with the diffusion lengths  $L_h$  and  $L_g$ . Suppose that  $\ell_p$  is the length of the p-side outside the depletion region

Figure 6.4 Schematic sketch of the LV characteristics of Ge, Si, and GaAs pn junctions.

Figure 6.5 Minority carrier injection and diffusion in a short diade.

and  $\ell_n$  is that of the *n*-side outside the depletion region. If  $\ell_p$  and  $\ell_n$  are shorter than the diffusion lengths  $L_e$  and  $L_h$ , respectively, then we have what is called a **short diode** and consequently the minority carrier distribution profiles fall almost linearly with distance from the depletion region, as depicted in Figure 6.5. This can be readily proved by solving the continuity equation, but an intuitive explanation makes it clear. At x'=0, the minority carrier concentration is determined by the law of the junction, whereas at the battery terminal there can be no excess carriers as the battery will simply collect these. Since the length of the neutral region is shorter than the diffusion length, there are practically no holes lost by recombination, and therefore the hole flow is expected to be uniform across  $\ell_n$ . This can be so only if the driving force for diffusion, the concentration gradient, is linear.

The excess minority carrier gradient is

$$\frac{d\Delta p_n(x')}{dx'} = -\frac{[p_n(0) - p_{no}]}{\ell_n}$$

The current density  $J_{D,hole}$  due to the injection and diffusion of holes in the n-region as a result of forward bias is

$$J_{D,\text{hole}} = -eD_h \frac{d\Delta p_n(x')}{dx'} = eD_h \frac{[p_n(0) - p_{no}]}{\ell_n}$$

We can now use the law of the junction

$$p_n(0) = p_{no} \exp\left(\frac{eV}{kT}\right)$$

for  $p_n(0)$  in the above equation and also obtain a similar equation for electrons diffusing in the p-region and then sum the two for the total current J,

$$J = \left(\frac{eD_h}{\ell_n N_d} + \frac{eD_e}{\ell_p N_a}\right) n_i^2 \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

[6.14]

It is clear that this expression is identical to that of a long diode, that is, Equation 6.12, if in the latter we replace the diffusion lengths  $L_h$  and  $L_e$  by the lengths  $\ell_n$  and  $\ell_p$  of the n- and p-regions outside the SCL.

## 6.1.3 FORWARD BIAS: RECOMBINATION AND TOTAL CURRENT

So far we have assumed that, under a forward bias, the minority carriers diffusing and recombining in the neutral regions are supplied by the external current. However, some of the minority carriers will recombine in the depletion region. The external current must therefore also supply the carriers lost in the recombination process in the SCL. Consider for simplicity a symmetrical pn junction as in Figure 6.6 under forward bias. At the metallurgical junction at the center C, the hole and electron concentrations are  $p_M$  and  $n_M$  and are equal. We can find the SCL recombination current by considering electrons recombining in the p-side in  $W_p$  and holes recombining in the n-side in  $W_n$  as shown by the shaded areas ABC and BCD, respectively, in Figure 6.6. Suppose that the mean hole recombination time in  $W_n$  is  $\tau_h$  and mean electron recombination time in  $W_p$  is  $\tau_e$ . The rate at which the electrons in ABC are recombining is the area ABC (nearly all injected electrons) divided by  $\tau_e$ . The electrons are replenished by the diode current. Similarly, the rate at which holes in BCD are recombining is the area BCD divided by  $\tau_h$ . Thus, the recombination current density is

$$J_{\text{recom}} = \frac{eABC}{\tau_e} + \frac{eBCD}{\tau_h}$$

We can evaluate the areas ABC and BCD by taking them as triangles, ABC  $\approx \frac{1}{5}W_p n_M$ , etc., so that

$$J_{\text{recom}} pprox rac{erac{1}{2}W_p n_M}{ au_e} + rac{erac{1}{2}W_n p_M}{ au_h}$$

Under steady-state and equilibrium conditions, assuming a nondegenerate semiconductor, we can use Boltzmann statistics to relate these concentrations to the potential

Figure 6.6 Forward-biased pn junction and the injection of carriers and their recombination in SCL.

energy. At A, the potential is zero and at M it is  $\frac{1}{2}e(V_o - V)$ , so

$$\frac{p_M}{p_{po}} = \exp\left[-\frac{e(V_o - V)}{2kT}\right]$$

Since  $V_o$  depends on dopant concentrations and  $n_i$  as in Equation 6.6 and further  $p_{po} = N_a$ , we can simplify this equation to

$$p_M = n_i \exp\left(\frac{eV}{2kT}\right)$$

This means that the recombination current for V > kT/e is given by

Recombination current

$$J_{\text{recom}} = \frac{en_i}{2} \left( \frac{W_p}{\tau_e} + \frac{W_n}{\tau_h} \right) \exp\left( \frac{eV}{2kT} \right)$$

[6.15]

From a better quantitative analysis, the expression for the recombination current can be shown to be<sup>4</sup>

Recombination current

$$J_{\text{recom}} = J_{ro} \left[ \exp(eV/2kT) - 1 \right]$$

[6.16]

where  $J_m$  is the preexponential constant in Equation 6.15.

Equation 6.15 is the current that supplies the carriers that recombine in the depletion region. The total current into the diode will supply carriers for minority carrier diffusion in the neutral regions and recombination in the space charge layer, so it will be the sum of Equations 6.12 and 6.15.

Total diode current = diffusion + recombination

$$J = J_{so} \exp\left(\frac{eV}{kT}\right) + J_{ro} \exp\left(\frac{eV}{2kT}\right) \qquad \left(V > \frac{kT}{e}\right)$$

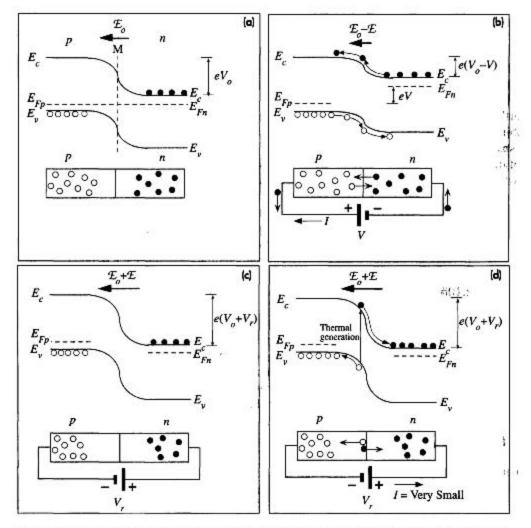

This expression is often lumped into a single exponential as

The diode equation

$$J = J_o \exp\left(\frac{eV}{nkT}\right) \qquad \left(V > \frac{kT}{e}\right)$$

[6.17]

where  $J_o$  is a new constant and  $\eta$  is an **ideality factor**, which is 1 when the current is due to minority carrier diffusion in the neutral regions and 2 when it is due to recombination in the space charge layer. Figure 6.7 shows typical expected I-V characteristics of pn junction Ge, Si, and GaAs diodes. At the highest currents, invariably, the bulk resistances of the neutral regions limit the current (why?). For Ge diodes, typically  $\eta=1$  and the overall I-V characteristics are due to minority carrier diffusion. In the case of GaAs,  $\eta\approx 2$  and the current is limited by recombination in the space charge layer. For Si, typically,  $\eta$  changes from 2 to 1 as the current increases, indicating that both processes play an important role. In the case of heavily doped Si diodes, heavy doping leads to short minority carrier recombination times and the current is controlled by recombination in the space charge layer so that the  $\eta=2$  region extends all the way to the onset of bulk resistance limitation.

<sup>1 4</sup> This is generally proved in advanced texts.

Figure 6.7 Schematic sketch of typical I-V characteristics of Ge, Si, and GaAs pn junctions as log(I) versus V.

The slope indicates e/(ηkT).

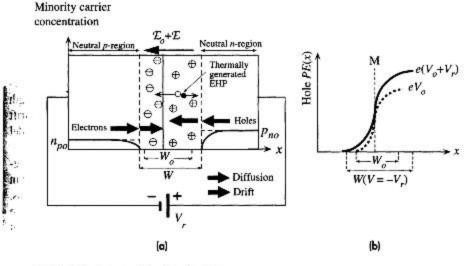

Figure 6.8 Reverse-biased pn junction.

- (a) Minority carrier profiles and the origin of the reverse current.

- (b) Hole PE across the junction under reverse bias.

## 6.1.4 REVERSE BIAS

When a pn junction is reverse-biased, as shown in Figure 6.8a, the applied voltage, as before, drops mainly across the depletion region, that is, the space charge layer (SCL), which becomes wider. The negative terminal will attract the holes in the p-side to move away from the SCL, which results in more exposed negative acceptor ions and thus a wider SCL. Similarly, the positive terminal will attract electrons away from the SCL, which exposes more positively charged donors. The depletion width on the n-side also widens. The movement of electrons in the n-region toward the positive battery

terminal cannot be sustained because there is no electron supply to this *n*-side. The *p*-side cannot supply electrons to the *n*-side because it has almost none. However, there is a small reverse current due to two causes.

The applied voltage increases the built-in potential barrier, as depicted in Figure 6.8b. The electric field in the SCL is larger than the built-in internal field  $\mathcal{E}_o$ . The small number of holes on the *n*-side near the SCL become extracted and swept by the field across the SCL over to the *p*-side. This small current can be maintained by the diffusion of holes from the *n*-side bulk to the SCL boundary.

Assume that the reverse bias  $V_r > kT/e = 25$  mV. The hole concentration  $p_n(0)$  just outside the SCL is nearly zero by the law of the junction, Equation 6.9, whereas the hole concentration in the bulk (or near the negative terminal) is the equilibrium concentration  $p_{no}$ , which is small. There is therefore a small concentration gradient and hence a small hole diffusion current toward the SCL as shown in Figure 6.8a. Similarly, there is a small electron diffusion current from bulk p-side to the SCL. Within the SCL, these carriers are drifted by the field. This minority carrier diffusion current is essentially the Shockley model. The reverse current is given by Equation 6.12 with a negative voltage which leads to a diode current density of  $-J_{so}$  called the reverse saturation current density. The value of  $J_{so}$ depends only on the material via  $n_i$ ,  $\mu_h$ ,  $\mu_e$ , depant concentrations, but not on the voltage  $(V_r > kT/e)$ . Furthermore, as  $J_{so}$  depends on  $n_i^2$ , it is strongly temperature dependent. In some books it is stated that the causes of reverse current are the thermal generation of minority carriers in the neutral region within a diffusion length to the SCL, the diffusion of these carriers to the SCL, and their subsequent drift through the SCL. This description, in essence, is identical to the Shockley model we just described.

The thermal generation of electron-hole pairs (EHPs) in the SCL, as shown in Figure 6.8a, can also contribute to the observed reverse current since the internal field in this layer will separate the electron and hole and drift them toward the neutral regions. This drift will result in an external current in addition to the reverse current due to the diffusion of minority carriers. The theoretical evaluation of SCL generation current involves an in-depth knowledge of the charge carrier generation processes via recombination centers, which is discussed in advanced texts. Suppose that  $\tau_g$  is the mean time to generate an electron-hole pair by virtue of the thermal vibrations of the lattice;  $\tau_g$  is also called the mean thermal generation time. Given  $\tau_g$ , the rate of thermal generation per unit volume must be  $n_i/\tau_g$  because it takes on average  $\tau_g$  seconds to create  $n_i$  number of EHPs per unit volume. Furthermore, since WA, where A is the cross-sectional area, is the volume of the depletion region, the rate of EHP, or charge carrier, generation is  $(AWn_i)/\tau_g$ . Both holes and electrons drift in the SCL each contributing equally to the current. The observed current density must be  $e(Wn_i)/\tau_g$ . Therefore the reverse current density component due to thermal generation of EHPs within the SCL should be given by

EHP thermal generation in SCL

$$J_{\rm gen} = \frac{eWn_i}{\tau_e} \tag{6.18}$$

The reverse bias widens the width W of the depletion layer and hence increases  $J_{\text{gen}}$ . The total reverse current density  $J_{\text{rev}}$  is the sum of the diffusion and generation

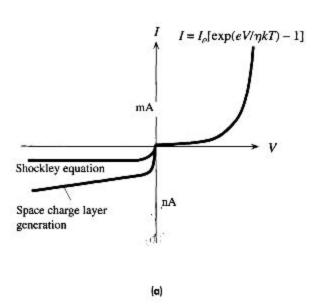

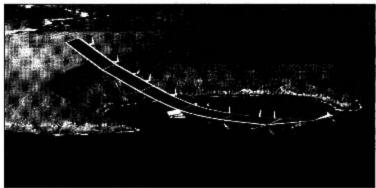

Figure 6.9

(a) Forward and reverse I-V characteristics of a pn junction (the positive and negative current axes have different scales and hence the discontinuity at the origin).

(b) Reverse diode current in a Ge pn junction as a function of temperature in a  $\ln(l_{rev})$  versus 1/T plot. Above 238 K,  $l_{rev}$  is controlled by  $n_i^2$ , and below 238 K, it is controlled by  $n_i$ . The vertical axis is a logarithmic scale with actual current values.

SOURCE: (b) From D. Scansen and S. O. Kasap, Cnd. J. Physics, 70, 1070, 1992.

components,

$$J_{\text{rev}} = \left(\frac{eD_h}{L_h N_d} + \frac{eD_e}{L_e N_a}\right) n_i^2 + \frac{eW n_i}{\tau_e}$$

[6.19] Total reverse current

which is shown schematically in Figure 6.9a. The thermal generation component  $J_{\text{gen}}$  in Equation 6.18 increases with reverse bias  $V_r$  because the SCL width W increases with  $V_r$ .

The terms in the reverse current in Equation 6.19 are predominantly controlled by  $n_i^2$  and  $n_i$ . Their relative importance depends not only on the semiconductor properties but also on the temperature since  $n_i \propto \exp(-E_g/2kT)$ . Figure 6.9b shows the reverse current  $I_{\text{rev}}$  in dark in a Ge pn junction (a photodiode) plotted as  $\ln(I_{\text{rev}})$  versus 1/T to highlight the two different processes in Equation 6.19. The measurements in Figure 6.9b show that above 238 K,  $I_{\text{rev}}$  is controlled by  $n_i^2$  because the slope of  $\ln(I_{\text{rev}})$  versus 1/T yields an  $E_g$  of approximately 0.63 eV, close to the expected  $E_g$  of about 0.66 eV in Ge. Below 238 K,  $I_{\text{rev}}$  is controlled by  $n_i$  because the slope of  $\ln(I_{\text{rev}})$  versus 1/T is equivalent to  $E_g/2$  of approximately 0.33 eV. In this range, the reverse current is due to EHP generation in the SCL via defects and impurities (recombination centers).

## **EXAMPLE 6.4**

**FORWARD- AND REVERSE-BIASED SI DIODE** An abrupt Si  $p^+n$  junction diode has a cross-sectional area of 1 mm<sup>2</sup>, an acceptor concentration of  $5 \times 10^{18}$  boron atoms cm<sup>-3</sup> on the p-side, and a donor concentration of  $10^{16}$  arsenic atoms cm<sup>-3</sup> on the n-side. The lifetime of holes in the n-region is 417 ns, whereas that of electrons in the p-region is 5 ns due to a greater concentration of impurities (recombination centers) on that side. Mean thermal generation lifetime ( $\tau_g$ ) is about 1  $\mu$ s. The lengths of the p- and n-regions are 5 and 100 microns, respectively.

- Calculate the minority diffusion lengths and determine what type of a diode this is.

- b. What is the built-in potential across the junction?

- c. What is the current when there is a forward bias of 0.6 V across the diode at 27 °C? Assume that the current is by minority carrier diffusion.

- d. Estimate the forward current at 100 °C when the voltage across the diode remains at 0.6 V. Assume that the temperature dependence of  $n_i$  dominates over those of D, L, and  $\mu$ .

- e. What is the reverse current when the diode is reverse-biased by a voltage  $V_r = 5 \text{ V}$ ?

#### SOLUTION

The general expression for the diffusion length is  $L = \sqrt{D\tau}$  where D is the diffusion coefficient and  $\tau$  is the carrier lifetime. D is related to the carrier mobility  $\mu$  via the Einstein relationship  $D/\mu = kT/e$ . We therefore need to know  $\mu$  to calculate D and hence L. Electrons diffuse in the p-region and holes in the n-region, so we need  $\mu_e$  in the presence of  $N_a$  acceptors and  $\mu_h$  in the presence of  $N_d$  donors. From the drift mobility,  $\mu$  versus dopant concentration in Figure 5.19, we have the following:

With

$$N_a = 5 \times 10^{18} \text{ cm}^{-3}$$

$\mu_s \approx 120 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$

With  $N_d = 10^{16} \text{ cm}^{-3}$   $\mu_k \approx 440 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$

Thus

$$D_e = \frac{kT\mu_e}{e} \approx (0.0259 \text{ V})(120 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}) = 3.10 \text{ cm}^2 \text{ s}^{-1}$$

$$D_h = \frac{kT\mu_h}{e} \approx (0.0259 \text{ V})(440 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}) = 11.39 \text{ cm}^2 \text{ s}^{-1}$$

Diffusion lengths are

$$L_e = \sqrt{D_e \tau_e} = \sqrt{[(3.10 \text{ cm}^2 \text{ s}^{-1})(5 \times 10^{-9} \text{ s})]}$$

$$= 1.2 \times 10^{-4} \text{ cm} \quad \text{or} \quad 1.2 \text{ } \mu\text{m} < 5 \text{ } \mu\text{m}$$

$$L_h = \sqrt{D_h \tau_h} = \sqrt{[(11.39 \text{ cm}^2 \text{ s}^{-1})(417 \times 10^{-9} \text{ s})]}$$

$$= 21.8 \times 10^{-4} \text{ cm} \quad \text{or} \quad 21.8 \text{ } \mu\text{m} < 100 \text{ } \mu\text{m}$$

We therefore have a long diode. The built-in potential is

$$V_o = \left(\frac{kT}{e}\right) \ln \left(\frac{N_d N_a}{n_t^2}\right) = (0.0259 \text{ V}) \ln \left[\frac{(5 \times 10^{18} \times 10^{16})}{(1.0 \times 10^{10})^2}\right] = 0.877 \text{ V}$$

To calculate the forward current when V = 0.6 V, we need to evaluate both the diffusion and recombination components to the current. It is likely that the diffusion component will exceed the recombination component at this forward bias (this can be easily verified). Assuming

that the forward current is due to minority carrier diffusion in neutral regions,

$$I = I_{so} \left[ \exp \left( \frac{eV}{kT} \right) - 1 \right] \approx I_{so} \exp \left( \frac{eV}{kT} \right)$$

for  $V \gg \frac{kT}{e}$  (= 0.0259 V)

where

$$I_{so} = AJ_{so} = Aen_i^2 \left[ \left( \frac{D_h}{L_h N_d} \right) + \left( \frac{D_e}{L_e N_o} \right) \right] \approx \frac{Aen_i^2 D_h}{L_h N_d}$$

as  $N_a \gg N_d$ . In other words, the current is mainly due to the diffusion of holes in the *n*-region. Thus,

$$I_{so} = \frac{(0.01 \text{ cm}^2)(1.6 \times 10^{-19} \text{ C})(1.0 \times 10^{10} \text{ cm}^{-3})^2(11.39 \text{ cm}^2 \text{ s}^{-1})}{(21.8 \times 10^{-4} \text{ cm})(10^{16} \text{ cm}^{-3})}$$

= 8.36 × 10<sup>-14</sup> A or 0.084 pA

Then the diode current is

$$I \approx I_{xo} \exp\left(\frac{eV}{kT}\right) = (8.36 \times 10^{-14} \text{ A}) \exp\left[\frac{(0.6 \text{ V})}{(0.0259 \text{ V})}\right]$$

=  $0.96 \times 10^{-3} \text{ A}$  or  $0.96 \text{ mA}$

We note that when a forward bias of 0.6 V is applied, the built-in potential is reduced from 0.877 V to 0.256 V, which encourages minority carrier injection, that is, diffusion of holes from p- to n-side and electrons from n- to p-side. To find the current at 100 °C, first we assume that  $I_{so} \propto n_i^2$ . Then at T = 273 + 100 = 373 K,  $n_i \approx 1.0 \times 10^{12}$  cm<sup>-3</sup> (approximately from  $n_i$  versus 1/T graph in Figure 5.16), so

$$I_{so}(373 \text{ K}) \approx I_{so}(300 \text{ K}) \left[ \frac{n_1(373 \text{ K})}{n_1(300 \text{ K})} \right]^2$$

$\approx (8.36 \times 10^{-14}) \left( \frac{1.0 \times 10^{12}}{1.0 \times 10^{10}} \right)^2 = 8.36 \times 10^{-10} \text{A} \quad \text{or} \quad 0.836 \text{ nA}$

At 100 °C, the forward current with 0.6 V across the diode is

$$I = I_{so} \exp\left(\frac{eV}{kT}\right) = (8.36 \times 10^{-10} \text{ A}) \exp\left[\frac{(0.6 \text{ V})(300 \text{ K})}{(0.0259 \text{ V})(373 \text{ K})}\right] = 0.10 \text{ A}$$

When a reverse bias of  $V_r$  is applied, the potential difference across the depletion region becomes  $V_o + V_r$  and the width W of the depletion region is

$$W = \left[\frac{2\varepsilon(V_o + V_r)}{eN_d}\right]^{1/2} = \left[\frac{2(11.9)(8.85 \times 10^{-12})(0.877 + 5)}{(1.6 \times 10^{-19})(10^{22})}\right]^{1/2}$$

$$= 0.88 \times 10^{-6} \text{ m} \qquad \text{or} \qquad 0.88 \text{ } \mu\text{m}$$

The thermal generation current with  $V_r = 5 \text{ V}$  is

$$I_{\text{gen}} = \frac{eAWn_i}{\tau_g} = \frac{(1.6 \times 10^{-19} \text{ C})(0.01 \text{ cm}^2)(0.88 \times 10^{-4} \text{ cm})(1.0 \times 10^{10} \text{ cm}^{-3})}{(10^{-6} \text{ s})}$$

$$= 1.41 \times 10^{-9} \text{ A} \qquad \text{or} \qquad 1.4 \text{ nA}$$

This thermal generation current is much greater than the reverse saturation current  $I_{10} (= 0.084 \text{ pA})$ . The reverse current is therefore dominated by  $I_{gen}$  and it is 1.4 nA.

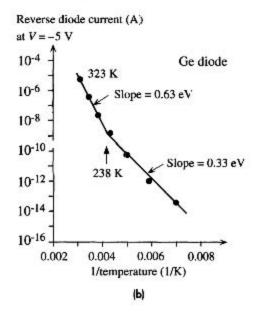

## 6.2 pn JUNCTION BAND DIAGRAM

## 6.2.1 OPEN CIRCUIT

Figure 6.10a shows the energy band diagrams for a p-type and an n-type semiconductor of the same material (same  $E_g$ ) when the semiconductors are isolated from each other. In the p-type material the Fermi level  $E_{Fp}$  is  $\Phi_p$  below the vacuum level and is close to  $E_v$ . In the n-type material the Fermi level  $E_{Fn}$  is  $\Phi_n$  below the vacuum level and is close to  $E_c$ . The separation  $E_c - E_{Fn}$  determines the electron concentration  $n_{no}$  in the n-type and  $E_{Fp} - E_v$  determines the hole concentration  $p_{po}$ , in the p-type semi-conductor under thermal equilibrium conditions.

An important property of the Fermi energy  $E_F$  is that in a system in equilibrium, the Fermi level must be spatially continuous. A difference in Fermi levels  $\Delta E_F$  is equivalent to electrical work eV, which is either done on the system or extracted from the system. When the two semiconductors are brought together, as in Figure 6.10b, the Fermi level must be uniform through the two materials and the junction at M, which marks the position of the metallurgical junction. Far away from M, in the bulk of the n-type semiconductor, we should still have an n-type semiconductor and  $E_c - E_{Fn}$  should be the same as before. Similarly,  $E_{Fp} - E_v$  far away from M inside the p-type material should also be the same as before. These features are sketched in Figure 6.10b keeping  $E_{Fp}$  and  $E_{Fn}$  the same through the whole system and, of course, keeping the bandgap  $E_c - E_v$  the same. Clearly, to draw the energy band diagram, we have to bend the bands  $E_c$  and  $E_v$  around the junction at M because  $E_c$  on the n-side is close to  $E_{Fn}$  whereas on the p-side it is far away from  $E_{Fp}$ . How do bands bend and what does it mean?

Figure 6.10

(a) Two isolated p- and n-type semiconductors (same material).

(b) A pri junction band diagram when the two semiconductors are in contact. The Fermi level must be uniform in equilibrium. The metallurgical junction is at M. The region around M contains the space charge layer (SCL). On the reside of M, SCL has the exposed positively charged donors, whereas on the p-side it has the exposed negatively charged acceptors.

As soon as the two semiconductors are brought together to form the junction, electrons diffuse from the n-side to the p-side and as they do so they deplete the n-side near the junction. Thus  $E_c$  must move away from  $E_{Fn}$  toward M, which is exactly what is sketched in Figure 6.10b. Holes diffuse from the p-side to the n-side and the loss of holes in the p-type material near the junction means that  $E_v$  moves away from  $E_{Fp}$  toward M, which is also in the figure.

Furthermore, as electrons and holes diffuse toward each other, most of them recombine and disappear around M, which leads to the formation of a depletion region or the space charge layer, as we saw in Figure 6.1. The electrostatic potential energy (PE) of the electron decreases from 0 inside the p-region to  $-eV_o$  inside the n-region, as shown in Figure 6.1g. The total energy of the electron must therefore decrease going from the p- to the n-region by an amount  $eV_o$ . In other words, the electron in the n-side at  $E_c$  must overcome a PE barrier to go over to  $E_c$  in the p-side. This PE barrier is  $eV_o$ , where  $V_o$  is the built-in potential that we evaluated in Section 6.1. Band bending around M therefore accounts not only for the variation of electron and hole concentrations in this region but also for the effect of the built-in potential (and hence the built-in field as the two are related).

In Figure 6.10b we have also schematically sketched in the positive donor (at  $E_d$ ) and the negative acceptor (at  $E_a$ ) charges in the SCL around M to emphasize that there are exposed charges near M. These charges are, of course, immobile and, generally, they are not shown in band diagrams. It should be noted that in the SCL region, marked as  $W_o$ , the Fermi level is close to neither  $E_c$  nor  $E_v$ , compared with the bulk semiconductor regions. This means that both n and p in this zone are much less than their bulk values  $n_{no}$  and  $p_{po}$ . The metallurgical junction zone has been depleted of carriers compared with the bulk. Any applied voltage must therefore drop across the SCL.

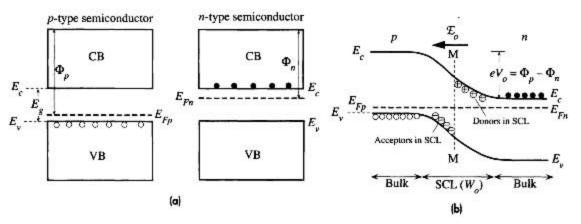

## 6.2.2 FORWARD AND REVERSE BIAS

The energy band diagram of the pn junction under open circuit conditions is shown in Figure 6.11a. There is no net current, so the diffusion current of electrons from the n- to p-side is balanced by the electron drift current from the p- to n-side driven by the built-in field  $\mathcal{E}_o$ . Similar arguments apply to holes. The probability that an electron diffuses from  $E_c$  in the n-side to  $E_c$  in the p-side determines the diffusion current density  $I_{\text{diff}}$ . The probability of overcoming the PE barrier is proportional to  $\exp(-eV_o/kT)$ . Therefore, under zero bias,

$$J_{\rm diff}(0) = B \exp\left(-\frac{eV_o}{kT}\right)$$

[6.20]

$$J_{\text{net}}(0) = J_{\text{diff}}(0) + J_{\text{drift}}(0) = 0$$

[6.21]

where B is a proportionality constant and  $J_{\text{drift}}(0)$  is the current due to the drift of electrons by  $\mathcal{E}_o$ . Clearly  $J_{\text{drift}}(0) = -J_{\text{diff}}(0)$ ; that is, drift is in the opposite direction to diffusion.

When the pn junction is forward-biased, the majority of the applied voltage drops across the depletion region, so the applied voltage is in opposition to the built-in potential  $V_o$ . Figure 6.11b shows the effect of forward bias, which is to reduce the PE

Figure 6.11 Energy band diagrams for a pn junction: [a] open circuit, (b) forward bias, (c) reverse bias conditions, [d] thermal generation of electron-hole pairs in the depletion region results in a small reverse current.

barrier from  $eV_o$  to  $e(V_o-V)$ . The electrons at  $E_c$  in the *n*-side can now readily overcome the PE barrier and diffuse to the *p*-side. The diffusing electrons from the *n*-side can be replenished easily by the negative terminal of the battery connected to this side. Similarly holes can now diffuse from the *p*- to *n*-side. The positive terminal of the battery can replenish those holes diffusing away from the *p*-side. There is therefore a current flow through the junction and around the circuit.

The probability that an electron at  $E_c$  in the *n*-side overcomes the new *PE* barrier and diffuses to  $E_c$  in the *p*-side is now proportional to  $\exp[-e(V_o - V)/kT]$ . The latter increases enormously even for small forward voltages. The new diffusion current due

to electrons diffusing from the n- to p-side is

$$J_{\text{diff}}(V) = B \exp \left[ -\frac{e(V_o - V)}{kT} \right]$$

There is still a drift current due to electrons being drifted by the new field  $\mathcal{E}_o - \mathcal{E}$  ( $\mathcal{E}$  is the applied field) in the SCL. This drift current now has the value  $J_{\text{drift}}(V)$ . The net current is the diode current under forward bias

$$J = J_{\text{diff}}(V) + J_{\text{drift}}(V)$$

$J_{\text{drift}}(V)$  is difficult to evaluate. As a first approximation we can assume that although  $\mathcal{E}_o$  has decreased to  $\mathcal{E}_o - \mathcal{E}$ , there is, however, an increase in the electron concentration in the SCL due to diffusion so that we can approximately take  $J_{\text{drift}}(V)$  to remain the same as  $J_{\text{drift}}(0)$ . Thus

$$J \approx J_{\text{diff}}(V) + J_{\text{drift}}(0) = B \exp\left[-\frac{e(V_o - V)}{kT}\right] - B \exp\left(-\frac{eV_o}{kT}\right)$$

Factoring leads to

$$J \approx B \exp\left(-\frac{eV_o}{kT}\right) \left[\exp\left(\frac{eV}{kT}\right) - 1\right]$$

We should also add to this the hole contribution, which has a similar form with a different constant B. The diode current-voltage relationship then becomes the familiar diode equation,

$$J = J_o \left[ \exp \left( \frac{eV}{kT} \right) - 1 \right]$$

pn Junction I-V characteristics

where  $J_o$  is a temperature-dependent constant.<sup>5</sup>

When a reverse bias,  $V = -V_r$ , is applied to the pn junction, the voltage again drops across the SCL. In this case, however,  $V_r$  adds to the built-in potential  $V_o$ , so the PE barrier becomes  $e(V_o + V_r)$ , as shown in Figure 6.11c. The field in the SCL at M increases to  $\mathcal{E}_o + \mathcal{E}$ , where  $\mathcal{E}$  is the applied field.

The diffusion current due to electrons diffusing from  $E_c$  in the n-side to  $E_c$  in the p-side is now almost negligible because it is proportional to  $\exp[-e(V_o + V_r)/kT]$ , which rapidly becomes very small with  $V_r$ . There is, however, a small reverse current arising from the drift component. When an electron-hole pair (EHP) is thermally generated in the SCL, as shown in Figure 6.11d, the field here separates the pair. The electron falls down the PE hill, down to  $E_c$ , in the n-side to be collected by the battery. Similarly the hole falls down its own PE hill (energy increases downward for holes) to make it to the p-side. The process of falling down a PE hill is the same process as being driven by a field, in this case by  $\mathcal{E}_o + \mathcal{E}$ . Under reverse bias conditions, there is therefore a small reverse current that depends on the rate of thermal generation of EHPs in the SCL. An electron in the p-side that is thermally generated within a diffusion length

<sup>1 &</sup>lt;sup>5</sup> The derivation is similar to that for the Schottky diode, but there were more assumptions here.

$L_{\epsilon}$  to the SCL can diffuse to the SCL and consequently can become drifted by the field, that is, roll down the PE hill in Figure 6.11d. Such minority carrier thermal generation in neutral regions can also give rise to a small reverse current.

## **EXAMPLE 6.5**

**THE BUILT-IN VOLTAGE V\_o FROM THE ENERGY BAND DIAGRAM** The energy band treatment allows a simple way to calculate  $V_o$ . When the junction is formed in Figure 6.10 from a to b,  $E_{Fp}$  and  $E_{Fn}$  must shift and line up. Using the energy band diagrams in this figure and semiconductor equations for n and p, derive an expression for the built-in voltage  $V_o$  in terms of the material and doping properties  $N_d$ ,  $N_a$ , and  $n_i$ .

#### SOLUTION

The shift in  $E_{Fp}$  and  $E_{Fn}$  to line up is clearly  $\Phi_p - \Phi_n$ , the work function difference. Thus the *PE* barrier  $eV_o$  is  $\Phi_p - \Phi_n$ . From Figure 6.10, we have

$$eV_o = \Phi_p - \Phi_n = (E_c - E_{Fp}) - (E_c - E_{Fn})$$

But on the p- and n-sides, the electron concentrations in thermal equilibrium are given by

$$n_{po} = N_c \exp \left[ -\frac{(E_c - E_{Fp})}{kT} \right]$$

$$n_{no} = N_c \exp \left[ -\frac{(E_c - E_{Pn})}{kT} \right]$$

From these equations, we can now substitute for  $(E_c - E_{Fp})$  and  $(E_c - E_{Fn})$  in the expression for  $eV_o$ . The  $N_c$  cancel and we obtain

$$eV_o = kT \ln \left(\frac{n_{no}}{n_{no}}\right)$$

Since  $n_{po} = n_i^2/N_a$  and  $n_{no} = N_d$ , we readily obtain the built-in potential  $V_o$ ,

Built-in voltage

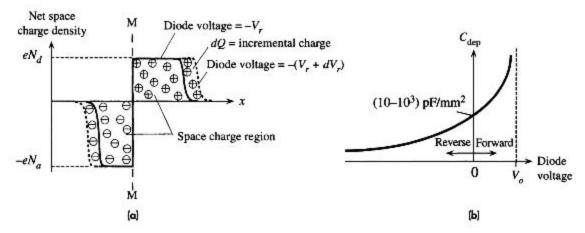

# 6.3 DEPLETION LAYER CAPACITANCE OF THE pn JUNCTION

It is apparent that the depletion region of a pn junction has positive and negative charges separated over a distance W similar to a parallel plate capacitor. The stored charge in the depletion region, however, unlike the case of a parallel plate capacitor, does not depend linearly on the voltage. It is useful to define an incremental capacitance that relates the incremental charge stored to an incremental voltage change across the pn junction.

The width of the depletion region is given by

Depletion region width

$$W = \left\lceil \frac{2\varepsilon (N_a + N_d)(V_o - V)}{eN_o N_d} \right\rceil^{1/2}$$

[6.22]

where, for forward bias, V is positive, which reduces  $V_o$ , and, for reverse bias, V is negative, so  $V_o$  is increased. We are interested in obtaining the capacitance of the

Figure 6.12 The depletion region behaves like a capacitor.

- (a) The charge in the depletion region depends on the applied voltage just as in a capacitor. A reverse bias example is shown.

- (b) The incremental capacitance of the depletion region increases with forward bias and decreases with reverse bias. Its value is typically in the range of picofarads per mm<sup>2</sup> of device area.

depletion region under dynamic conditions, that is, when V is a function of time. When the applied voltage V changes by dV, to V + dV, then W also changes via Equation 6.22, and as a result, the amount of charge in the depletion region becomes Q + dQ, as shown in Figure 6.12a for the reverse bias case, that is,  $V = -V_r$  and  $dV = -dV_r$ . The **depletion layer capacitance**  $C_{\text{dep}}$  is defined by

$$C_{\text{dep}} = \left| \frac{dQ}{dV} \right| \tag{6.23}$$

Definition of depletion layer capacitance

where the amount of charge (on any one side of the depletion layer) is

$$|Q| = eN_dW_nA = eN_aW_pA$$

and  $W = W_n + W_p$ . We can therefore substitute for W in Equation 6.22 in terms of Q and then differentiate it to obtain dQ/dV. The final result for the depletion capacitance is

$$C_{\text{dep}} = \frac{\varepsilon A}{W} = \frac{A}{(V_o - V)^{1/2}} \left[ \frac{e\varepsilon (N_a N_d)}{2(N_o + N_d)} \right]^{1/2}$$

[6.24]

Depletion capacitance

We should note that  $C_{\text{dep}}$  is given by the same expression as that for the parallel plate capacitor,  $\varepsilon A/W$ , but with W being voltage dependent by virtue of Equation 6.22. The  $C_{\text{dep}} - V$  behavior is sketched in Figure 6.12b. Notice that  $C_{\text{dep}}$  decreases with increasing reverse bias, which is expected since the separation of the charges increases via  $W \propto (V_o + V_r)^{1/2}$ . The capacitance  $C_{\text{dep}}$  is present under both forward and reverse bias conditions.

The voltage dependence of the depletion capacitance is utilized in **varactor diodes** (varicaps), which are employed as voltage-dependent capacitors in tuning circuits. A varactor diode is reverse biased to prevent conduction, and its depletion capacitance is varied by the magnitude of the reverse bias.

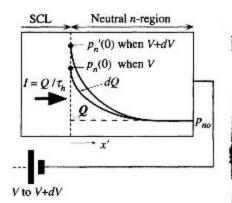

## 6.4 DIFFUSION (STORAGE) CAPACITANCE AND DYNAMIC RESISTANCE

The diffusion or storage capacitance arises under forward bias only. As shown in Figure 6.2a, when the  $p^+n$  junction is forward biased, we have stored a positive charge on the *n*-side by the continuous injection and diffusion of minority carriers. Similarly, a negative charge has been stored on the  $p^+$ -side by electron injection, but the magnitude of this negative charge is small for the  $p^+n$  junction. When the applied voltage is increased from V to V + dV, as shown in Figure 6.13, then  $p_n(0)$  changes from  $p_n(0)$  to  $p'_n(0)$ . If dQ is the additional minority carrier charge injected into the *n*-side, as a result of a small increase dV in V, then the incremental **storage** or **diffusion capacitance**  $C_{\text{diff}}$  is defined as  $C_{\text{diff}} = dQ/dV$ . At voltage V, the injected positive charge Q on the *n*-side is disappearing by recombination at a rate  $Q/\tau_h$ , where  $\tau_h$  is the minority carrier lifetime. The diode current I is therefore  $Q/\tau_h$ , from which

Injected minority carrier charge

$$Q = \tau_h I = \tau_h I_o \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right]$$

[6.25]

Thus.

Diffusion capacitance

$$C_{\text{diff}} = \frac{dQ}{dV} = \frac{\tau_h eI}{kT} = \frac{\tau_h I \text{ (mA)}}{25}$$

[6.26]

where we used  $e/kT \approx 1/0.025$  at room temperature. Generally the value of the diffusion capacitance, typically in the nanofarads range, far exceeds that of the depletion layer capacitance.

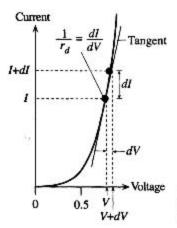

Suppose that the voltage V across the diode is increased by an infinitesimally small amount dV, as shown in an exaggerated way in Figure 6.14. This gives rise to a small increase dI in the diode current. We define the **dynamic** or **incremental resistance**  $r_d$  of the diode as dV/dI, so

Dynamic/ incremental resistance

$$r_d = \frac{dV}{dI} = \frac{kT}{eI} = \frac{25}{I(\text{mA})}$$

(6.27)

Figure 6.13 Consider the injection of holes into the n-side during forward bias.

Storage or diffusion capacitance arises because when the diode voltage increases from V to V + dV, more minority carriers are injected and more minority carrier charge is stored in the n-region.

Figure 6.14 The dynamic resistance of the diode is defined as dV/dl, which is the inverse of the tangent at l.

The dynamic resistance is therefore the inverse of the slope of the I-V characteristics at a point and hence depends on the current I. It relates the changes in the diode current and voltage arising from the **diode action** alone, by which we mean the modulation of the rate of minority carrier diffusion by the diode voltage. We could have equivalently defined a dynamic conductance by

$$g_d = \frac{dI}{dV} = \frac{1}{r_d}$$

Dynamic conductance

From Equations 6.26 and 6.27 we have

$$r_d C_{\text{diff}} = \tau_h \tag{6.28}$$

The dynamic resistance  $r_d$  and diffusion capacitance  $C_{\rm diff}$  of a diode determine its response to small ac signals under forward bias conditions. By *small* we usually mean voltages smaller than the thermal voltage kT/e or 25 mV at room temperature. For small ac signals we can simply represent a forward-biased diode as a resistance  $r_d$  in parallel with a capacitance  $C_{\rm diff}$ .

**INCREMENTAL RESISTANCE AND CAPACITANCE** An abrupt Si  $p^+n$  junction diode of cross-sectional area (A) 1 mm<sup>2</sup> with an acceptor concentration of  $5 \times 10^{18}$  boron atoms cm<sup>-3</sup> on the p-side and a donor concentration of  $10^{16}$  arsenic atoms cm<sup>-3</sup> on the n-side is forward-biased to carry a current of 5 mA. The lifetime of holes in the n-region is 417 ns, whereas that of electrons in the p-region is 5 ns. What are the small-signal ac resistance, incremental storage, and depletion capacitances of the diode?

#### SOLUTION

This is the same diode we considered in Example 6.4 for which the built-in potential was 0.877 V and  $I_{10} = 0.0836$  pA. The current through the diode is 5 mA. Thus

$$I = I_{so} \exp\left(\frac{eV}{kT}\right)$$

or  $V = \left(\frac{kT}{e}\right) \ln\left(\frac{I}{I_{so}}\right) = (0.0259) \ln\left(\frac{5 \times 10^{-3}}{0.0836 \times 10^{-12}}\right) = 0.643 \text{ V}$

**EXAMPLE 6.6**

The dynamic diode resistance is given by

$$r_d = \frac{25}{I(\text{mA})} = \frac{25}{5} = 5 \Omega$$

The depletion capacitance per unit area with  $N_a \gg N_d$  is

$$C_{\rm dep} = A \left[ \frac{e \varepsilon (N_a N_d)}{2(N_a + N_d)(V_o - V)} \right]^{1/2} \approx A \left[ \frac{e \varepsilon N_d}{2(V_o - V)} \right]^{1/2}$$

At V = 0.643 V, with  $V_o = 0.877$  V,  $N_d = 10^{22}$  m<sup>-3</sup>,  $\varepsilon_r = 11.9$ , and  $A = 10^{-6}$  m<sup>2</sup>, the above equation gives

$$C_{\text{dep}} = 10^{-6} \left[ \frac{(1.6 \times 10^{-19})(11.9)(8.85 \times 10^{-12})(10^{22})}{2(0.877 - 0.643)} \right]^{1/2}$$

= 6.0 × 10<sup>-10</sup> F or 600 pF

The incremental diffusion capacitance  $C_{\text{diff}}$  due to holes injected and stored in the n-region is

$$C_{\text{diff}} = \frac{r_h I \text{ (mA)}}{25} = \frac{(417 \times 10^{-9})(5)}{25} = 8.3 \times 10^{-8} \text{ F}$$

or 83 nF

Clearly the diffusion capacitance (83 nF) that arises during forward bias completely overwhelms the depletion capacitance (600 pF).

We note that there is also a diffusion capacitance due to electrons injected and stored in the p-region. However, electron lifetime in the p-region is very short (here 5 ns), so the value of this capacitance is much smaller than that due to holes in the n-region. In calculating the diffusion capacitance, we normally consider the minority carriers that have the longest recombination lifetime, here  $\tau_h$ . These are the carriers that take a long time to disappear by recombination when the bias is suddenly switched off.

## 6.5 REVERSE BREAKDOWN: AVALANCHE AND ZENER BREAKDOWN

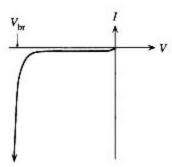

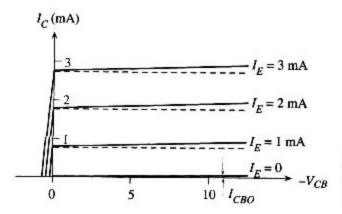

The reverse voltage across a pn junction cannot be increased without limit. Eventually the pn junction breaks down either by the Avalanche or Zener breakdown mechanisms, which lead to large reverse currents, as shown in Figure 6.15. In the  $V = -V_{br}$  region, the reverse current increases dramatically with the reverse bias. If unlimited, the large

Figure 6.15 Reverse I-V, characteristics of a pri junction.

reverse current will increase the power dissipated, which in turn raises the temperature of the device, which leads to a further increase in the reverse current and so on. If the temperature does not burn out the device, for example, by melting the contacts, then the breakdown is recoverable. If the current is limited by an external resistance to a value within the power dissipation specifications, then there is no reason why the device cannot operate under breakdown conditions.

## 6.5.1 AVALANCHE BREAKDOWN

As the reverse bias increases, the field in the SCL can become so large that an electron drifting in this region can gain sufficient kinetic energy to impact on a Si atom and ionize it, or break a Si-Si bond. The phenomenon by which a drifting electron gains sufficient energy from the field to ionize a host crystal atom by bombardment is termed **impact ionization**. The accelerated electron must gain at least an energy equal to  $E_g$  as impact ionization breaks a Si-Si bond, which is tantamount to exciting an electron from the valence band to the conduction band. Thus an additional electron-hole pair is created by this process.

Consider what happens when a thermally generated electron just inside the SCL in the p-side is accelerated by the field. The electron accelerates and gains sufficient energy to collide with a host Si atom and release an EHP by impact ionization, as depicted in Figure 6.16. It will lose at least  $E_g$  amount of energy, but it can accelerate and head for another ionizing collision further along the depletion region until it reaches the neutral n-region. The EHPs generated by impact ionization themselves can now be accelerated by the field and will themselves give rise to further EHPs by ionizing collisions and so on, leading to an **avalanche effect**. One initial carrier can thus create many carriers in the SCL through an avalanche of impact ionizations.

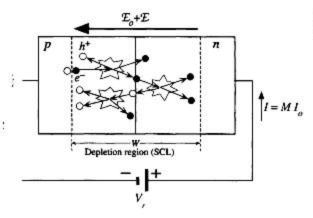

If the reverse current in the SCL in the absence of impact ionization is  $I_o$ , then due to the avalanche of ionizing collisions in the SCL, the reverse current becomes  $MI_o$  where M is the multiplication. It is the net number of carriers generated by the avalanche effect per carrier in the SCL. Impact ionization depends strongly on the electric field. Small increases in the reverse bias can lead to dramatic increases in the

Figure 6.16 Avalanche breakdown by impact ionization.

multiplication process. Typically

$$M = \frac{1}{1 - \left(\frac{V_r}{V_{\text{br}}}\right)^n}$$

[6.29]

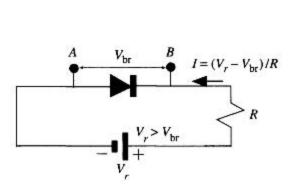

where  $V_r$  is the reverse bias,  $V_{br}$  is the breakdown voltage, and n is an index in the range 3 to 5. It is clear that the reverse current  $MI_o$  increases sharply with  $V_r$  near  $V_{br}$ , as depicted in Figure 6.15. Indeed, the voltage across a diode under reverse breakdown remains around  $V_{br}$  for very large current variations (several orders of magnitude). If the reverse current under breakdown is limited by an appropriate external resistor R, as shown in Figure 6.17, to prevent destructive power dissipation in the diode, then the voltage across the diode remains approximately at  $V_{br}$ . Thus, as long as  $V_r > V_{br}$ , the diode clamps the voltage between A and B to approximately  $V_{br}$ . The reverse current in the circuit is then  $(V_r - V_{br})/R$ .

Since the electric field in the SCL depends on the width of the depletion region W, which in turn depends on the doping parameters,  $V_{br}$  also depends on the doping, as discussed in Example 6.7.

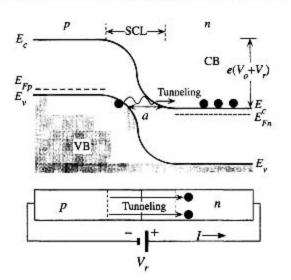

## 6.5.2 ZENER BREAKDOWN

Heavily doped pn junctions have narrow depletion widths, which lead to large electric fields within this region. When a reverse bias is applied to a pn junction, the energy band diagram of the n-side can be viewed as being lowered with respect to the p-side, as depicted in Figure 6.18. For a sufficient reverse bias (typically less than 10 V),  $E_r$

**Figure 6.17** If the reverse breakdown current when  $V_r > V_{br}$  is limited by an external resistance R to prevent destructive power dissipation, then the diode can be used to clamp the voltage between A and B to remain approximately  $V_{br}$ .

Figure 6.18 Zener breakdown involves electrons tunneling from the VB of p-side to the CB of p-side when the reverse bias reduces E<sub>c</sub> to line up with E<sub>v</sub>.

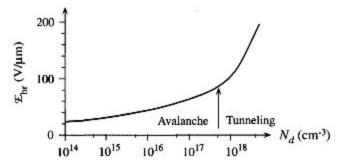

**Figure 6.19** The breakdown field  $\mathcal{E}_{br}$  in the depletion layer for the onset of reverse breakdown versus doping concentration  $\mathcal{N}_d$  in the lightly doped region in a one-sided  $(p^+n \text{ or } pn^+)$  abrupt pn junction.

Avalanche and tunneling mechanisms are separated by the arrow.

SOURCE: Data extracted from M. Sze and G. Gibbons, Solid State Electronics, 9, no. 831, 1966.

on the n-side may be lowered to be below  $E_v$  on the p-side. This means that electrons at the top of the VB in the p-side are now at the same energy level as the empty states in the CB in the n-side. As the separation between the VB and CB narrows, shown as  $a \ (< W)$ , the electrons easily tunnel from the VB in the p-side to the CB in the n-side, which leads to a current. This process is called the **Zener effect.** As there are many electrons in the VB and many empty states in the CB, the tunneling current can be substantial. The reverse voltage  $V_r$ , which starts the tunneling current and hence the Zener breakdown, is clearly that which lowers  $E_c$  on the n-side to be below  $E_v$  on the p-side and thereby gives a separation that encourages tunneling. In nonquantum mechanical terms, one may intuitively view the Zener effect as the strong electric field in the depletion region ripping out some of those electrons in the Si-Si bonds and thereby releasing them for conduction.

Figure 6.19 shows the dependence of the breakdown field  $\mathcal{E}_{br}$  in the depletion region for the onset of avalanche or Zener breakdown in a one-sided  $(p^+n \text{ or } pn^+)$  abrupt junction on the dopant concentration  $N_d$  in the lightly doped side. At high fields, the tunneling becomes the dominant reverse breakdown mechanism.

**AVALANCHE BREAKDOWN** Consider a uniformly doped abrupt  $p^+n$  junction  $(N_a \gg N_d)$  reverse biased by  $V = -V_r$ .

**EXAMPLE 6.7**

- a. What is the relationship between the depletion width W and the potential difference (V<sub>a</sub> + V<sub>r</sub>) across W?

- b. If avalanche breakdown occurs when the maximum field in the depletion region E<sub>o</sub> reaches the breakdown field E<sub>br</sub>, show that the breakdown voltage V<sub>br</sub> (≫ V<sub>o</sub>) is then given by

$$V_{\rm br} = \frac{\varepsilon \mathcal{E}_{\rm br}^2}{2eN_d}$$

- c. An abrupt Si  $p^+n$  junction has boron doping of  $10^{19}$  cm<sup>-3</sup> on the *p*-side and phosphorus doping of  $10^{16}$  cm<sup>-3</sup> on the *n*-side. The dependence of the avalanche breakdown field on the impurity concentration is shown in Figure 6.19.

- 1. What is the reverse breakdown voltage of this Si diode?

- Calculate the reverse breakdown voltage when the phosphorus doping is increased to 10<sup>17</sup> cm<sup>-3</sup>.

#### SOLUTION

One can assume that all the applied reverse bias drops across the depletion layer so that the new voltage across W is now  $V_o + V_r$ . We have to integrate  $d\mathcal{E}/dx = \rho_{\text{net}}/\varepsilon$  as before across W to find the maximum field. The most important fact to remember here is that the pn junction equations relating W,  $\mathcal{E}_o$ ,  $V_o$ ,  $N_o$ ,  $N_d$ , and so on remain the same but with  $V_o$  replaced with  $V_o + V_r$ , since the applied reverse bias of  $V_r$  increases  $V_o$  to  $V_o + V_r$ . Then from Equation 6.4,

$$W^{2} = \frac{2\varepsilon(V_{o} + V_{r})(N_{o}^{-1} + N_{d}^{-1})}{e} \approx \frac{2\varepsilon(V_{o} + V_{r})}{eN_{d}}$$

since  $N_u \gg N_d$ . The maximum field that corresponds to the breakdown field  $\mathcal{L}_{br}$  is given by

Maximum field and reverse bias

Breakdown voltage and

doping

$$\mathcal{E}_o = -\frac{2(V_o + V_r)}{W}$$

Thus, from these two equations we can eliminate W and obtain  $V_{br} = V$ , as

$$V_{\rm br} = \frac{\varepsilon \mathcal{E}_{\rm hr}^2}{2eN_d}$$

Given  $N_a \gg N_d$  we have a  $p^+n$  junction with  $N_d=10^{16}$  cm<sup>-3</sup>. The depletion region extends into the *n*-region, so the maximum field actually occurs in the *n*-region. Here the breakdown field  $\mathcal{E}_{br}$  depends on the doping level as given in the graph of the critical field at breakdown  $\mathcal{E}_{br}$  versus doping concentration  $N_d$  in Figure 6.19. Taking  $\mathcal{E}_{br} \approx 40 \text{ V}/\mu\text{m}$  or  $4.0 \times 10^5 \text{ V cm}^{-1}$  at  $N_d=10^{16} \text{ cm}^{-3}$  and using the above equation for  $V_{br}$ , we get  $V_{br}=53 \text{ V}$ .

When  $N_d = 10^{17}$  cm<sup>-3</sup>,  $\mathcal{L}_{br}$  from the graph is about  $6 \times 10^5$  V cm<sup>-1</sup>, which leads to  $V_{br} = 11.8$  V.

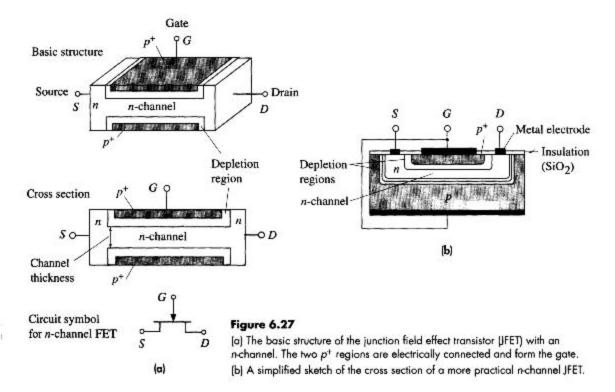

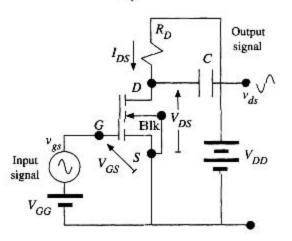

## 6.6 BIPOLAR TRANSISTOR (B.JT)

## 6.6.1 COMMON BASE (CB) DC CHARACTERISTICS

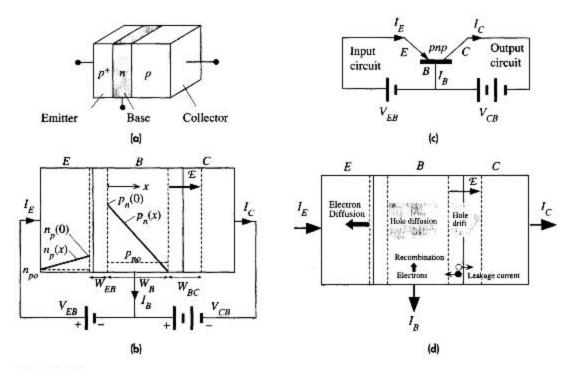

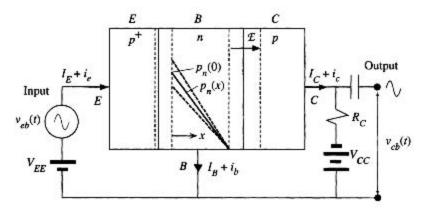

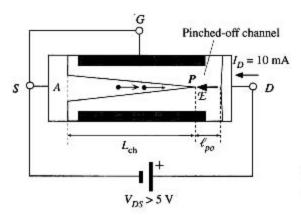

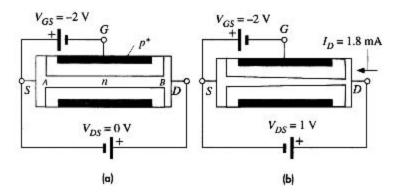

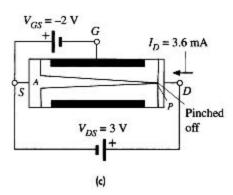

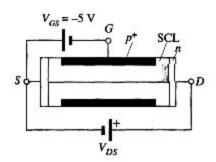

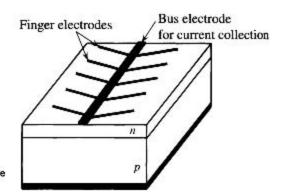

As an example, we will consider the pnp bipolar junction transistor (BJT) whose basic structure is shown in Figure 6.20a. The pnp transistor has three differently doped semiconductor regions. These regions of different doping occur within the same single crystal by the variation of acceptor and donor concentrations resulting from the fabrication process. The most heavily doped p-region ( $p^+$ ) is called the **emitter**. In contact with this region is the lightly doped p-region, which is called the **base**. The next region is the p-type doped **collector**. The base region has the most narrow width for reasons discussed below. Although the three regions in Figure 6.20a have identical cross-sectional areas, in practice, due to the fabrication process, the cross-sectional area increases from the emitter to the collector and the collector region has an extended width. For simplicity, we will assume that the cross-sectional area is uniform, as in Figure 6.20a.

The pnp BJT connected as shown in Figure 6.20b is said to be operating under normal and active conditions, which means that the base-emitter (BE) junction is forward biased and the base-collector (BC) junction is reverse biased. The circuit in

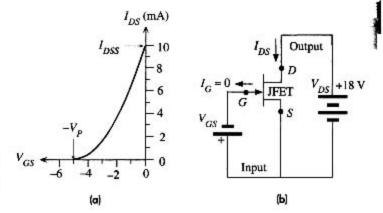

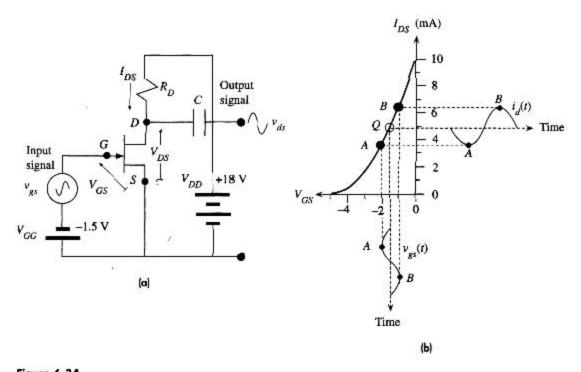

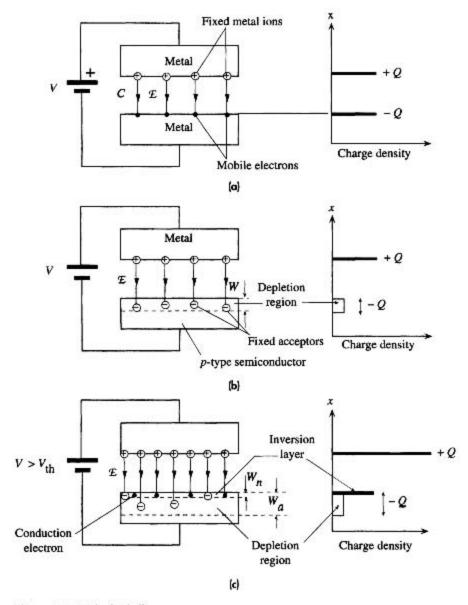

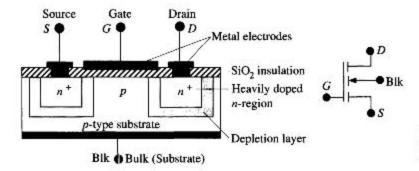

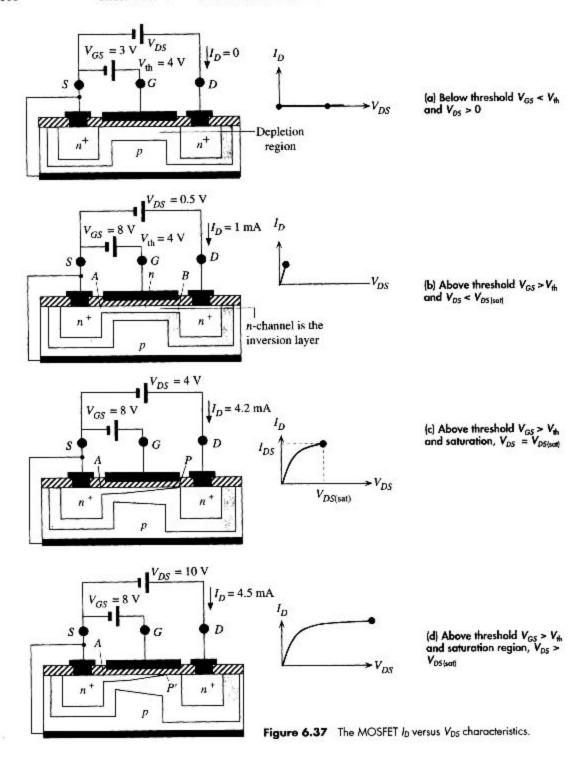

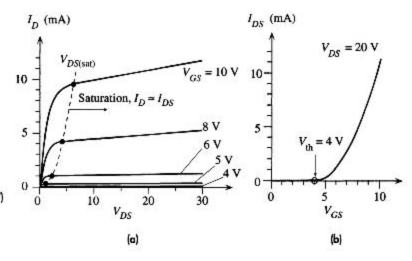

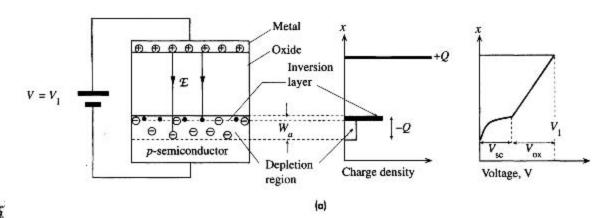

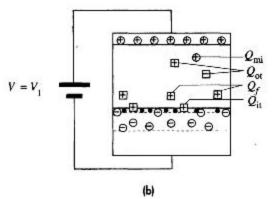

Figure 6.20

- (a) A schematic illustration of the pnp bipolar transistor with three differently doped regions.

- (b) The pnp bipolar operated under normal and active conditions.

- (c) The CB configuration with input and output circuits identified.

- (d) The illustration of various current components under normal and active conditions.

Figure 6.20b, in which the base is common to both the collector and emitter bias voltages, is known as the common base (CB) configuration. Figure 6.20c shows the CB transistor circuit with the BJT represented by its circuit symbol. The arrow identifies the emitter junction and points in the direction of current flow when the EB junction is forward biased. Figure 6.20c also identifies the emitter circuit, where  $V_{EB}$  is connected, as the input circuit. The collector circuit, where  $V_{CB}$  is connected, is the output circuit.

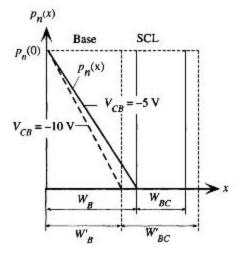

The base-emitter junction is simply called the **emitter junction** and the base-collector junction is called the **collector junction**. As the emitter is heavily doped, the base-emitter depletion region  $W_{EB}$  extends almost entirely into the base. Generally, the base and collector regions have comparable doping, so the base-collector depletion region  $W_{BC}$  extends to both sides. The width of the neutral base region outside the depletion regions is labeled as  $W_B$ . All these parameters are shown and defined in Figure 6.20b.

<sup>6</sup> CB should not be confused with the conduction band abbreviation.

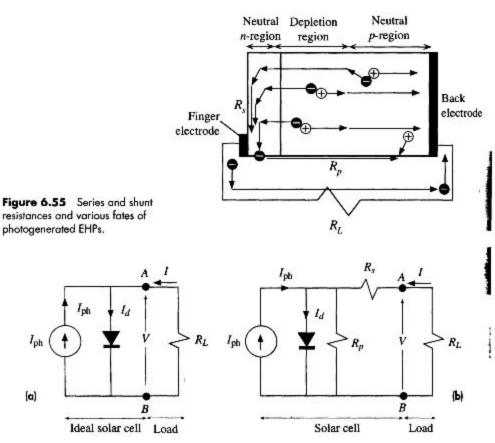

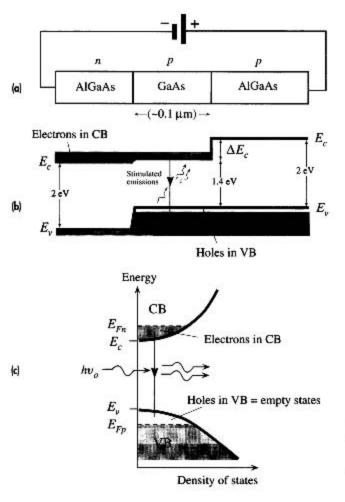

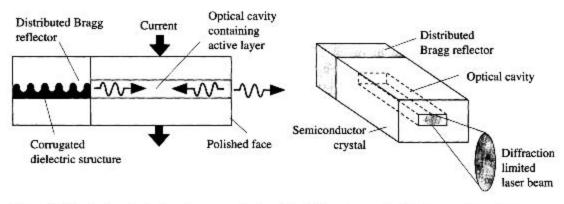

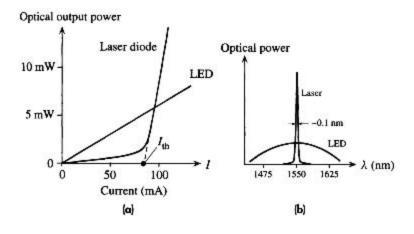

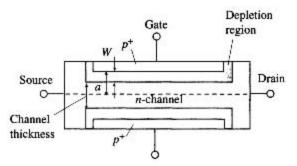

We should note that all the applied voltages drop across the depletion widths. The applied collector-base voltage  $V_{CB}$  reverse biases the BC junction and hence increases the field in the depletion region at the collector junction.