# RISC MICROPROCESSORS: INTEL 80960, MOTOROLA MC88100 AND POWERPC

This chapter provides an overview of the hardware, software, and interfacing features associated with three popular RISC microprocessors namely, the Intel 80960 SA/SB, the Motorola MC88100, and the PowerPC. Finally, the basic features of typical 64-bit RISC mircoprocessors are discussed.

### 8.1 Basics of RISC

RISC is an acronym for Reduced Instruction Set Computer. This type of microprocessor emphasizes simplicity and efficiency. RISC designs start with a necessary and sufficient instruction set. The purpose of using RISC architecture is to maximize speed by reducing clock cycles per instruction. Almost all computations can be obtained from a few simple operations. The goal of RISC architecture is to maximize the effective speed of a design by performing infrequent operations in software and frequent functions in hardware, thus obtaining a net performance gain.

The following summarizes the typical features of a RISC microprocessor:

- 1. The microprocessor is designed using hardwired control with little or no microcode. Note that variable length instruction formats generally require microcode design. All RISC instructions have fixed formats, and therefore microcode design is not necessary.

- 2. A RISC microprocessor executes most instructions in a single cycle.

- 3. The instruction set of a RISC microprocessor typically includes only register-to-register, load, and store. All instructions involving arithmetic operations use registers, while load and store operations are utilized to access memory.

- 4. The instructions have simple fixed format with few addressing modes.

- 5. A RISC microprocessor has several general-purpose registers and large cache memories.

- 6. A RISC microprocessor processes several instructions simultaneously and thus includes

- pipelining. 7. Software can take advantage of more concurrency. For example, Jumps occur after execution of the instruction that follows. This allows fetching of the next instruction during execution of the current instruction.

RISC microprocessors are suitable for embedded applications. An embedded application is one in which the processor monitors and analyzes signals from one segment of the system and

produces output required by another segment of the system; thus, it behaves as a controller that bridges various parts of the entire system. It performs all its functions without any user input.

RISC microprocessors are well suited for applications such as image processing, robotics, graphics, and instrumentation. The key features of the RISC microprocessors that make them ideal for these applications are their relatively low level of integration in the chip and instruction pipeline architecture. These characteristics result in low power consumption, fast instruction execution, and fast recognition of interrupts.

The state-of-the-art 64-bit RISC microprocessors include Digital Equipment Corporation's Alpha 21164, Motorola/IBM/Apple PowerPC 620 and Sun Microsystems Ultrasparc. Among these processors, the Alpha 21164 is the fastest with a maximum clock frequency of 300 MHz, four-way superscalar design, and 128-bit data bus. These processors are compared later in this chapter.

### 8.2 Intel 80960

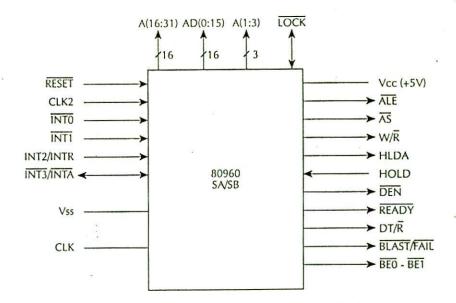

The Intel 80960 family includes two types of 16-bit RISC microprocessors. These are the 80960SA and 80960SB processors. The 80960SA is designed as an Intra-agent communication (IAC) microprocessor. IAC messages can be sent for execution into the bus interface of a 80960SA processor from software executing on another processor.

The 80960SB, on the other hand, is designed as a floating-point RISC microprocessor and includes on-chip floating-point hardware.

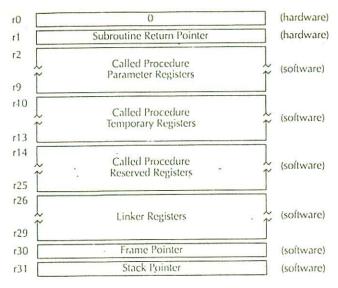

The 80960SA contains 32 32-bit registers while the 80960SB includes an additional four floating-point registers with a total of 36 32-bit registers.

The 80960SA/SB comes in two speeds: 10MHz and 16MHz. The clock input is divided by 2 internally to generate the internal processor clock.

### 8.2.1 Introduction

This section covers the basic architecture of the chip, its instruction set, typical 80960 based system design utilizing a burst controller with burst and non-burst memories.

### 8.2.2 Key Performance Features

The following summarizes the main features of the 80960SA/SB:

### 8.2.2.a Load and Store Model

Most operations are performed on operands in CPU registers rather than in memory. All of the arithmetic, comparison, branching, and bit operations are performed with registers and literals (5-bit and floating-point). Only LOAD & STORE are memory reference instructions.

### 8.2.2.b Large Internal Register Sets

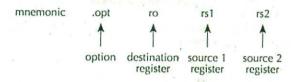

Large internal register sets featuring 32 32-bit general purpose and specific function registers are divided into two types: global and local. Both of these types can be used for general storage of operands. The only difference between global and local registers is the global registers retain their contents across procedure boundaries, whereas the processor allocates a new set of local registers each time a procedure is called.

### 8.2.2.c On-Chip Code and Data Caching

To reduce memory accesses, two features are added: an instruction cache and multiple sets of local registers. The former allows pre-fetching of blocks of instructions from the main memory while the latter allows the processor to perform most procedure calls without having to write the local registers out to the stack in memory.

### 8.2.2.d Overlapped Instruction Execution

This is accomplished through a register scoreboarding scheme which enhances program execution speed. Register scoreboarding permits instruction execution to continue while data are being fetched from memory. When a load instruction is executed, the processor sets one or more scoreboard bits to indicate the target registers to be loaded. After the target registers are loaded, the scoreboard bits are cleared. While the target registers are being loaded, the processor is allowed to execute other instructions, called independent instructions, that do not use these registers. The net result of using this technique is that code can often be optimized in such a way as to allow some instructions to be executed in parallel.

#### 8.2.2.e Single Clock Instructions

Most of the commonly used instructions are executed in a minimum number of clock cycles (usually one clock).

For example, instructions, either 32 or 64-bits long, are aligned on 32-bit boundaries allowing instructions to be decoded in one clock cycle. This eliminates the need for an instruction-alignment stage in the pipeline resulting in over 50 instructions that can be executed in a single clock cycle.

#### 8.2.2.f Interrupt Model

To handle interrupts, the processor maintains an interrupt table of 248 interrupt vectors, of which 240 are available for general use. When an interrupt is generated, the processor uses a pointer from the interrupt table to perform an implicit call to an interrupt handler procedure. The processor automatically saves the state of the processor prior to receiving the interrupt, performs the interrupt routine, and then restores its previous state. A separate interrupt stack is also provided to segregate interrupt handling from application programs. Interrupt handling facilities feature prioritizing pending interrupts.

### 8.2.2.g Procedure Call Mechanism

Each time a call instruction is issued, the processor automatically saves the current set of local registers and allocates a new set of local registers for the called procedure. Likewise, on the return from a procedure, the current set of local registers is deallocated and the local registers for the procedure being returned to are restored. Thus, on a procedure call, the program never has to explicitly save and restore those local variables.

#### 8.2.2.h Instruction Set and Addressing

The processor offers a full set of load, store, move, arithmetic, comparison, and branch instructions, with operations on both integer and ordinal data types. It also provides a complete set of Boolean and bit-field instructions, to simplify operations on bits and bit strings. The addressing modes are efficient and straightforward, while at the same time providing the necessary indexing and scaling modes required to address complex array and records.

The 32 address lines provide 4-gigabytes of address space for programs and data.

Table 8.1 lists the 80960SA/SB instruction set. The 80960SA does not include the floatingpoint instructions.

#### 8.2.2.i Floating Point Unit (Available with 80960SB only)

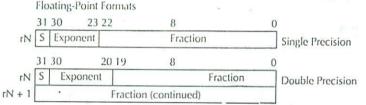

The on-chip floating point unit includes a full set of floating point operations including add, subtract, multiply, divide, trigonometric functions, and logarithmic functions. These operations are performed on single precision (32-bit), double precision (64-bit), and extended precision (80-bit) data. Four 80-bit floating-point registers are provided to hold extended precision values.

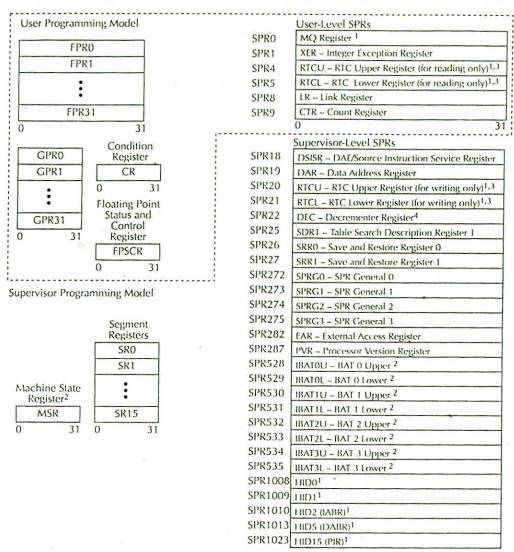

#### 8.2.3 80960 SA/SB Registers

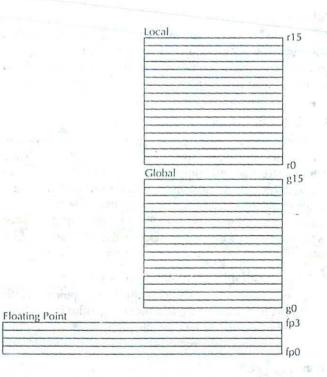

Figure 8.1 shows the 80960SB registers. The processor provides three types of data registers: global, floating-point, and local. As their names imply, the global registers constitute a set of general-purpose registers whose contents are retained across procedure boundaries. The

| Data Movement                                                                                                           | Arithmetic                                                                                                                                                   | Logical                                                                                        | Bit and Bit Field                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Load, Store, Move, Load<br>Address                                                                                      | Add, Subtract, Multiply,<br>Divide, Shift, Remainder,<br>Modulo, Extended<br>Multiply, Extended Divide                                                       | And, Not And, And Not, Or,<br>Xor, Not Or, Or Not, Nor,<br>Exclusive Nor, Not, Nand,<br>Rotate | Set Bit, Clear Bit, Not Bit,<br>Check Bit, Alter Bit, Scan<br>for Bit, Scan Over Bit,<br>Extract, Modify |

| Comparison                                                                                                              | Branch                                                                                                                                                       | Call/Return                                                                                    | Fault                                                                                                    |

| Compare, Conditional<br>Compare, Compare and<br>Increment, Compare and<br>Decrement                                     | Unconditional Branch,<br>Conditional Branch,<br>Compare and Branch                                                                                           | Call, Call extended, Call<br>system, Return, Branch and<br>Link                                | Conditional Fault,<br>Synchronous Fault                                                                  |

| Debug                                                                                                                   | Miscellaneous                                                                                                                                                | Decimal                                                                                        | Conversion                                                                                               |

| Modify Trace Controls,<br>Mark, Force Mark                                                                              | Atomic Add, Atomic Modify,<br>Flush Local Register, Modify<br>Arithmetic Controls, Modify<br>Process Control, Scan Byte<br>For Equal, Test Condition<br>Code | Move, Add with Carry,<br>Subtract with Carry                                                   | Convert Real to Integer,<br>Convert Integer to Real                                                      |

| Floating-Point                                                                                                          | and the state of the second                                                                                                                                  | Synchronous                                                                                    | EIN                                                                                                      |

| Move Real, Add, Subtract, M<br>Scale, Round, Square Root,<br>Arctangent, Log, Log Binary<br>Classify, Copy Real Extende | Sine, Cosine, Tangent,<br>7, Log Natural, Exponent,                                                                                                          | Synchronous Move, Synchrono                                                                    | ous Load                                                                                                 |

| TABLE 8.1 | 80960SA/SB | Instruction Set |

|-----------|------------|-----------------|

|-----------|------------|-----------------|

FIGURE 8.1 Local and global registers sets.

4 floating point registers are for extended precision floating point operations and are available only with the 80960SB. Their contents are also preserved across procedure calls. The 16 local registers are to hold local variables. For each procedure that is called, the processor allocates a separate set of local registers.

It should be noted that the global register g15 is reserved to hold the current frame pointer FP, while the others are available for general use. The local register r0 is used to hold the previous frame pointer (PFP), r1 is the stack pointer, r2 is used as a Return Instruction Pointer which is saved on the stack later and r3-r15 are available for general use.

Some special features of the 80960SB registers are provided in the following:

#### 8.2.3.a Register Scoreboarding

The main purpose is to permit instructions to be executed concurrently provided that they are independent instructions.

#### 8.2.3.b Instruction Pointer

The 32-bit r1 holds the address of the instruction currently being executed. Since the instructions are required to be aligned on a word boundary, the least significant 2 bits of IP are always 0. IP can not be read directly. However, IP can be used as an offset into address space. This addressing mode can be used with the load address (lda) instruction to read the current value of IP. When a break in instruction stream occurs due to an interrupt or procedure call, the IP contents will be stored in r2, and later saved on the stack.

#### .8.2.3.c Process Control Register

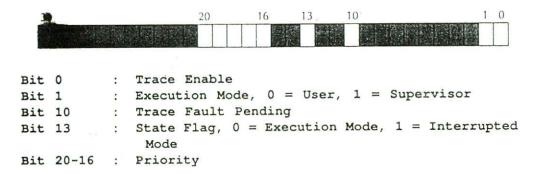

The processor's process control register is made up of a set of 32 bits, as shown below:

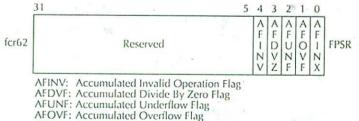

#### 8.2.3.d Arithmetic Control

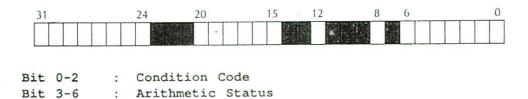

The arithmetic control bits include the condition code, arithmetic status, integer overflow flag and mask, floating point overflow, underflow, zero divide, invalid-op, inexact flags, masks, and faults. The processor sets or clears these bits to show the results of certain operations. For example, the processor modifies the condition code flags after each fault. These bits are set by the currently running program to tell the processor how to respond to certain fault conditions.

| Bit | 8     | : | Integer Overflow Flag                        |  |

|-----|-------|---|----------------------------------------------|--|

| Bit | 12    | : | Integer Overflow Mask                        |  |

| Bit | 15-20 | : | Floating Point Condition Flags               |  |

| Bit | 24-29 | : | Floating Point Condition Masks               |  |

| Bit | 30-31 | : | Floating Point Normalizing and Rounding Mode |  |

### 8.2.4 Data Types and Addresses

In order to be consistent with the data types included in the Intel 80960 manual, new terminologies such as ordinal and literals are introduced in this section.

#### 8.2.4.a Data Types

The processor defines and operates on the following data types:

- Integer (8, 16, 32, and 64 bits) signed whole numbers

- Ordinal (8, 16, 32, and 64 bits) general-purpose, unsigned whole numbers

- Real (32, 64, and 80 bits) confe

- icear (32, 64, and 60 bits

- (floating-point)

- · Bit/Bit Field

- Decimal (ASCII digits)

- Triple-Word (96 bits)

- · Quad-Word (128 bits)

conforms to IEEE single (32-bit), double (64-bits),

and extended precision (80-bit) floating point representations

span of 1 or more bits within register boundary decimal values in ASCII format.

- consecutive bytes

- consecutive bytes

#### 8.2.4.b Literals

The processor recognizes two types of literals: ordinal and floating-point, which can be used as operands in some instructions. An ordinal literal can range from 0 to 31 (5 bits). When an ordinal literal is used as an operand, the processor expands it to 32 bits by adding leading zeros. If an ordinal literal is used in an instruction that requires integer operands, the processor treats the literal as a positive integer value.

For floating-point, the processor recognizes two literals: +0.0 and +1.0. These floating point literals can only be used with floating point instructions. Ordinal literals can also be used in converting integer to real to get more values.

#### 8.2.4.c Register Addressing

A register may be used as an operand in an instruction by giving the register number (c.g., g0, f5, fp3). Both floating-point and non-floating-point instructions can reference global and local registers in this way. However, floating-point registers can only be referenced in conjunction with a floating-point instruction.

If the instruction requires more than one word, the reference is to the lowest number, which must be even when 2 words are required, must be multiples of four when 3 or 4 words are required. This is called "Register Alignment."

#### 8.2.4.d Memory Addressing Modes

Table 8.2 lists the 80960 memory addressing modes.

8.2.4.d.i Absolute Offset. Absolute offset is used to reference a memory location directly. An example is st g2, START which stores the word from register g2 into memory location START.

8.2.4.d.ii Register Indirect/Register Indirect with Offset. This mode permits an address to be specified with an ordinal value (32 bits) in a register or a displacement added to a value in a register. The register value is called the address base (abase). An example of register indirect is the ldob (r1), r2 which loads an ordinal byte from memory location addressed by r1 into r2. An example of

| Mode                                             | Description                             | Assembler Syntax    |

|--------------------------------------------------|-----------------------------------------|---------------------|

| Absolute offset                                  | offset                                  | exp                 |

| Register indirect                                | abase                                   | (reg)               |

| Register indirect with offset                    | abase + offset                          | exp(reg)            |

| Register indirect with index                     | abase + (index * scale)                 | (reg)[reg*scale]    |

| Register indirect with index<br>and displacement | abase + (index*scale) +<br>displacement | exp(reg)[reg*scale] |

| Index with displacement                          | (index*scale) + displacement            | exp[reg*scale]      |

| IP (instruction pointer) with displacement       | 1P + displacement + 8                   | exp(IP)             |

TABLE 8.2 80960 Memory Addressing Modes

register indirect with offset is stl g4, BEGIN(g2) which stores double word from g4, g5 stored at memory location addressed by BEGIN+(g2).

8.2.4.d.iii Register Indirect with Index/Register. This mode allows a scaled index value in another register to be added to the value in a register. The scale factor can be 1, 2, 4, 8, or 16. A displacement may also be added to the abase value and scaled index. An example is ldq (r1) [r2\*4], r4 which loads a quad-word starting at the memory location addressed by (r1)+(r2 scaled by 4) into register r4 through r7.

An example of register indirect with index and displacement is st g1, VALUE(g3)[g4\*4] which loads word in g1 into memory location addressed by (g3) +VALUE+(g4\*4).

- 8.2.4.d.iv Index with Displacement. This mode allows a scaled index to be used with a displacement. The index is contained in a register and is multiplied by a scaling constant before the displacement is added to it. An example is Idis VALUE [r8\*2], r10 which loads short integer at memory location addressed by VALUE+(r8\*2) into r10.

- 8.2.4.d.v IP with Displacement. This mode is often used with load and store instructions to make them IP relative. With this mode the displacement plus a constant of 8 is added to the IP of the instruction. An example is st r1, VALUE (IP) which stores words in r1 at memory location addressed by 8+IP+VALUE.

#### 8.2.5 80960SA/SB Instruction Set

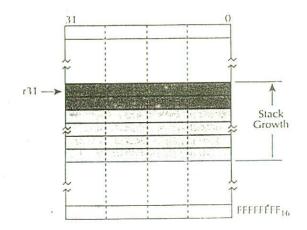

The 80960 includes 182 instructions. An assembly-language statement consists of an instruction mnemonic, followed by from 0 to 3 operands, separated by commas. The following example illustrates the assembly-language statement for the addo instruction:

adds the ordinal operands in global register g1 and g3 and stores the result in g5. The instructions can be classified into four categories:

- 1. Data Movement

- 2. Conversion

- 3. Arithmetic and Logic Operations

- 4. Comparison and Control

The following provides a list of operands used in the instructions:

reg \_\_\_\_\_ global (g0, g1, ..., g15) or local (r0, r1, ..., r15) registers

- freg global (g0, g1, ..., g15) or local (r0, r1, ..., r15) registers or floating-point (fp0 thru fp3) registers

- lit integer or ordinal literal of the range 0. . .31

- flit floating-point literal of value 1.0 or 0.0

522

disp — signed displacement of range -222 to +222-1

mem - address defined with the full range of addressing modes

addr — address

efa - effective address

#### 8.2.5.a Data Movement

The data movement instructions move data between the global and local registers, and between these registers and memory.

#### 8.2.5.a.i Load Instructions.

Load integer byte, ldib (8-bit) Load integer short, ldis (16-bit) mem, reg Load ordinal byte, ldob (8-bit) Load ordinal short, ldos (16-bit)

The above instructions load a byte or half word (2 bytes) and convert it into a full 32-bit word. Integers are sign-extended, ordinals and zero-extended automatically. For example, Idib (r1), r0 loads the 8-bit integer in memory addressed by r1 into register r0.

| Load | - 1d         | )      |     |

|------|--------------|--------|-----|

| Load | long - 1d1   | 1      |     |

| Load | triple - 1dt | } mem, | reg |

| Load | quad - 1dq   |        |     |

The ld, ldl, ldt and ldq instructions copy 4, 8, 12, and 16 bytes, respectively, from memory into successive registers.

ldl mem, reg must specify an even numbered register (eg. g0, g2, . . ., g16).

ldt mem, reg and ldq mem, reg must specify a register that is a multiple of four (eg. g0, g4, g8, . . ., r0, r4, r8, . .) For example, consider ldq 1254(r1), r4 loads the contents of memory location starting at address r1+1254 into register r4 thru r7.

8.2.5.a.ii Store Instructions. Each load instruction has a corresponding store instruction which stores bytes or words from registers to memory.

The store instructions are listed below:

| st ) |        |     |  |

|------|--------|-----|--|

| stob | - 19 y |     |  |

| stos |        |     |  |

| stib |        |     |  |

| stis | reg,   | mem |  |

| stl  |        |     |  |

| stt  |        |     |  |

| stq  |        |     |  |

The stob and stib, and stos and stis instructions store a byte and half-word (16-bit), respectively, from the low ortler bytes of the specified source register. The st, stl, stl, and stq instructions store 4, 8, 12, and 16 bytes, respectively, from successive registers to memory.

For the stl instruction, the specified source register must specify an even numbered register (e.g.  $g0, g2, \ldots, g16$ ). For the stt and stq instructions, the specified source register number must be a multiple of four such as  $g0, g4, g8, \ldots, g16$ .

As an example, the instruction st g4, 2478(g8) stores the word in register g4 into memory location starting at offset 2478+(g8).

8.2.5.a.iii MOVE. The move instructions copy data from a register or group of registers to another register or group of registers. These are listed below:

```

move word - mov

move longword - movl

move triple word - movt

move quad word - movq

```

The movl, movt, and movq instructions specify the source and destination registers as the first (lowest numbered) register of several successive registers. For the movl, these registers must be even numbered such as g0, g2, ..., r0, r2, ... while for the movt and movq instructions, these registers must be an integral multiple of four such as g0, g4, ..., r0, r4, ...

As an example, the instruction movt r4, g8 moves a triple word (three 32-bit) from registers r4, r5, r6 into g8, g9, g10.

8.2.5.a.iv Load Address. Ida mem, reg computes an effective address specified with mem or efa and stores it in the destination, reg. Note that efa represents an effective address based on an addressing mode. This instruction loads a constant longer than 5 bits into a register. To load a register with a constant of 5 bits or less, the move instruction (mov) can be used with a literal as the source operand.

As an example, the instruction, lda 40(g7), g0 computes the effective address specified with 40+(g7) and stores it in g0.

lda 0x845, r4 loads the constant 845H into r4. Note that 0x indicates data in hexadecimal.

8.2.5.a.v Floating-Point Move (Available with 80960SB Only). The following move-real instructions (movr, movrl and movre) are provided for moving real number values between the global and local registers and the floating-point registers:

move real - movr

move longreal - movrl

move extended real - movre

freg/flit, freg

As an example, the following instruction sequence converts a real value in g1 to a long real value, which is stored in g8, g9.

| movr  | g1,  | fp0 |  |

|-------|------|-----|--|

| movrl | fp0, | g8  |  |

The two instructions cpysre and cpyrsre for real extended numbers are explained in the following:

cpysre src1, src2, dst

or

cpyrsre freg/flit freg/flit freg

copies the absolute value of src1 into dst based on the sign of src2.

For cpysre: If src2 is positive then dst  $\leftarrow$  abs(src1); else dst  $\leftarrow$  abs(src1). For cpyrsre: If src2 is negative then dst  $\leftarrow$  abs(src1); else dst  $\leftarrow$  abs(src1)

If the src1, src2, or dst operand specifies one of g0 thru g15 or r0 thru r15, this register (lowest) is the first of three successive registers. Also, this register number must be a multiple of 4 (e.g. g0, g4, g8, . . ).

As an example, the instruction, cpysre g0, fp1, r4 means that the absolute value from g0g1g2 is copied to r4r5r6; the sign from fp1 is copied to r4r5r6.

#### 8.2.5.b Conversion (Available With 80960SB Only)

524

As mentioned before, data can be converted from one length to another by means of the load and store instructions. For example, the ldis instruction loads a short integer from memory to a register and automatically converts the integer from a half word to a full word.

The 80960SB extended instruction set provides instructions to perform conversions between integer and real data types. These instructions are listed below:

```

Convert integer to real , cvtir

Convert long integer to real, cvtilr

Convert real to integer, cvtri

Convert real to long integer, cvtril

Convert truncated real to integer, cvtzri

Convert truncated real to long integer, cvtzril freq/flit,reg

```

For the cvtilr instruction, the source operand specifies the first (lowest numbered) of two successive registers. This register must be even numbered (e.g. g0, g2, g4, . . .).

Converting an integer to long real format requires two instructions as follows:

- 1. cvtir or cvtilr can be used to convert the integer to extended real.

- 2. movrl can then be used to move the value from freg to two global or local registers.

For example the instruction sequence:

cvtir g2, fp0 movrl fp0, g4

converts an integer in g2g3 to real and stores it in fp0; movrl then converts the real value in fp0 to a long real value and stores the result in g4g5.

The cvtril and cvtzril instructions specify the destination operand as the first (lowest numbered) of two successive registers. This register must be even numbered. Also, the nontruncated version of cvtzri and cvtzril instructions round according to the current rounding mode in the Arithmetic Control register. The truncated version always rounds towards zero.

As an example, the following instruction sequence converts a long real value in g8g9 to a long integer in g2g3:

| movrl g8, fp0  | ; | long real source in g8g9 is converted to        |

|----------------|---|-------------------------------------------------|

|                |   | extended-real format in fp0                     |

| cvtril fp0, g2 | ; | extended real value in fp0 is converted to long |

|                | ; | integer in g2g3.                                |

### Synchronous Load and Move

Both the 80960SA and 80960SB include these instructions.

The 80960SA/SB executes the store instructions asynchronously with the memory controller. Once the processor outputs data for storing in main memory, it continues with execution of the next instruction in the program, and assumes that its bus control logic hardware will

complete the operation. The 80960SA/SB includes four special instructions for performing memory operations that perform store and move operations synchronously with memory.

The synchronous load instruction, synld reg/addr, reg copies a word from the source into a register. When this instruction is performed, the processor waits until a condition code bit is set in the arithmetic control register indicating that the operation has been completed, before it begins executing the next instruction. The synld instruction is primarily used to read the contents of the interrupt-control register.

The following instructions

Synmov Synmovl Synmovq

copies one (synmov), two (synmovl) or four (synmovq) words from memory location(s) specified by the source to the destination and waits for completion, including those operations initialed prior to this instruction. The primary function of these instructions is for sending IAC (Inter-agent communication) messages. The primary function of an IAC mechanism is to provide alternative to the external interrupt mechanism to communicate with the processor. Also, certain processor functions such as purging the instruction cache and setting breakpoint registers can only be done with the IAC mechanism. IAC messages are defined in such a way that processors can send them amongst themselves on the bus in a multiprocessor system. For example, a program on processor A can send a message to processor B telling it to flush its instruction cache. Without this facility, processor A would need to generate an interrupt to processor B to tell a program in processor B to flush the cache.

Since IAC messages carry out specific control functions that are not included in instructions, they are useful in single-processor systems. The 80960SA/SB can send an IAC message by writing the message to a special memory-mapped location. The memory mapping only occurs if one of the synchronous load/move instructions is used. A memory write to its specific memory-mapped location using one of these instructions does not cause a bus operation to occur; instead the data are interpreted by the processor as an IAC message and the message causes the same function to be performed by the processor. The function is performed synchronously (i.e. immediately after the synchronous load/move) instruction.

### 8.2.5.c Arithmetic and Logic Operations

8.2.5.c.i Table 8.3 lists 80960SA/SB add, subtract, multiply, divide, and shift instructions.

|                                                                  |   | Instructions and data types |         |      |          |

|------------------------------------------------------------------|---|-----------------------------|---------|------|----------|

| Operations                                                       | 1 | Integer                     | Ordinal | Real | Long Rea |

| add* src1, src2, dst<br>reg/lit reg/lit reg                      |   | addi                        | addo    | addr | addrl    |

| $dst \leftarrow src2 + src1$                                     |   |                             |         |      |          |

| * = i or o or r or rl                                            |   |                             | i in    |      |          |

| sub⁴ src1, src2, dst<br>reg/lit reg/lit reg<br>dst ← src2 - src1 |   | subi                        | subo    | subr | subrl    |

| $dst \leftarrow src_2 - src_1$<br>* = i or o or r or rl          |   |                             |         |      |          |

| mul*src1, src2, dst<br>freg/flit freg/flit freg                  |   | muli                        | mulo    | mulr | mulrl    |

| dst ← src2 * src1                                                |   |                             |         |      |          |

| * = i or o or r or rl                                            |   |                             |         |      |          |

TABLE 8.3 80960SA/SB Add/Subtract/Multiply/Divide/Shift

|                                                                                                                                                                                                                         | 4             | Instructions and data type |      |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------|------|----------|

| Operations                                                                                                                                                                                                              | Integer       | Ordinal                    | Real | Long Rea |

| div* src1, src2, dst<br>dst ← src2 / src1<br>reg/lit reg/lit reg<br>* = i or o or r or rl                                                                                                                               | divi          | divo                       | divr | divrl    |

| No remainder is provided after div*, dst contain quotient.                                                                                                                                                              |               |                            |      |          |

| rem*src1, src2, dst<br>freg/flit freg/flit freg                                                                                                                                                                         | remi          | remo                       | remr | remrl    |

| Performs src2 / src1 and stores the remainder in dst. The sign of<br>the result (if nonzero) is the same as the sign of src2. Calculation<br>of the remainder is done by repeated subtraction.<br>* = i or o or r or rl |               |                            |      |          |

| signed integer modulo:<br>modi srcl, src2, dst<br>reg/lit reg/lit reg<br>dst = src2 - (src2 + src1)*src1                                                                                                                | modi          |                            |      | _        |

| Shift left<br>shl* Len, src, dst<br>reg/lit reg/lit reg                                                                                                                                                                 | shli .        | shlo                       | -    | -        |

| Shifts src left by the number of bits specified in the Len operand<br>and stores result in dst. For values greater than 32, the processor<br>interprets the value as 32.<br>* = i or o                                  |               |                            |      |          |

| Shift right<br>shr* len, src, dst<br>reg/lit reg/lit reg                                                                                                                                                                | shri<br>shrdi | shro                       | -    | - ,      |

| hifts src right by the number of bits indicated with the len<br>operand and stores the result in dst. For values of len greater<br>than 32, the processor interprets the value as 32.<br>= i or di or o                 |               |                            |      |          |

### TABLE 8.3 80960SA/SB Add/Subtract/Multiply/Divide/Shift (continued)

#### Details of Table 8.3

Note the instructions addr/addrl, subr/subrl, roundr/roundrl and sqrtr/sqrtrl are only available with the 80960SB.

For addrl, subrl, mulrl, divrl and remrl instructions, if src1, src2, or dst operand specifies one of the registers from g0 thru g15 or r0 thru r15, the register is the first (lowest numbered) of two successive registers. Also, this register must be even numbered (eg. go, g2, g4, ...).

The binary results from subi and subo are identical except that subi can signal an integer overflow.

For the divi instruction, an integer overflow can be signaled.

The shlo instruction shifts zeros into the least-significant bit and the shro instruction shifts zeros into the most-significant bit.

The shli instruction shifts zeros into the least-significant bit; if the bits shifted out are not the same as the sign bit, an overflow is generated. If overflow occurs, the sign of the result is the same as the sign of the src operand.

The shri instruction performs an arithmetic shift operation by shifting the sign bit in from the most-significant bit.

The shrdi instruction is provided for dividing an integer by a power of 2. With shrdi, one is added to the result if the bits shifted out are non-zero and the operand is negative, which produces the correct result for negative operands.

Remi and modi differ when there is a negative operand: the result of remi has the same sign as the dividend; that of modi has the same sign as the divisor. For example, if  $r^3 = 3$ ,  $r^4 = (-7)$ :

"remi r3, r4, r5" stores (-1) to r5, (-7) = -2 \* 3 + (-1)"modi r3, r4, r5" stores 1 to r5, (-7) = -2 \* 3 - 1

shrdi adds 1 to the result if bits shifted out are non-zero and operand is negative, which produces the correct result for negative operands (if division is desired).

8.2.5.c.ii Rotate Instruction. The operation of the rotate instruction is provided below:

| Instruction                                 | Operation                                                                                                     |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| rotate len, src, dst<br>reg/lit reg/lit reg | dst $\leftarrow$ rotate (len mod 32 (src))<br>copies src to dst and rotates the bits in the dst as follows:   |

|                                             |                                                                                                               |

|                                             |                                                                                                               |

|                                             | The len operand specifies the number that the dst operand<br>is rotated. The len operand can be from 0 to 31. |

| 2                                           | The instruction can also be used to rotate bits to right.                                                     |

8.2.5.c.iii Extended Arithmetic. There are four instructions for double precision integer arithmetic. These are described below:

> Add ordinal with carry, addc src1, src2, dst reg/lit reg/lit reg Operation: dst ← src2 + src1 + carry Flags affected: carry (c) and overflow (v)

Subtract ordinal with carry, subc src1, src2, dst reg/lit reg/lit reg

Operation: dst ← src2 - src1 - carry Flags affected: carry, overflow.

Extended multiply, emul src1, src2, dst reg/lit reg/lit reg

Operation: dst + 1,  $dst \leftarrow src1 * src2$

The result is 64 bits and is stored in two adjacent registers. The dst operand specifies the lower numbered register, which receives the least significant bits of the result. The dst operand must be an even numbered register (ro, r2, r4, ..., or g0, g2, ...).

4. Extended Divide

ediv src1, src2, dst

reg/lit reg/lit reg

Operation: dst ← Remainder of src2/src1

$dst + 1 \leftarrow Quotient of src2/src1$

Scr2 is a long ordinal (64 bits) which is contained in two adjacent registers. Src2 specifies the lower numbered register which contains the least significant bits of the operand. Src2 operand must be an even numbered register. Src1 value is a normal ordinal 32 bits. dst operand must be an even numbered register.

8.2.5.c.iv Floating-Point Arithmetic Instructions (Available with 80960SB Only). In addition to floating-point add (addr/addrl), subtract (subr/subrl), multiply (mulr/mulrl) and divide (divr/divrl) which were already explained, additional floating-point instructions are listed in Table 8.4. Note that in Table 8.4,

| For roundrl,<br>sqrtrl,<br>sinrl,<br>cosrl,<br>tanrl<br>logbnrl,<br>exprl. | If the src or dst operand references a global or local register, this<br>→ register is the first (lowest numbered) of two successive registers.<br>This register must be even numbered (g0, g2,, r0, r2).  |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For atanrl,<br>logrl,<br>logeprl,<br>scalerl,                              | If the src1, src2, or dst references a global or local register, this<br>→ register is the first (lowest numbered) of two successive registers.<br>This register must be even numbered (g0, g2,, r0, r2,). |

|                                                                                                                                                                                                     |                                                                                                                                                                 | Instructions<br>Data Type |           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------|

| Operation                                                                                                                                                                                           |                                                                                                                                                                 | Real                      | Long Real |

| Basic:                                                                                                                                                                                              | round* src, dst<br>freg/lit freg<br>rounds src; to the nearest integral<br>value depending on the rounding<br>mode and stores the result in dst.<br>* = r or rl | roundr                    | roundrl   |

|                                                                                                                                                                                                     | sqrt* src, dst<br>freg/flit freg<br>calculates the square root of src and<br>stores it in dst<br>* = r or rl                                                    | sqrtr                     | sqrtrl    |

| Trigonometric Operation                                                                                                                                                                             |                                                                                                                                                                 |                           |           |

| Calculate the specified trigonometric function<br>of src and stores the result in dst. The src<br>value is in radians. The resulting dst value is                                                   | Sin* src, dst<br>freg/flit freg<br>* = r or rl                                                                                                                  | sinr                      | sinrl     |

| in the range -1 to +1 inclusive for sine and cosine                                                                                                                                                 | cos* src, dst<br>freg/flit freg<br>* = r or rl                                                                                                                  | cosr                      | cosrl     |

| For tangent, the source value is a finite real<br>number between -∞ to +∞                                                                                                                           | tan* src, dst<br>freg/lit freg<br>* = r or rl                                                                                                                   | tanr                      | tanrl     |

| atan calculates arctangent of src2/src1 and<br>stores result in dst. The result is in radians<br>and lies between $-\pi$ to $\pi$ inclusive. The sign<br>of the result is same as the sign of src2. | atani* src1, src2, dst<br>freg/lit freg/lit freg<br>* = r or rl                                                                                                 | atanr                     | atanrl .  |

| Operation (Logarithmic, Exponential, and Scale)                                                                                                                                                     |                                                                                                                                                                 |                           |           |

| Logbn calculates the log;(src) and stores the integral part of this value as real number in dst.                                                                                                    | logbn* src, dst<br>freg/flit freg<br>* = r or rl                                                                                                                | logbñr                    | logbnrl   |

| Log* calculates src2*log2(src1) and stores result<br>in dst. Compute y*log2(x).                                                                                                                     | log*src1, src2, dst<br>freg/flit freg/flit freg<br>* = r or rl                                                                                                  | logr                      | logrl     |

| logep* calculates $rc2*log_2(src1 + 1)$ and stores<br>result in dst. Compute $y*log_2(x + 1)$ .                                                                                                     | logep*src1, src2, dst<br>freg/flit freg/flit freg<br>* = r or rl                                                                                                | logepr                    | logeprl   |

| exp* performs dst $\leftarrow (2^{uc} - 1)$ . The source<br>value must be within -0.5 to +0.5 inclusive.<br>Compute $2^{x} - 1$ .                                                                   | exp* src, dst<br>freg/flit freg                                                                                                                                 | expr                      | exprl     |

| TABLE 8.4 | 80960SB Floating-Point Arithmetic | Instructions Beyond | Add/Subtract/Multiply/Divide |

|-----------|-----------------------------------|---------------------|------------------------------|

|           |                                   |                     |                              |

|                                                                                                                                                  |                                                 |      | Instructions and<br>Data Types |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|--------------------------------|---------|

| Operation (Logarithmic, Exponential and Scale)                                                                                                   |                                                 | Real | Long Real                      |         |

| scale* performs dst ← src2*(2 <sup>src1</sup> ). src1 is<br>integer, src2 and dst are reals. Multiply a<br>floating-point value by a power of 2. | scale*src1, src2, dst<br>reg/lit freg/flit freg |      | scaler                         | scalerl |

8.2.5.c.v Logical, Bit/Bit Field Operations. Table 8.5 lists these instructions:

| Instruction                                   | Operation Performed                    |

|-----------------------------------------------|----------------------------------------|

| and src1, src2, dst<br>reg/lit_reg/lit_reg    | dst ← src2 ∧ src1                      |

| andnot src1, src2, dst<br>reg/lit reg/lit reg | dst $\leftarrow$ src2 $\land$ (src)'   |

| nand src1, src2, dst<br>reg/lit reg/lit reg   | dst ← (src2 ∧ src1)'                   |

| notand src1, src2, dst<br>reg/lit reg/lit reg | dst $\leftarrow$ (src2) ' $\land$ src1 |

| or src1, src2, dst<br>reg/lit reg/lit reg     | $dst \leftarrow src2 \lor src1$        |

| ornot src1, src2, dst<br>reg/lit reg/lit reg  | $dst \leftarrow src2 \lor (src1)'$     |

| nor src1, src2, dst<br>reg/lit reg/lit reg    | $dst \leftarrow (src2 \lor src1)'$     |

| notor src1, src2, dst<br>reg/lit reg/lit reg  | $dst \leftarrow (src2)' \lor src1$     |

| xor src1, src2, dst<br>reg/lit reg/lit reg    | $dst \leftarrow src2 \oplus src1$      |

| xnor src1, src2, dst<br>reg/lit reg/lit reg   | dst $\leftarrow$ (sr2 $\oplus$ src1)'  |

Note that in the above,  $\wedge =$  and,  $\vee =$  or,  $\oplus =$  exclusive or, ' = NOT

Table 8.6 lists bit/bit field instructions.

| Instruction                                      | Operation                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| alterbit bitpos, src, dst<br>reg/lit reg/lit reg | copies the src to dst with one bit altered. The bitpos specifies the bit to be changed<br>and the condition code determines the value the bit is to be changed to. If the<br>condition code is 010 <sub>2</sub> , the selected bit is set to one; if the condition code is 000 <sub>2</sub> ,<br>the bit is cleared to zero. |

| chkbit bitpos, src<br>reg/lit reg/lit            | checks the bit in src specified by bitpos and sets the condition code according to<br>the value found. If the bit is one, the condition code is set to 010 <sub>2</sub> ; if the bit is<br>zero, the condition code is cleared to 000 <sub>2</sub> .                                                                         |

| clrbit bitpos, src, dst<br>reg/lit reg/lit reg   | copies src to dst with the bit specified by bitpos cleared to zero.                                                                                                                                                                                                                                                          |

| notbit bitpos, src, dst<br>reg/lit reg/lit reg   | copies src to dst with the bit specified by bitpos ones complemented.                                                                                                                                                                                                                                                        |

| scanbit src, dst<br>reg/lit reg                  | searches src for most-significant set-bit. If the set-bit is found, its bit number<br>is stored in dst and the condition code is set to 010 <sub>2</sub> . If src is zero, all ones are<br>stored in dst and the condition code is cleared to 000 <sub>2</sub> .                                                             |

| setbit bitpos, src, dst                          | copies src to dst with the bit specified by bitpos set to one.                                                                                                                                                                                                                                                               |

| TABLE 8.6 | Bit/Bit Field | Instructions |

|-----------|---------------|--------------|

|-----------|---------------|--------------|

reg/lit reg/lit reg

| Instruction                                         | Operation                                                                                                                                                                                                                                                      |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sparobit src, dst<br>reg/lit reg                    | searches src for the most-significant clear-bit. If the clear-bit is found, its number<br>is stored in dst and the condition code is set to 0102. If the src value is all ones<br>then all ones are stored in dst and the condition code is cleared to 0003.   |

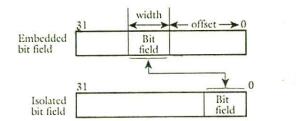

| extract bitpos, len, src/dst<br>reg/lit reg/lit reg | shifts a specified bit field in src/dst right and fills the bits to the left of the shifted bit field with zeros. The bitpos value specifies the least significant bit of the bit field to be shifted and the len value specifies the length of the bit field. |

| modify mask, src, src/dst<br>reg/lit reg/lit reg    | modifies selected bits in src/dst with bits from src. The mask operand selects the bits to be modified: Only the bits set in the mask operand are modified in src/ds src/dst $\leftarrow$ (src $\land$ mask) $\lor$ (src/dst $\land$ (mask)')                  |

| TABLE 8.6 | Bit/Bit Field | Instructions | (continued) | ) |

|-----------|---------------|--------------|-------------|---|

|-----------|---------------|--------------|-------------|---|

8.2.5.c.vi Byte Operations. The scanbyte instruction performs a byte-by-byte comparison of two ordinals to determine if two corresponding bytes are equal.

The format of the scanbyte is as follows:

## scanbyte src1, src2 reg/lit reg/lit

The scanbyte performs a byte-by-byte comparison of src1 and src2 and sets the condition code to  $010_2$  if any two corresponding bytes are equal. If no corresponding bytes are equal, the condition code is cleared to  $000_2$ .

The scanbyte operation is detailed below:

If  $(src1 \land 000000FF_{16}) = (src2 \land 000000FF_{16})$ or  $(src1 \land 0000FF00_{16}) = (src2 \land 0000FF00_{16})$ or  $(src1 \land 00FF0000_{16}) = (src2 \land 00FF0000_{16})$ or  $(src1 \land FF000000_{16}) = (src2 \land FF000000_{16})$

then condition code =  $010_2$ ; else condition code =  $000_2$ .

8.2.5.c.vii Decimal Arithmetic (Available with 80960SB Only). These instructions operate on 32-bit decimal operands that contain an 8-bit ASCII-coded decimal in the least-significant byte.

dmovt src, dst reg reg

daddc src1, src2, dst

reg reg reg

copies src to dst. The least significant byte of src is tested to find whether or not it is a valid ASCII digit  $(30_{16} \text{ thru } 39_{16})$ . If the value is a valid ASCII decimal, the condition code is cleared to  $000_2$ ; otherwise, it is set to  $010_2$ . This instruction is normally used iteratively to validate decimal strings.

adds bits 0 thru 3 of src2 and src1 (with bit 1 of condition code used here as carry bit). The result is stored in bits 0 thru 3 of dst. If there is a carry after addition, bit 1 of condition code is set to one. Bits 4 thru 31 of scr2 are copied to dst unchanged. The instruction assumes that the least significant 4 bits of src1 and src2 are valid BCD digits.

The daddc is intended to be used iteratively to add BCD values in which the least significant four bits of the operands represent valid BCD numbers from 0 to 9.

| dsubc | src1, src2, dst | subtracts bits 0 thru 3 of src1 and src2 as follows: |

|-------|-----------------|------------------------------------------------------|

| *     | reg reg reg     | $dst \leftarrow src2 - src1 - 1 + C.$                |

Bit 1 of condition code is used as C (carry bit). The other characteristics of dsubc are same as the daddc instruction.

The dsubc is intended to be used iteratively to subtract BCD values in which the least significant four bits of the operands represent valid BCD numbers from 0 to 9.

8.2.5.c.viii Atomic Instructions. In multiprocessor systems, a mechanism is required to allow programs to manipulate shared data in an indivisible manner so that when such an operation is underway, another processor cannot perform the same operation. The 80960 includes two instructions called atomic instructions to implement higher-level synchronization mechanisms, such as locks and semaphores.

#### The atmod src, mask, src/dst reg reg/lit reg addr

instruction copies the src/dst value into the memory location specified in src. The src is a register containing the address and thus the name reg addr in the instruction. The bits set in the mask operand select the bits to be modified in memory. The initial value from memory is stored in src/dst.

For example, atmod g1, g3, g6 performs the following:

g1  $\leftarrow$  g1 ANDed by g3 where g1 contains the address of a word in memory. g6  $\leftarrow$  Initial value stored at address g1 in memory.

The read and write of memory are done atomically (i.e. other processors are prevented from accessing the word of memory specified with the src/dst operand until the operation has been completed).

The memory location in src is the address of the first byte (least significant byte) of the word to be modified.

#### The atadd src/dst, src, dst reg reg/lit reg addr

adds the src value (full word) to the value in memory specified by src/dst. The initial value from memory is stored in dst.

The read and write of memory are done atomically. The memory location in src/dst is the address of the first byte (least significant byte) of the word.

The atadd instruction, therefore, adds a value of a word in memory and returns the original value of the word. For example, atadd r2, r4, r9 performs the following:

$r2 \leftarrow r4 + (r2)$  where r2 specifies the address of a word in memory; r9  $\leftarrow$  initial value stored at address r2 in memory.

The atomic read operation waits until the LOCK line on the external bus is not asserted and then asserts the LOCK line and performs the read. The atomic write operation performs a write operation and deasserts the LOCK line. This ensures that another processor cannot perform an atomic read operation between read and write to the word in memory specified with the src/dst operand until the operation has been completed.

#### 8.2.5.d Comparison and Control

Though this 80960SA/SB RISC processor has a condition code register, it is not affected by most arithmetic and movement instructions. An explicit comparison instruction is needed for

conditional branches. This feature has its advantage. Between the instruction that sets condition code and the instruction that performs conditional branching, many independent arithmetic operations can be inserted. That will increase the pipeline efficiency. Arithmetic instructions that change condition codes are: addc, subc, dmovt, daddc, dsubc.

8.2.5.d.i Comparison. These instructions compare integer (signed numbers) and ordinals (unsigned numbers):

Compare Integer (cmpi)/Ordinal (cmpo) cmpi src1, src2 or reg/lit reg/lit cmpo

compares src2 and src1 values and sets the condition code according to the following:

| Condition Code |     | Comparison  |

|----------------|-----|-------------|

|                | 100 | src1 < src2 |

|                | 010 | srcl = src2 |

|                | 001 | src1 > src2 |

Compare and Increment Integer(cmpinci)/Ordinal (cmpinco) cmpinci src1, src2, dst or reg/lit reg/lit reg cmpinco

compares src2 and src1 values and sets the condition code according to the results of the comparison. Src2 is then incremented by one and the result is stored in dst.

The condition codes are affected by the comparison result in exactly the same way as the cmpi/cmpo.

Conditional Compare Integer (concmpi)/Ordinal (concmpo) concmpi src1, src2 or reg/lit reg/lit concmpo

compares src2 and src1 value if bit 2 of the condition code is not set. If the comparison is performed, the condition code is set according to the comparison results in the same way as cmpi/cmpo.

Compare and Decrement Integer (cmpdeci)/Ordinal (cmpdeco) cmpdeci rc1, src2, dst or reg/lit reg/lit reg cmpdeco

compares src2 and src1 values and sets the condition code according to the comparison results in the same way as cmpi/cmpo. The src2 is then decremented by one and the result is stored in dst.

The following instructions are for real and long real floating-point numbers (available with only 80960SB microprocessor):

Compare real (cmpr/longreal (cmprl)) compr src1, src or freg/flit freg/flit comprl

| Condition Code | Comparison                      |

|----------------|---------------------------------|

| 100            | src1 < src2                     |

| 010            | src1 = src2                     |

| 001            | src1 > src2                     |

| 000            | if either src1 or scr2 is a NaN |

compares src2 with src1 and sets the condition code according to the result as follows:

cmpr/cmprl clears the condition code flags to  $000_2$  for the unordered condition. Note that the unordered relationship is true when at least one of the two values compared is a NaN.

Compare Ordered Real (cmpor)/Ordered Long Real (cmpor) cmpor src1, src2 or freg/flit freg/flit cmporl

compares src2 and src1 and sets the condition code in the same way as cmpr/cmprl.

Compor/comporl clears the condition code to  $000_2$  and an invalid-operation exception is signaled for the unordered condition. Note that the unordered condition is true when at least one of the two values being compared is a NaN.

Classify Real (cassr)/Long Real (classrl) classr src or freg/flit classrl

checks classification of real number in src and stores the class in arithmetic-status bits (3 through 6) of the arithmetic controls as follows:

| A Status | Classification       |

|----------|----------------------|

| S000     | Zero                 |

| S001     | Denormalized number  |

| S010     | Normal finite number |

| S011     | Infinity             |

| S100     | Quiet NaN            |

| S101     | Signaling NaN        |

| S110     | Reserved operand     |

The S bit is set to the sign of the src operand.

For cmprl and cmporl and classrl instructions, if src1 or src2 for cmprl/cmporl or src for calssrl specifies a global or local register, this register is the first (lowest numbered) of two successive registers. Also, this register must be even numbered.

8.2.5.d.ii Control Instructions. The 80960SA/SB include the following unconditional branch instructions:

Branch (b)/Branch Extended (bx) b targ or bx targ disp mem

branches to the instruction specified with the targ operand.

For the b instruction the range of targ operand is from  $-2^{23}$  to  $(2^{23} - 4)$  bytes from the current IP. For bx, the targ can be farther than  $-2^{23}$  to  $(2^{23} - 4)$  bytes for the current IP. Also, since the

targ operand for bx is a memory type, full range of addressing words including register indirect mode can be used.

Branch and Link (bal)/Link Extended (balx) bal targ or balx targ, dst disp mem reg

stores the address of the next instruction (next IP value) in a register and branches to the instruction specified with the targ operand. These instructions are intended for calling leaf procedures (procedures that do not call other procedures). Using the b or bx instruction, the leaf procedure can branch to the IP saved by bal or balx.

For bal, the address of the next instruction is saved in g14. The range of targ is from  $-2^{23}$  to  $2^{23} - 4$ .

The balx performs the same operation as the bal except that the address of the next instruction is stored in dst, allowing it to be stored in any available register. The range of targ can be farther  $-2^{23}$  to  $(2^{23} - 4)$  bytes from the current IP.

#### Compare and Branch

These instructions compare two operands, then branch (or not) according to the result:

| Compar           | e                        |                          |

|------------------|--------------------------|--------------------------|

| Branch If        | Integer (Signed)         | Ordinal (Unsigned)       |

| Equal            | cmpibe src1, src2, targ  | cmpobe src1, src2, targ  |

| Not Equal        | cmpibne src1, src2, targ | empobne src1, src2, targ |

| Less             | cmpibl src1, src2, targ  | cmpobl si c1, src2, targ |

| Less or Equal    | cmpible src1, src2, targ | cmpoble src1, src2, targ |

| Greater          | cmpibg src1, src2, targ  | cmpobg src1, src2, targ  |

| Greater or Equal | cmpibge src1, src2, targ | cmpobge src1, src2, targ |

| Ordered          | cmpibo src1, src2, targ  | cmpobo src1, src2, targ  |

| Unordered        | cmpibno src1, src2, targ | cmpobno src1, src2, targ |

In the above instructions, src1 = reg/lit, src2 = reg, and targ = disp. These instructions compare src1 and src2, and set the condition code based on the result. If the AND of the condition code and the mask part of the instruction is not zero, the processor branches to targ; otherwise, the processor goes to the next instruction. Note that the condition code  $000_2$  indicates no condition and is the unordered condition while condition code  $= 111_2$  is the 'ordered' condition. The terms 'ordered' and 'unordered' are used when comparing two floating-point numbers. If, when comparing two floating-point values, one of the values is a NaN (Not a number), the relationship is said to be 'unordered'; otherwise, the releationship is 'ordered'.

#### Bit Instructions:

Check Bit and Branch if SET, bbs bitpos, src, targ Check Bit and Branch if Clear, bbc reg/lit reg disp

bbs and bbc instructions check the bit in src-specified by bitpos and set the condition code according to the value. The processor then branches to targ according to the condition.

#### **Test Condition Codes**

These instructions cause a TRUE (1) to be stored in a destination register if the condition code matches. Otherwise, a FALSE (0) is stored.

teste dst Test if Equal testl dst Test if Less testne dst Test if Not Equal testg dst Test if Greater

testle dst Test if Less or Equal testo dst Test Ordered testge dst Test if Greater or Equal testno dst Test if Unordered

In the above, dst = reg.

#### **Conditional Fault**

These instructions permit a fault to be generated explicitly according to the state of the condition-code bits:

| faulte  | Fault if Equal         | faultne | Fault if Not Equal        |

|---------|------------------------|---------|---------------------------|

| faultl  | Fault if Less          | faultg  | Fault if Greater          |

| faultle | Fault if Less or Equal | faultge | Fault if Greater or Equal |

| faulto  | Fault Ordered          | faultno | Fault if Unordered        |

#### Call and Return

The processor offers an on-chip call return mechanism for making procedure calls to local procedures and kernel procedures. These instructions support that mechanism:

| call targ  | Calls where targ = disp           |

|------------|-----------------------------------|

| callx targ | Calls Extended where targ = mem   |

| calls targ | Calls System where targ = reg/lit |

| ret        | Return                            |

The call and callx instructions call local procedures. They differ only in addressing mode. The processor will allocate a new set of local registers and a new stack frame for the called procedure. The calls instruction operates similarly, except that it gets its target procedure address from the system procedure table. Depending on the type of entry being pointed to in the procedure table, the calls instruction can cause a supervisor procedure call to be executed.

The ret instruction performs a return from a called procedure to a calling procedure. The same instruction is used to return from local and supervisor calls and from implicit calls to interrupt and fault handlers. The processor takes care of all the details.

#### Debug

The processor supports debugging and program tracing. These are the debugging tools:

modte Modify Trace Control

mark Mark — generates a breakpoint trace event if breakpoint trace mode flag is enabled.

fmark Force Mark — generates a breakpoint trace event regardless of the breakpoint trace mode flag.

#### **Processor Management**

The processor provides several instructions for use in controlling processor-related functions.

modpc src, mask, src/dst reg/lit reg/lit reg flushreg stores the contents of src/dst in the process control register, with the bits set in the mask modified. The src/dst then contains the initial value of the process control register. The src/dst is a dummy operand and must be set equal to the mask operand. The processor must be in the supervisor mode for executing this instruction. copies each local register set except the current set to its associated stack-frame in memory and marks them as invalid, meaning that they will be reloaded from memory if and when they become the current local register set.

modac mask, src, dst

places the contents of src in the Arithmetic control register with the bits set in the mask modified register. The dst then contains the initial value of the Arithmetic controls.

reg/lit reg/lit reg

**Conditional Branches:**

| be  | Branch if Equal         | bne | Branch if Not Equal        |

|-----|-------------------------|-----|----------------------------|

| Ы   | Branch if Less          | bg  | Branch if Greater          |

| ble | Branch if Less or Equal | bge | Branch if Greater or Equal |

| bo  | Branch if Ordered       | bno | Branch if Unordered        |

These instructions are single-operand with the operand "targ" or "disp" defined in the same way as bal.

#### Value of $\pi$

The 80960SA/SB uses the value 41490FDA<sub>16</sub> for  $\pi$ . The details of this computation are given in Intel i960SA/SB Microprocessor SA/SB reference manual. As an example,  $\pi$  can be located into a register such as r4 by using lda 0X41490fda, r4 where ox is used to represent hexadecimal number by the 80960SA/SB assembler.

#### 80960 Assembler

The 80960 assembler uses the first operand of a two operand instruction as the source operand and the second operand as the destination. The assembler directive # is used before a comment. 0X before an immediate number is used to represent a hex number.

### Example 8.1

Identify the addressing modes for the following 80960 instructions:

- i) ldl 4816(r3),g4

- ii) st r3,34(r8)[r4\*4]

#### Solution

| i)  | source            | destination                    |

|-----|-------------------|--------------------------------|

|     | register indirect | register                       |

| ii) | source            | destination                    |

|     | register          | register indirect with         |

|     |                   | scaled index and displacement. |

### Example 8.2

Determine whether the following 80960 instructions are valid or invalid. Comment.

- i) ldq (g8) [g9], r2

- ii) stl 46, 52(r5)

#### Solution

- i) Not valid since for ldq instruction, the destination must specify a register number that is multiple of 4 such as r0, r4, r8, ..., g0, g4, g8, .... Since register r2 is not a multiple of 4, the instruction is invalid.

- ii) Valid since for stl, the source must be an even numbered register which is r6 in this case.

### Example 8.3

Write an 80960 instruction sequence to read 32-bit elements 5, 6, and 7 from a table stored in memory into register r1, r2, and r3 respectively. Assume that register r5 points to the starting address containing element 0 (32-bit data) of the table.

Solution

ldt 5(r5), r8 #r8 ← ((r5+5)) #r9 ← ((r5+6)) #r10 ← ((r5+7)) mov r8, r1 #r1 ← r8 mov r9, r2 #r2 ← r9 mov r10, r3 #r3 ← r10.

### Example 8.4

Write an assembly language program in 80960 assembly language to add two 64-bit numbers. Assume that the two 64-bit numbers are stored in r1, r0 and r3, r2 respectively. Store the 64-bit result in r0, r1.

Solution

```

cmpo 1, 0 # clears bit 1(carry bit)

# of the condition code register

addc r0,r2,r0 # r0 \leftarrow r2+r0+carry bit

addc r1,r3,r1 # r1 \leftarrow r3+r1+carry bit

finish b finish # halt

```

### Example 8.5

Write an 80960 assembly language program to perform the following operation:

(A/B) + C \* D

where A, B, C, D are stored in r0, r1, r2, r3 as 32-bit integers. Assume C\*D generates 32-bit product. Discard remainder of A/B. Store the 32-bit result in r4.

```

Solution

```

|        | divi | r1,  | r0, | r4 | # | r4  | -  | r0, | 'r1 |    |  |

|--------|------|------|-----|----|---|-----|----|-----|-----|----|--|

|        | muli | r2,  | r3, | r5 | # | r5  | ←  | r2' | *r3 |    |  |

|        | addi | r5,  | r4  |    | # | r4  | -  | r4  | +   | r5 |  |

| finish | b fi | nish |     |    | # | sto | go |     |     |    |  |

### Example 8.6

Write a program in 80960 assembly language that copies bits 3-6 of register r1 into bits 31-28 of register r2.

#### Solution

extract 3, 4, r1 # r1 = 000. . . 000aaaa shlo 28, r1, r1 # r1 = aaaa000. . . 000 538

Microprocessors and Microcomputer-Based System Design, 2nd Edition

### Example 8.7

Write a program in 80960 assembly language to branch to a label 'start' if the 32-bit operand in register g2 is not a finite number.

#### Solution

|        | classr g2                |    |                               |

|--------|--------------------------|----|-------------------------------|

|        | modac 0, 0, g1           | #  | place condition code in g1    |

|        |                          | #  | arithmetic status in bits     |

|        |                          | #  | 3-6 of g1                     |

|        | shro 3, g1, g1           | #  | move arith status in bits     |

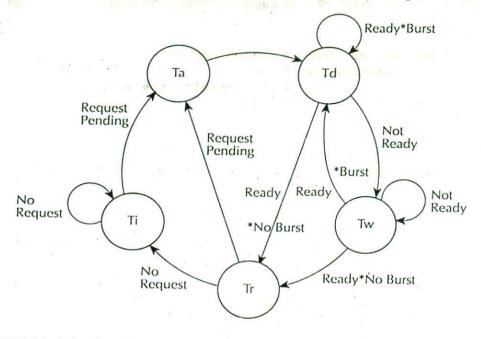

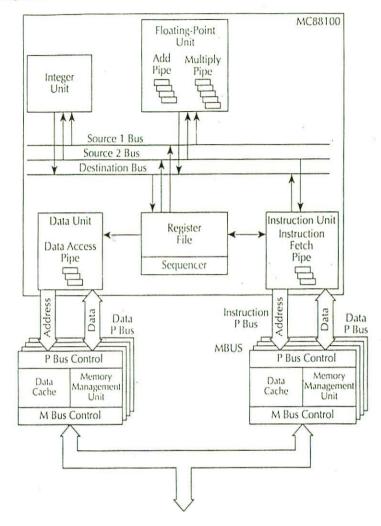

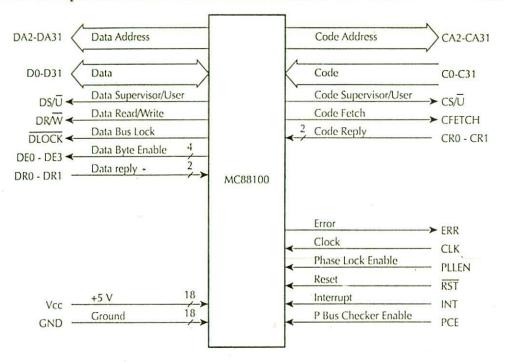

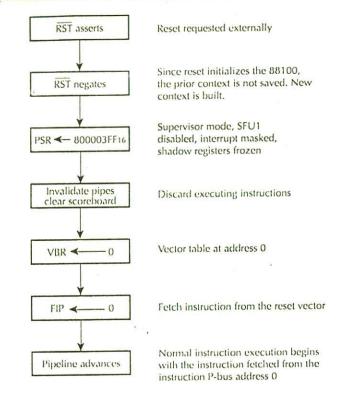

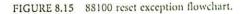

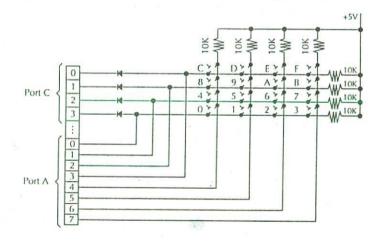

|        | *                        | #  | 0-3 of g1                     |