# Practical aspects and testability

Is it not strange that desire should so many years outlive performance? Shakespeare: King Henry IV

# Objectives

The chapter is intended to round off and summarize much of the preceding text and to discuss some of the practical realities the designer must face. The problems of communication again receive close attention and are illustrated in the context of the 4-bit data path design.

The chapter also includes a section headed 'Ground rules for successful design' and the reader will find that most of the rules, tabulated data and performance parameters are grouped together consecutively in this section. The question of noise margins and other relevant aspects, such as CIF code and CAD tools, are also discussed.

The second half of the chapter is entirely devoted to the very important subject of testability, which must always be a key design requirement for systems of any size.

# 10.1 Some thoughts on performance

Two important parameters (other than 'does it work at all?') are speed and power dissipation. These factors are generally interrelated; power dissipation and area are also interrelated in MOS technology.

Take, for example, the simple case of an nMOS 8:1 inverter which may be set out with a minimum feature size pull-down transistor (i.e.  $2\lambda \times 2\lambda$  pull-down gate area and a minimum width  $16\lambda \log \times 2\lambda$  wide pull-up channel) giving a total resistance from  $V_{DD}$  to GND of 90 k $\Omega$ . The maximum power dissipation for this particular design will thus be

$$\frac{(5 \text{ V})^2}{90 \text{ k}\Omega} = 0.278 \text{ mW}$$

An alternative form of 8:1 inverter is to use a pull-down geometry  $2\lambda$  long and  $6\lambda$  wide with a  $6\lambda$  long,  $2\lambda$  wide pull-up channel giving a  $V_{DD}$  to GND resistance of 33.3 k $\Omega$  and a consequent maximum power dissipation of

$$\frac{(5 \text{ V})^2}{33.3 \text{ k}\Omega} = 0.744 \text{ mW}$$

that is, about three times the dissipation. However, comparing the total transistor areas for each case we have, in the first case,  $2\lambda \times 2\lambda + 16\lambda \times 2\lambda = 36\lambda^2$  area and, in the second case,  $2\lambda \times 6\lambda + 6\lambda \times 2\lambda = 24\lambda^2$ . In other words, the 3:1 (approximate) reduction in power dissipation is at the expense of a 50% increase in transistor area.

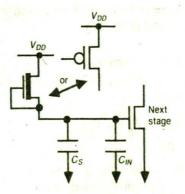

Now consider the aspect of speed (or circuit delays), and take the simple case of one 8:1 inverter driving another similar inverter. The longest delays will occur when the output of the first stage is changing from logic 0 (Lo) to logic 1 (Hi), that is, the  $\Delta$  transition of the output, and the capacitances associated with the output and the input of the next stage must charge through the pull-up resistance of the first stage as in Figure 10–1. Asymmetry is also present in CMOS devices. It is also obvious that during the complementary  $\nabla$  transition the same capacitances must be discharged through the pull-down transistor of the first stage.

For the minimum pull-down feature size nMOS 8:1 inverter, for example

$$R_{p.u} = 8R_s$$

$$R_{p.d} = 1R_s$$

$$C_{IN} = 1\Box C_g$$

allow stray and wiring capacitances

$$C_s = 4 \Box C_s$$

(say)

Then

$\Delta$  transition delay =  $8R_s \times 5\Box C_s = 40\tau$

and

$$\nabla$$

transition delay =  $1R_s \times 5 \Box C_s = 5\tau$

For the alternative 8:1 inverter design discussed earlier, and allowing the same stray and wiring capacitances

$$\Delta$$

transition delay =  $3R_s \times 7\Box C_s = 21\tau$

and

$$\nabla$$

transition delay =  $\frac{1}{3}R_{c} \times 7\Box C_{c} = 2\frac{1}{3}\tau$

Thus, it may be seen that a speed-up factor of about 2:1 in this case is bought at the expense of a 3:1 increase in power consumption but has the bonus of reducing area by a factor of 2:3. Similar considerations apply to the switching energy of CMOS circuits.

Therefore, as in most engineering situations, there are trade-offs to be made, and it is essential that the would-be designer have a good fundamental understanding of the discipline to be able to make sound decisions.

But remember, in the end there will always be limits imposed by the technology and some specifications will be impossible to meet.

# 10.1.1 Optimization of nMOS and CMOS inverters\*

The approximate calculations presented here should be useful from a qualitative point of view and are intended to give the reader some appreciation of basic CMOS and nMOS circuit optimization problems.

<sup>\*</sup> The authors are indebted to Professor K. S. Trivedi of Duke University for providing this material on inverter optimization.

For a more rigorous treatment of circuit optimization methods, refer to the articles cited at the end of the chapter.

## 10.1.1.1 The CMOS inverter

The area of a basic CMOS inverter is proportional to the total area occupied by the p- and n-devices.

$$A \propto (W_p L_p + W_n L_n)$$

where

$W_p$  = width of the p-device  $L_p$  = length of the p-device  $W_n$  = width of the n-device  $L_n$  = length of the n-device

Minimum area can be achieved by choosing minimum dimensions for  $W_p$ ,  $L_p$ ,  $W_n$  and  $L_n$ , that is

$$W_p = L_p = W_n = L_n = 2\lambda$$

(minimum)

Hence

$$\frac{W_p}{W_n} = 1$$

Switching power dissipation,  $P_{sd}$ , can be approximated by  $C_1 V_{DD}^2 f$  where

$C_L$  = load capacitance at the inverter output  $V_{DD}$  = power supply voltage f = frequency of switching

For fixed  $V_{DD}$  and f, minimizing  $P_{sd}$  requires minimizing  $C_L$  which can be achieved by minimizing the area A since  $C_L$  is proportional to the gate areas comprising A.

Asymmetry in rise and fall times,  $t_r$  and  $t_f$  (transition times between 10% and 90% logic levels), can be equalized by using  $\beta_n = \beta_p$ . (Notice that  $t_r$  and  $t_f$  are proportional to the average resistance of the device which is approximately given

by  $\overline{\beta V_{DD}}$  where  $\beta = \beta_n$  or  $\beta_p$ .) This requires that

$$\frac{W_p}{L_p} = \left(\frac{\mu_n}{\mu_p}\right) \frac{W_n}{L_n}$$

to compensate for the lower hole mobility  $\mu_p$ , compared to electron mobility  $\mu_n$

Assuming

$$L_p = L_n = 2\lambda$$

,  $\frac{\mu_n}{\mu_p} \stackrel{:}{=} 2$ , we require  $\frac{W_p}{W_n} \stackrel{:}{=} 2$ . This yields  $t_r = t_f$ .

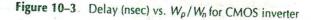

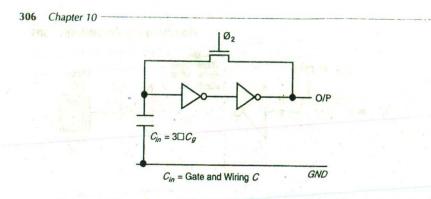

#### Figure 10-2 Inverter pair

Note that equalizing rise and fall times is not possible in nMOS or pseudonMOS inverters because of the ratio requirement.

Asymmetry in noise margins,  $NM_H$  and  $NM_L$ , can be equalized by choosing

$\beta_n = \beta_p$  and hence  $\frac{W_p}{W_p} \doteq 2$  for  $L_p = L_n$ . This yields  $NM_H = NM_L$ . (See Figure 10-4(b).)

Basic inverter pair delay - Consider a basic inverter pair shown in Figure 10-2 where  $C_L$  is the capacitive load driven by the two identical inverters, inverter pair delay  $D(=t_r + t_f)$  is proportional to  $(R_p + R_n)C_L$  where  $R_p = 2/(\beta_p V_{DD})$  and  $R_n = 2/(\beta_n V_{DD})$  are the average resistances of the p- and n-transistors respectively. Also

$$C_L = C_E + (W_p L_p + W_n L_n) C_g$$

where

$C_E$  = lumped parasitic capacitance  $C_{p} =$ gate capacitance per unit area

Hence

$$D = D_0 \left[ \left( \frac{2}{\beta_p V_{DD}} + \frac{2}{\beta_n V_{DD}} \right) (C_E + (W_p L_p + W_n L_n) C_g) \right]$$

where  $D_0$  is a constant of proportionality. Assuming  $\frac{\mu_n}{\mu_n} = 2$

$$D = D_0 \left[ C_E \left( \frac{2L_{\gamma}}{W_p} + \frac{L_n}{W_n} \right) + C_g \left( 2L_p^2 + 2L_p L_n \frac{W_n}{W_p} + L_p L_n \frac{W_p}{W_n} + L_n^2 \right) \right]$$

Since D increases with  $L_n$  and  $L_p$ , for minimum D choose  $L_n = L_p = 2\lambda$  (minimum). Minimizing D with respect to  $W_p$  yields a solution

$$W_p / W_n = \sqrt{2} \left[ 1 + \frac{C_E}{C_g L_n W_n} \right]^{1/2}$$

W  $/W_n = \sqrt{2}$  for  $C_E << C_g L_n W_n$  (normal case)

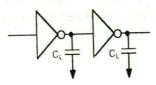

However, D does not vary significantly with  $W_p/W_n$  in the range  $1 \le \frac{W_p}{W_n} \le 2$  (see Figure 10–3). Hence simultaneous optimization of various parameters mentioned above seems to be easily achievable in the CMOS inverter, without greatly increasing the delay D.

Notes:  $L_p = L_n = 2\lambda = 5 \ \mu m$ Gate capacitance  $C_g = 4 \times 10^{-4} \ pF/\mu m^2$  $C_E = 4 \times 10^{-3} \ pF$

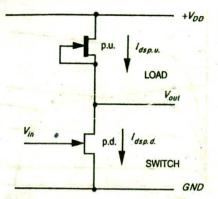

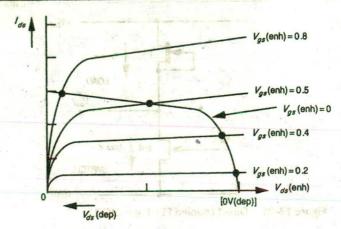

# 10.1.1.2 nMOS inverter

Let  $Z_{p.u.}/Z_{p.d.} = \frac{L_{p.u.}W_{p.d.}}{W_{p.u.}L_{p.d.}} = k$  where the subscripts *p.u.* and *p.d.* refer to the pull-up and pull-down transistors respectively. Then area

$$A = A_0(L_{p,d.} W_{p,d.} + L_{p,u.} W_{p,u.})$$

$$= A_0 \left( L_{p,d.} W_{p,d.} + k W_{p,u.}^2 \frac{L_{p,d.}}{W_{p,d.}} \right)$$

where  $A_0$  is a constant of proportionality. For a fixed k, to achieve minimum A, we need  $L_{p.d.} = W_{p.u.} = 2\lambda$ . Minimizing A with respect to  $W_{p.d.}$  yields a solution  $W_{p.d.} \sqrt{k}W_{p.u.} = \sqrt{k}2\lambda$ . Hence, using  $Z_{p.u.}/Z_{p.d.} = k$ , we obtain

Practical aspects and testability 291

$$L_{p.u.} = \sqrt{k} \cdot L_{p.d.} = \sqrt{k} \cdot 2\lambda$$

This implies  $Z_{p,\mu} = \sqrt{k}$  and  $Z_{p,d} = 1/\sqrt{k}$ . Giving

Minimum area =  $8A_0\lambda^2\sqrt{k}$

Static power dissipation,  $P_d = P_0 \frac{V_{DD}^2}{(k+1)Z_{p,d}}$ , where  $P_0$  is a constant of

proportionality — for fixed k and  $V_{DD}$ ,  $P_d$  is minimized by choosing as large a  $Z_{p,d}$  as possible. However, a large  $Z_{p,d}$  requires a large a  $Z_{p,u}$  ( $Z_{p,u} = kZ_{p,d}$ ), and hence the delay D of the inverter pair increases. One has to choose the maximum  $Z_{p,d}$  possible for a given maximum allowed delay D.

If we use  $Z_{p,d} = 1$  with  $L_{p,d} = W_{p,d} = 2\lambda$ , and  $Z_{p,u} = k$  with  $L_{p,u} = 2k\lambda$  and  $W_{p,u} = 2\lambda$ , we obtain

$$P_{d} = \frac{P_{0}V_{DD}^{2}}{(k+1)}$$

$$A = 4A_{0}(k+1)\lambda^{2}$$

Inverter pair delay - Proceeding in a similar manner to the CMOS case

$$C_{L} = C_{E} + C_{g} W_{p,d} L_{p,d},$$

$$D = t_{r} + t_{f} = D_{0} (Z_{p,d} + Z_{p,u}) C_{L}$$

$$= D_{0} [Z_{p,d} C_{E} (1 + k) + C_{o} (1 + k) L_{p,d}^{2}]$$

To minimize D:

- 1. Choose minimum  $L_{p,d} = 2\lambda$ .

- 2. For maximum  $W_{p,d}$ , choose  $L_{p,u} = 2\lambda$ , as  $W_{p,d} = 2k\lambda \frac{W_{p,u}}{L_{p,u}}$  which yields  $W_{p,d} = kW_{p,u}$ .

Choosing large  $W_{p,d}$  to minimize D increases A. Hence for a given area  $A(=W_{p,d}L_{p,d}+W_{p,u}L_{p,u})$  with  $L_{p,d}=L_{p,u}=2\lambda$ , we must have

$$W_{p.u.} = \frac{A}{2\lambda(k+1)} \qquad \qquad W_{p.d.} = \frac{kA}{2\lambda(k+1)}$$

With  $W_{p.u.} = 2\lambda$ , we have  $W_{p.d.} = k2\lambda$ . Hence  $Z_{p.u.} = 1$  and  $Z_{p.d.} = 1/k$  for minimum D.

Minimum  $D = D_0(1 + k) (C_E/k + 4\lambda^2 C_e)$

Table 10–1 shows the summary of optimization of the three parameters, D, A and  $P_d$ . Notice that the solution for minimum power dissipation also gives the lowest power delay product among the three designs.

#### 292 Chapter 10 -

| Table 10-1 Optimum parameters for | r nMOS | inverters |

|-----------------------------------|--------|-----------|

|-----------------------------------|--------|-----------|

|                        | L <sub>p.d.</sub>  | W <sub>p.d.</sub>  | Z <sub>p.d.</sub>                         | L <sub>р.и.</sub>    | W <sub>p.u.</sub>        | Z <sub>p.4</sub> |

|------------------------|--------------------|--------------------|-------------------------------------------|----------------------|--------------------------|------------------|

| Minimum D              | 2λ                 | 2kl                | 1/k                                       | 2λ                   | 2λ                       | 1                |

| Minimum A              | 2λ                 | $2\lambda\sqrt{k}$ | $1/\sqrt{k}$                              | $2\lambda\sqrt{k}$   | 2λ                       | $\sqrt{k}$       |

| Minimum P <sub>d</sub> | 2λ                 | 2λ                 | 1                                         | 2Xk                  | 2λ                       | k                |

|                        | A/A <sub>0</sub>   | C.1. 12            | DID                                       | ol - dia<br>Idd stor | $P_d/(P_0)$              | $V_{DD}^2$ )     |

| Minimum D              | 4λ²(k +            | 1) (1              | $+k)(C_E/k$                               | $+ 4\lambda^2 C_g$ ) | $\frac{k}{k+1}$          | 1                |

| Minimum A              | 8λ <sup>2</sup> √/ | Ē (1               | $(1+k)\left(\frac{C_E}{\sqrt{k}}+\right)$ | $4\lambda^2 C_g$     | $\frac{\sqrt{k}}{(k+1)}$ |                  |

| Minimum $P_d$          | $4\lambda^2(k +$   | 1) (               | $(C_{E} + k) = (C_{E} + k)$               | $4\lambda^2 C_g)$    | $\frac{1}{(k+1)}$        | 1)               |

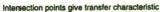

# 10.1.2 Noise margins

Noise margins have been mentioned in the preceding section and it is appropriate now to consider this factor in more detail.

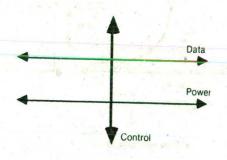

Noise margins are a measure of a logic circuit's tolerance of noise voltages in either of the two logic states; in other words, by how much the input voltage can change without disturbing the present logic output state. In order to examine this, it is convenient to consider a pair of inverters (nMOS or CMOS) and derive the noise margins for signals applied to the input of the second inverter, inverter 2, which is driven from the output of a similar inverter, inverter 1, as in Figure 10-4(a).

Referring now to Figure 10-4(b), we see the transfer characteristics ( $V_{out}$  vs.  $V_{in}$ ) for a pair of CMOS inverters set out in such a way that the output voltage of inverter 1 is applied as the input voltage to inverter 2. By first considering the point at which output 1 starts to enter the transition region (the unity gain point A) and calling this voltage  $V_{OH min}$  and then considering the input voltage level  $V_{IH min}$  (point B) at which the transition of the output of inverter 2 commences, we are able to define the high level noise margin of inverter 2 as  $NM_H$  where

$NM_{H} = V_{OHmin} - V_{IHmin}$  (a positive voltage)

Similarly, a consideration of the low logic level conditions gives

$NM_L = V_{OLmax} - V_{ILmax}$  (a negative voltage)

Note: A and B, C and D are unity gain points.

Figure 10–4 Inverter noise margins

A similar approach will yield noise margins for the nMOS inverter as shown in Figure 10-4(c). It may be seen that generally the CMOS inverter will have better noise margins than the nMOS inverter, particularly for the low condition.

In both cases, symmetry about  $V_{inv}$  is assumed (where  $V_{inv}$  is the point at which  $V_{out} = V_{in} = V_{DD}/2$ ). This assumes that  $\beta_p = \beta_n$  for CMOS and that the correct ratio of  $Z_{p.u}$  to  $Z_{p.d}$  has been observed for nMOS.

Changes in the  $\beta_n/\beta_p$  ratio for CMOS or to the  $Z_{p,u}/Z_{p,d}$  ratio for nMOS will result in a shift in the  $V_{out}$  vs.  $V_{in}$  characteristics (see Figures 2–7 for nMOS and 2–15 for CMOS) and consequent degradation of one or the other noise margin in each case.

Thus the effect of ratios on noise margins performance must be taken into account in design.

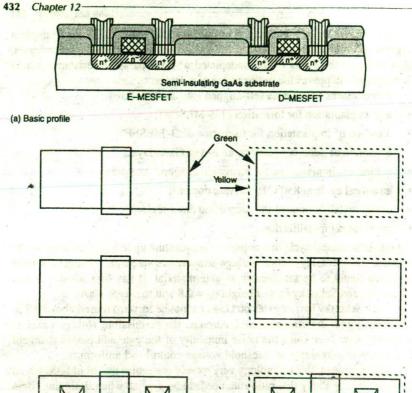

# 10.2 Further thoughts on floor plans/layout

In considering the layout of the four-bit data path used earlier as a design exercise, we could have waited until we knew the minimum size and disposition of connections to each functional block in order to finalize the floor plan. Indeed, this is a possible approach if communications will allow. Quite accurate floor plans can be set out at an early stage if a library of properly dimensioned and characterized elements/ cells is available to the designer.

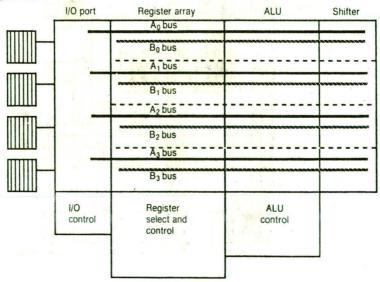

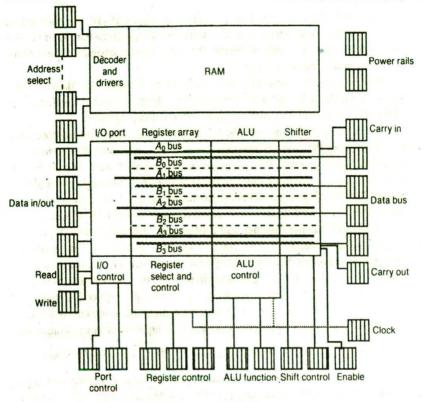

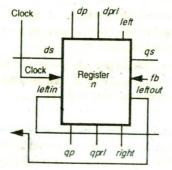

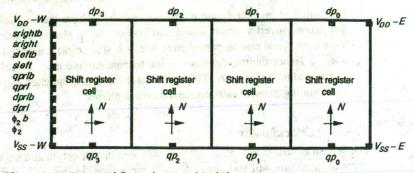

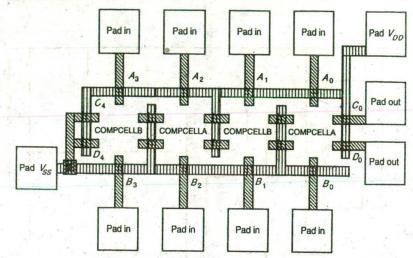

However, a better approach is to draw up quite specific floor plans at the outset and then design/configure the subsystems to conform to the required floor plan. This approach is more general than the one we have used so far. The same 4-bit processor (Figure 8-1) will be used to illustrate the method and considerations involved.

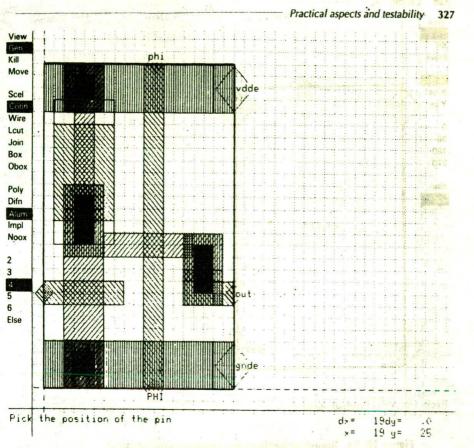

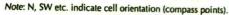

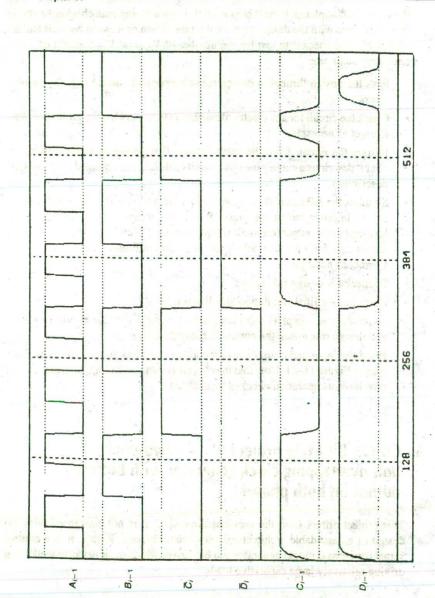

First (as before) determine an *overall strategy* (perhaps as suggested in Figure 10–5) and then use this to determine the best relative disposition of subsystems in light of data flow and control paths through the system. For the 4-bit data path, a suitable layout is shown in Figure 10–6.

Figure 10–5 A communications strategy

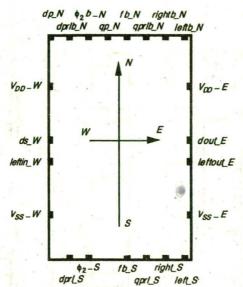

When approached this way, a reasonably well thought-out floor plan can be developed before knowing any real detail of the subsystem/block areas. In the event, features of individual subsystems (Figures 7–8, 7–9 with 7–10, 8–11(b), and 9–15 with 9–17) will, in general, dominate the overall layout and other blocks may then be stretched and/or reconfigured as necessary to conform with the dominant features.

In order to do so it is essential to set out clearly the way in which data will flow on the buses. In this case:

- 1. Floating bus lines are envisaged.

- 2. All read and write operations are coincident with  $\phi_1$ .

- 3. Bus A connects the I/O port to the register array and carries one operand  $(A_k)$  from the registers to the adder. It will also be used to carry the output of the shifter back to the register array (and I/O port). Bus A is therefore bidirectional.

- 4. Bus B connects the register array with the other input  $(B_k)$  of the adder and may also be used to carry the sum output  $(S_k)$  from the adder to the input of the shifter. Bus B is unidirectional.

Taking the subsystems of the 4-bit data path example (Figures 7–9 with 7–10, 8–11(b), and 9–15 with 9–18), one of the main features is the bus spacing, that is, the spacing between buses  $A_n$  and  $B_n$  and between  $A_n$  and  $A_{n+1}$ , etc., and close examination of the interconnection of designs pursued in this text will reveal that the bus spacings of the adder subsystem dominate those of the other subsystems.

Figure 10-6 Possible floor plan for 4-bit processor

#### 296 Chapter 10

Rearrangements consequent on these considerations affect the barrel shifter (Figures 7-8 to 7-10) in particular. It is necessary to interchange the relative position of the *In* and *Out* bus lines and also make the cell stretchable to match the height of the dominant (adder) block and its bus spacing. Also, to mate with the bus structures of the other blocks, the *In* and *Out* bus lines should be in metal rather than polysilicon and diffusion, as used in our original design of Figures 7-8, 7-9 and 7-10.

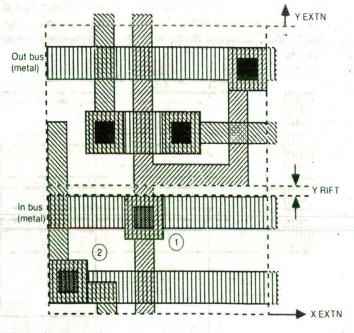

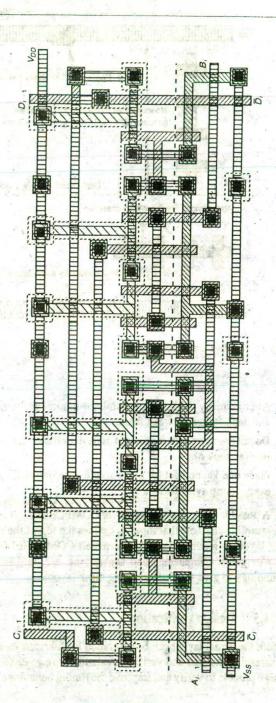

The way in which this may be done is indicated in the revised standard cell layout (Figure 10–7); it is necessary to allow for rifts and extensions *and* to cope with optional features which result from the four versions (owing to optional contacts) of the standard cell required, thus ensuring generality.

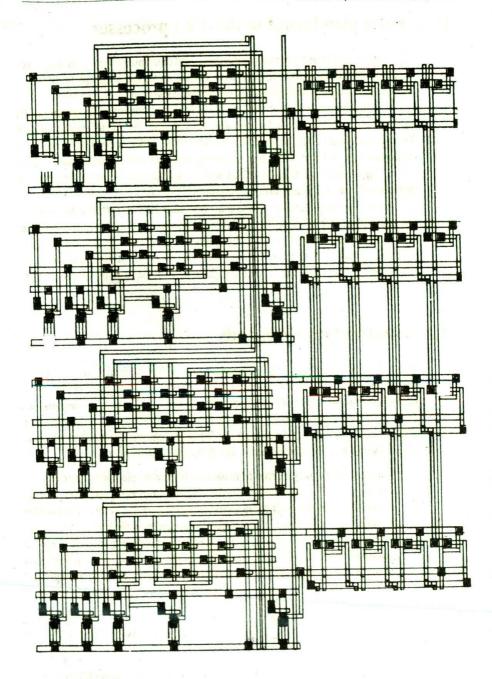

The concept of the use of a Y RIFT which is extendable from  $0\lambda$  minimum upward and X EXTN and Y EXTN which are extensions of the cell from  $0\lambda$ upward make the barrel shifter configurable to match most bus dispositions. Note that rifts and extensions should be placed where they cut a minimum amount of simple geometry; for example, Y RIFT involves the stretching of two wires one in polysilicon and the other in diffusion. Once such a degree of freedom is available, subsystems may be mated with a smooth flow-through of buses as suggested in Figure 10–8, which, for simplicity, shows the mask layout for an nMOS adder and a shifter which is on the right.

Note: 1 and 2 are optional contacts

Figure 10–7 Standard cell for barrel shifter

Figure 10–8 A possible interconnection of the adder and shifter subsystems

#### 298 Chapter,10 -

# 10.3 Floor plan layout of the 4-bit processor

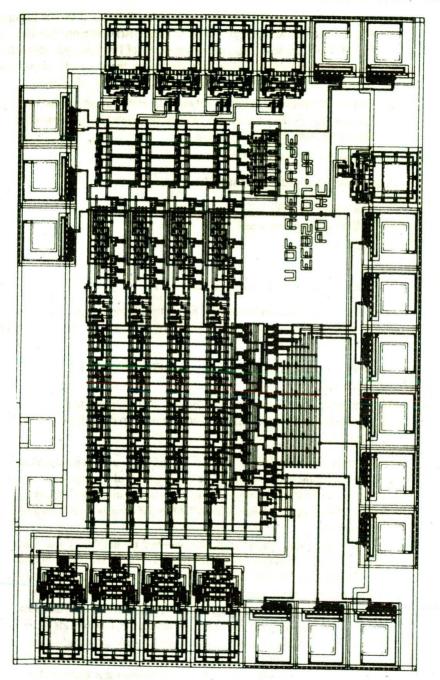

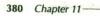

Having designed the three main subsystems and determined their bounding boxes and interconnection dispositions, we can now envisage a complete system in which they are disposed relative to each other as set out in Figure 10-6.

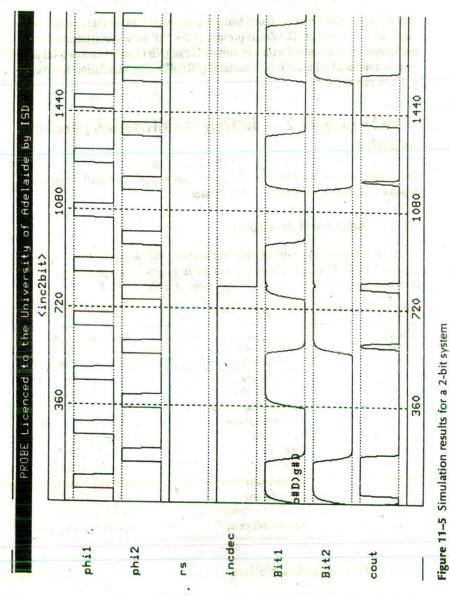

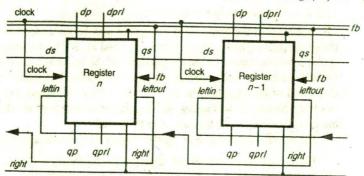

The dominant feature of the layout (in this case, the interbus spacing of the adder circuit) having already been determined, and the shifter having already been redesigned to allow stretching to match the adder, a consideration of the bounding box and of connections to the register array will reveal a need for some stretching of the basic register cell as well so that an easy interconnection of the subsystem can take place through alignment of the buses in each subunit.

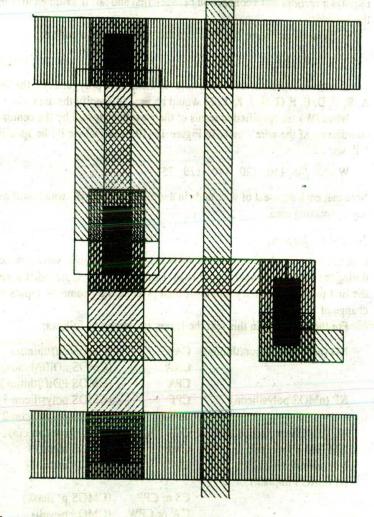

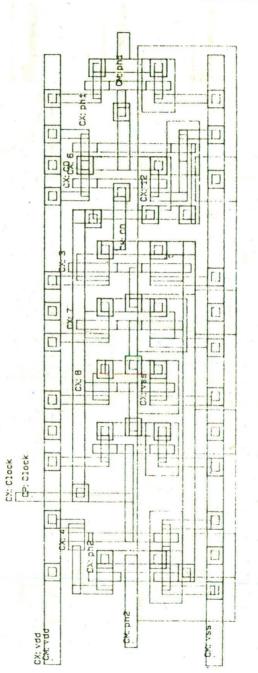

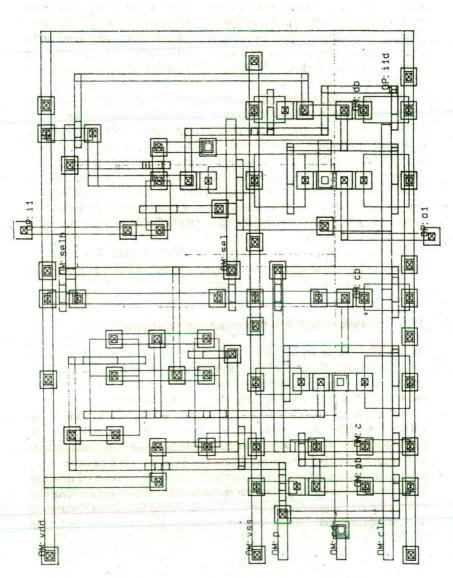

A possible arrangement — one that was fabricated as a student project — is included in Figure 10–9. Although layer encoding is lost in this particular black and white reproduction from a color-pen plotter of the mask layouts, the architecture and placement of the subsystems are quite readily apparent. Connections to and from the outside world are made through input and output pads which allow for bonding.

# 10.4 Input/output (I/O) pads

As well as allowing the bonding of leads from the chip to the pins on the package, the I/O pads cover a number of other requirements. Consequently, several types of pad are required. It is not within the scope of this text to present designs for a family of pads and, in most cases, pad designs are readily obtainable as basic library cells. However, the purposes served by the circuitry associated with pads require some general observations. The following needs must be met:

Protection of circuitry on chip from damage from static electricity and capacitive discharge (ESD) effects: this can be a serious problem, and care must be exercised in handling all MOS (and other integrated) circuits. The problem of 'static zap' may be put in perspective by considering the breakdown voltage of the thin oxide between gate and channel in, say, a 5 μm MOS circuit. Silicon dioxide has a breakdown voltage in the region of 10<sup>9</sup> volts/meter and for a gate oxide thickness of 0.1 μm, the maximum allowable voltage gate/ channel is

$V_{gcmax} < \frac{10^9 \text{ volts}}{\text{meter}} \times \frac{0.1}{10^6} \text{ meter} = 100 \text{ volts}$

This may sound generous in light of rail voltages of the order of 5 to 10 volts, but relatively high voltages are readily generated on one's person or on tools and handling equipment. Quite innocent pastimes, such as walking across

Figure 10–9 Complete layout of 4-bit data path multiproject chip

300 Chapter 10

a vinyl floor or a synthetic carpet, can generate voltages of several hundred volts under conditions of high relative humidity (RH) and more than 10 kV if the RH is low. These voltages are well in excess of 100 volts and, although in some cases immediate failure may not occur, there may be significant degradation of reliability and/or life through 'wounding' of circuits.

- 2. Provide the necessary buffering between the environments on and off chip. For example, buffers are needed to drive the relatively large capacitances associated with circuits off the chip.

- 3. Provide for the connection of power supply rails.

A minimum set of pads should include:

- 1.  $V_{DD}$  connection pad;

- 2.  $GND(V_{ss})$  connection pad;

- 3. input pad;

- 4. output pad;

- 5. bidirectional I/O pad (usually tristate logic).

In all cases when input and output (or bidirectional) pad designs from a library are used, the designer *must* be aware of the nature of the circuitry embodied in the pad design, that is:

- be aware of the ratios/size of inverters/buffers onto which output lines are connected;

- be aware of how input lines pass through the pad circuit (e.g. are the input signals fed in through pass transistors or do they come from inverter-like stages?).

Unless there are exceptional circumstances pads must always be placed around, the *periphery* of the chip area, otherwise bonding difficulties may be encountered. A sample set of nMOS 5  $\mu$ m pad designs may be consulted in Hon and Sequin, 1980, and Newkirk and Mathews, 1984. CMOS pad designs are usually available from fabricators.

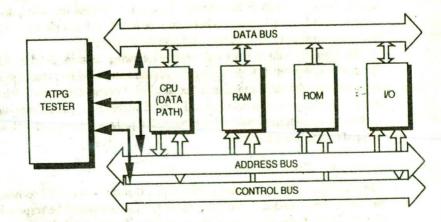

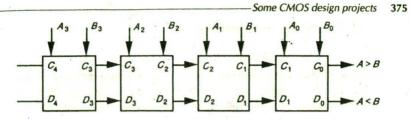

The designer must allow for the way in which the number of available pads quickly get used up and the very significant area they occupy. Take, for example, a simple processor of the type discussed in this text together with some RAM memory to form a basic microprocessor circuit. A typical arrangement is shown in Figure 10–10. Allowing for eight memory address lines (i.e. 256 locations of RAM), the complete chip as shown will need more than 30 pads which must therefore be accommodated in the layout. Such a number is readily bonded to, say, a 40-pin header, but the designer must also bear in mind that the package to be used will impose an ultimate limitation on the allowable number of pads.

Figure 10-10 4-bit processor — pad utilisation

# 10.5 'Real estate'

### Give me land, lots of land . . .

(words of a popular song of yesteryear)

One of the most common mistakes among beginners is to assume that phenomenal amounts of circuitry occupy very little area on the chip (VLSI = very little silicon indeed?). In order to correct such over-optimism it is necessary to consider only one or two of the practical factors which arise in system design.

For example, consider the area required by the I/O pads for the floor plan of Figure 10–10. The connections shown require 33 pads and typical standard 5  $\mu$ m pad layouts require an area of 105 $\lambda$  by 100 $\lambda$  to 200 $\lambda$  (depending on the nature of the pad). An average pad then occupies some 105 $\lambda$  by 150 $\lambda$ , say, that is, an area of 15,750 $\lambda^2$ . Thus the area required for 33 pads is over 500,000 $\lambda^2$ . To put this into perspective, the average area allowance for each student project for a multiproject chip (MPC) design was typically somewhere in the region of 1000 $\lambda \times 1000\lambda$ ,

that is,  $10^6\lambda^2$ . Thus, for the floor plan given in Figure 10–10, the pads would occupy one-half of this total area. Certainly, the design given here is somewhat pad-intensive but, as a rule of thumb, the small system designer should allow *one-third* of the chip area for pads.

Having come to terms with this, the budding designer may then consider what to do with the layout of the remaining two-thirds of the chip area (i.e. about  $700,000\lambda^2$  for an example MPC design). What is the prognosis?

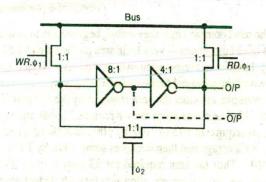

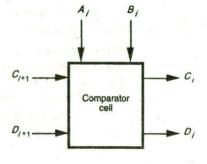

An assessment of what could be fitted into such an area could be approached by considering the basic enhancement mode pass transistor of *minimum size* occupying an area of  $4\lambda^2$ . If  $2\lambda$  clearance is allowed all around, then the on chip area will be  $36\lambda^2$ . Dividing this into the available area, one might conclude that almost 20,000 such devices could be fitted into the area under discussion. However, MOS circuitry necessitates the use of inverters or inverter-like circuits. When two transistors are put together and contacts etc. are added, then, typically, a single inverter occupies at least  $200\lambda^2$ . Viewed from this point, the same area should thus accommodate about 3500 inverters. However, this is also an overoptimistic assessment of the possible circuit density, since one has to consider the significant effect of interconnections even within a leaf-cell. Consider the simple memory cell of Figure 10–11 which we might use to implement the RAM of Figure 10–10. The temptation is to assess area requirements by reasoning thus:

two inverters + three pass transistors =  $2 \times 200\lambda^2 + 3 \times 36\lambda^2 = 508\lambda^2$

However, when design rule clearances, buses, power and control wiring are allowed for, this cell can occupy  $1500\lambda^2$  or more (i.e. a factor of 3:1 over the 'simple' estimates).

Now, consider the available area on the floor plan and further assume that about half this area (i.e. approximately  $350,000\lambda^2$ ) is to be devoted to the RAM. This area will allow no more than 256 bits of storage elements, as in Figure 10–11, and if each RAM location must hold a 4-bit word, then the delimer can be no more ambitious than a 64-word RAM. The running of extra bus lines, a

the register array, will further substantially increase the area occupied by each memory cell.

# 10.6 Further thoughts on system delays

10.6.1 Buses

He thought he saw [an operand], descending from a bus, he looked again and saw it was a hippopotamus.

# (With apologies to Lewis Carroll)

The use of bus lines is a convenient concept in distributing data and control through a system. However, it is easy to lose sight of what is *really* happening and bus-derived signals tend not to be what were expected.

Bidirectional buses are convenient but conflicts must be avoided since data cannot flow in both directions at once. Clearly, in our data path design, the sum  $S_k$  must be stored and then subsequently read onto the bus, since it becomes obvious that two buses cannot carry two input operands and the sum simultaneously. A significant problem which is often underestimated is that of speed restrictions imposed by the capacitive load presented by long bus lines.

The largest capacitance (for a typical bus system) is contributed by  $C_{BUS}$  (the bus wiring capacitance), and for small chips with, say, a 1000 $\lambda$  long bus this can be as high as 0.75 pF for a metal layer bus in 5  $\mu$ m technology. In total, then, the bus and associated circuitry for the system being considered could contribute a capacitive load of about 0.8 pF, which may be *driven* through pull-up (typically 20 to 40 k $\Omega$  'on' resistance) and pull-down (typically 10 k $\Omega$  'on' resistance) transistors and through at least one pass transistor or transmission gate in the series.

Therefore, sufficient time must be allowed to charge the total bus capacitance during, say,  $\phi_1$  of the clock. In the data path system considered here, the time required for the total bus capacitance to charge to an appropriate level (to, say, >90% of  $V_{DD}$ ) is in the region of 100 nsec. Thus, it may be seen that equal  $\phi_1$  and  $\phi_2$  clock periods would result in an upper clock frequency limitation for the processor due to bus loading alone of 5 MHz. This frequency can be increased by using asymmetric  $\phi_1$  and  $\phi_2$  periods or by using BiCMOS drivers.

# 10.6.2 Control paths, selectors, and decoders

A basic operation of a data path is to add together the numbers stored in two registers to produce a sum and a carry at the 'carry out' pad (for cascading, etc.).

#### 304 Chapter 10 -

In terms of *delays* involved, and in the context of the 5  $\mu$ m system considered here, the following delay mechanisms are encountered during this process:

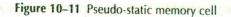

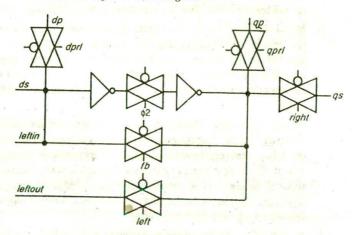

Select register and open pass transistors (or transmission gates) to connect cells to bus. For a particular design, the select logic and associated drivers might have the equivalent circuit as shown in Figure 10-12.

The overall delay of this arrangement may be assessed in terms of  $\tau$  (where  $\tau$  is the time constant of  $1 \square C_g$  charging through a minimum-size n-type pass transistor).

| Element(s) contributing                                                       | Delay         |  |

|-------------------------------------------------------------------------------|---------------|--|

| Input pad                                                                     | 30t (typical) |  |

| Three pass transistors $(n^2\tau) = 9\tau$                                    | 9τ            |  |

| Driver inverter pair ( $\Delta A \rightarrow \nabla B \rightarrow \Delta C$ ) | 34τ           |  |

| (Assuming $4\Box C_g$ load at C)                                              |               |  |

| Sum of delays (select register)                                               | = 73τ         |  |

## Figure10-12 Register select circuit

- 2. Data propagation along bus This has already been calculated as 100 nsec.

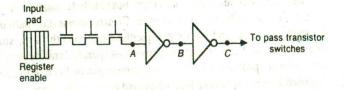

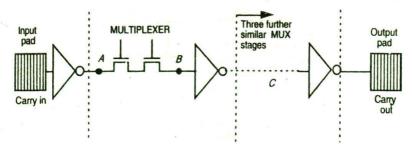

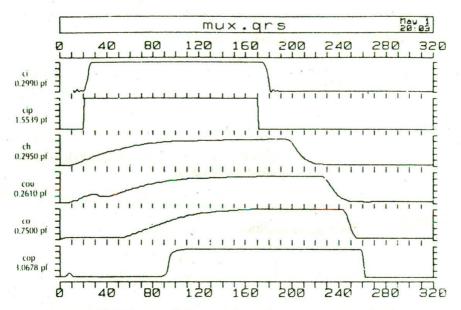

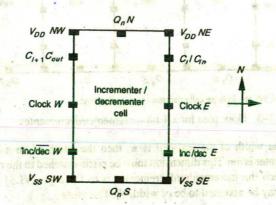

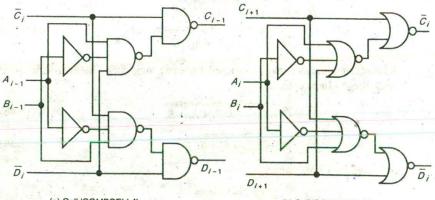

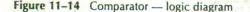

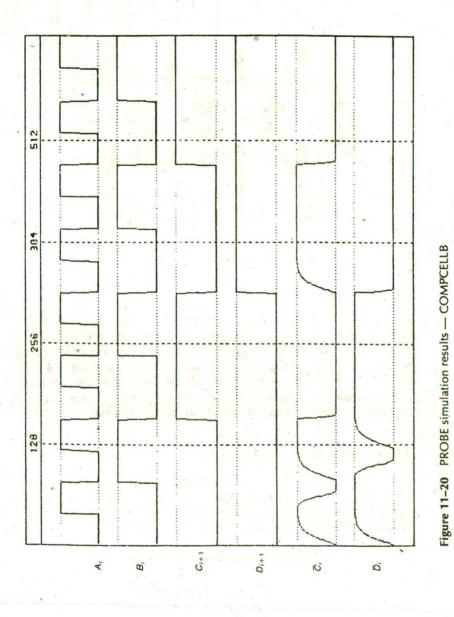

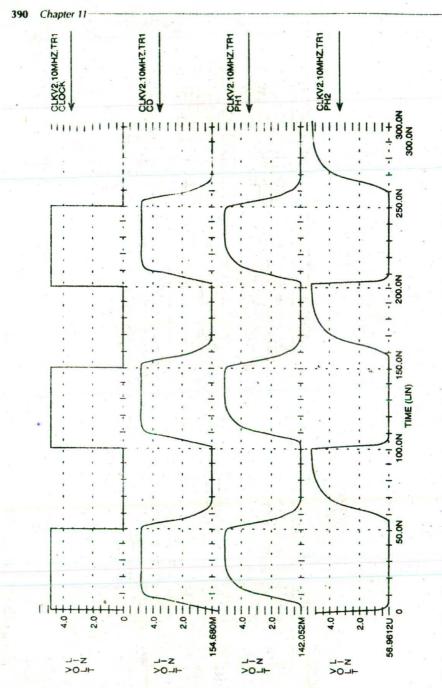

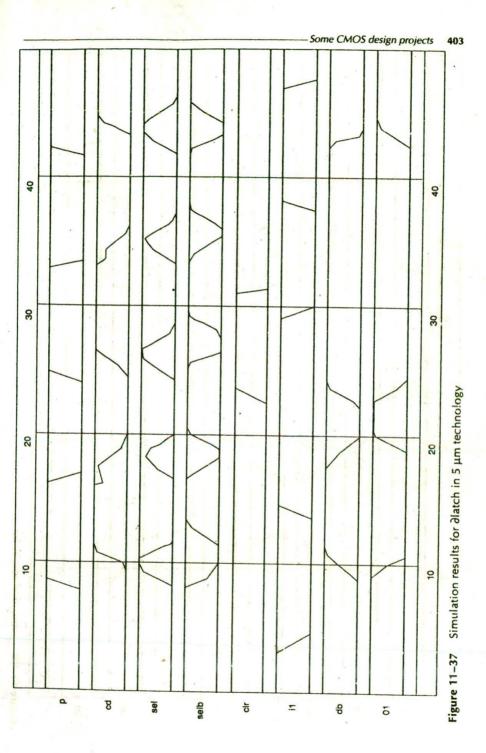

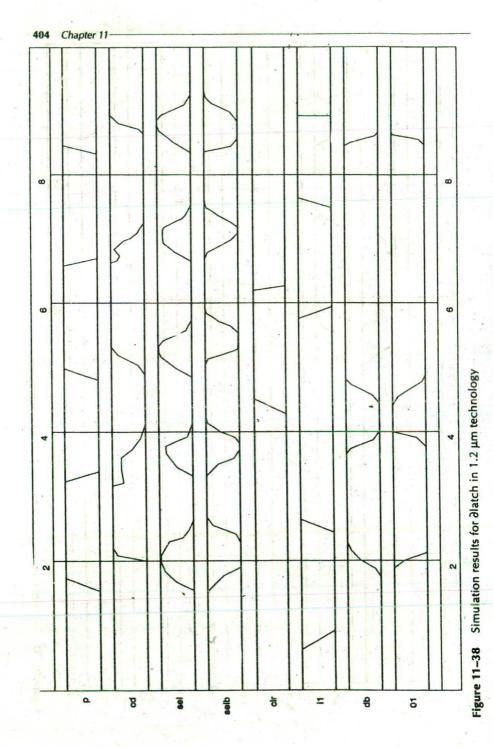

- 3. Carry chain delay The longest delay in the particular design of adder used is that of forming the 'carry out' which, in effect, propagates through all bits of the adder and then through the outlet pad as shown in Figure 10–13. Timing simulator results for a 2-bit arrangement is given as Figure 10–14. It will be seen that, although the  $\Delta C$  and  $\nabla C$  delays are slightly different, an average delay of 65 nsec is a fair assumption for the 2-bit system simulated. We may also deduce the delay per bit (= 20 nsec) from the simulation. Overall then, a 5  $\mu$ m 4-bit ripple-carry adder could be expected to have a delay of about 105 nsec.

Thus, the overall delay = select registers + bus delays + carry chain delays =  $(73\tau) + 100$  nsec + 105 nsec. For  $\tau = 0.2$  nsec

Sum of delays =  $14.6 + 100 + 105 \Rightarrow 220$  nsec

Thus,  $\phi_1$  of the clock must have a duration longer than 220 nsec.

Figure 10-13 Possible carry chain circuit

Figure 10-14 Timing simulation result for a 2-bit version of the multiplexerbased adder

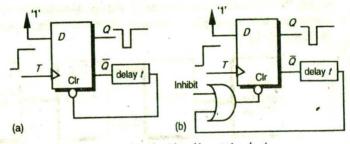

# 10.6.3 Use of an asymmetric two-phase clock

# 10.6.3.1 Clock period $\phi_2$

In many systems,  $\phi_2$  of the clock is used only to refresh memory/register cells such as that shown in Figure 10–15. From the figure it can be seen that  $\phi_2$  has to be long enough in duration to allow  $C_{in}$  to charge through the pull-up resistance of the second inverter and through the feedback circuit — which may be in the region of 35 k $\Omega$ , If time is allowed for  $C_{in}$  to charge to within < 10% of its final value, then refresh time  $= 2.5 \times 10\tau = 25\tau$  which, for the 5 µm system being

-21

Figure 10–15 Memory cell refresh

evaluated, equates to a minimum 'on' time of 5 nsec for  $\phi_2$ . However,  $\phi_2$  signals must also propagate through wiring etc., and finite rise- and fall-times must be allowed for so that some extra time should be allowed for the  $\phi_2$  'on' period. For safety allow, say, 50 $\tau$  (i.e. 10 nsec) for the  $\phi_2$  'on' period and also allow 10 nsec underlap between the two phases. Thus

total clock period = 220 + 10 + 10 + 10 = 250 nsec

Therefore, *in theory*, our simple modeling suggests that the data path chip design should operate on add instructions with a 4-MHz clock.

# 10.6.4 More nasty realities

Life wasn't meant to be easy. Malcolm Fraser (former Prime Minister of Australia)

The simple calculations made on the particular processor design seem to indicate that a clock frequency in the region of 4 MHz would be possible. In practice, this may not happen. Why is this so? To answer this it is necessary to consider practical as well as theoretical realities.

From the theoretical aspect, our predictions have been made on very approximate parameter values and on very simple circuit models. We have also mostly ignored the quite significant effects of peripheral capacitance in diffusion regions and fringing field capacitances around conductors on the chip.

Although  $\tau$  was assumed to be in the range 0.1 to 0.3 nsec for 5  $\mu$ m technology, the value of  $\tau$  measured for the fabricated chip may not be within this range.

Practical aspects and testability 307

In fact, the value of  $\tau$  measured on some 5 µm MPC circuits fabricated and tested for this project was in the region of 0.6 nsec.

The designer, therefore, must be aware of, and allow for, all the significantly nasty realities affecting the performance of the design, and have a good knowledge of the parameters of the processing plant or fabrication line where that design is to be implemented in silicon.

There are two main points of difference between expectations and realization which characterize many of the designs of beginners. They are:

1. The system being designed occupies far more area than was anticipated.

2. The system when manufactured is slower than the designer had estimated.

However, if the first few designs are carefully carried out, are not over-ambitious, and are properly checked for logical and design rule errors, the beginner is usually pleasantly surprised by the fact that the system does in fact function, albeit not quite as fast as intended.

# 10.7 Ground rules for successful design

This section is intended to provide a convenient focus for design information. From our considerations of system design up to this point a number of ground rules; aspects of philosophy, and some basic data have emerged which help to ease the design process and ensure success. These and one or two other considerations which are important (but have not as yet been formally set out in the text) are presented or referenced here under 19 subheadings.

- 1. The ratio rules (Chapter 2)

- (a) for nMOS inverters and inverter-like stages

$Z_{p.u}$ :  $Z_{p.d}$  ratio = 4:1 when driven from another inverter

$Z_{p,\mu}$ :  $Z_{p,d}$  ratio = 8:1 when driven through one or more pass transistor(s). where

Z = L/W for the channel in question

- (b) for CMOS, a 1:1 ratio is normally used to minimize area, but for pseudonMOS inverters etc., a ratio  $Z_{p,u}:Z_{p,d} = 3:1$  is required.

- 2. Design rules (Chapter 3). Never bend the rules.

- 3. Typical parameters for 5  $\mu$ m ( $\lambda$  = 2.5  $\mu$ m), 2  $\mu$ m and 1.2  $\mu$ m feature size MOS (Chapter 4) including guidelines for signal interconnections.

#### 308 Chapter 10 -

| Layer R, ohm per square                                            |                                                              |                                                                                 |

|--------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------|

| definitions of all an a second                                     | 5 μm <sup>-1</sup> στο το τ | Orbit                                                                           |

| Metal<br>Diffusion (n-type or n-active)<br>Silicide<br>Polysilicon | 0.03<br>10-50*<br>2-4<br>15-100                              | 0.04<br>20-45*                                                                  |

| n-transistor channel<br>p-transistor channel                       | $10^{-100}$<br>$10^{4}$<br>$2.5 \times 10^{4}$               | 15–30<br>2 × 10 <sup>4</sup> <sup>†</sup><br>4.5 × 10 <sup>4</sup> <sup>†</sup> |

# Table 10-2 (Table 4-1) Typical sheet resistances R<sub>s</sub> of MOS layers for 5 μm, and Orbit 2 μm and 1.2 μm technologies

Note: In some processes a silicide layer is used in place of polysilicon.

\*Times 2.5 for p-type.

<sup>†</sup> These values are approximations only. Resistances may be calculated from a knowledge of  $V_{dt}$  and the expressions for  $I_{dt}$  given earlier.

| Table 10–3 (Table 4–2) Typical area capacitance value | Table 10- | 3 (Table | e 4-2) Typic | cal area car | pacitance value |

|-------------------------------------------------------|-----------|----------|--------------|--------------|-----------------|

|-------------------------------------------------------|-----------|----------|--------------|--------------|-----------------|

| Capacitance                           | (1                  | Value in pF $\times$ 10 <sup>-4</sup> / $\mu$ m <sup>2</sup><br>elative values in bracket | s)                         |

|---------------------------------------|---------------------|-------------------------------------------------------------------------------------------|----------------------------|

|                                       | 5 µm                | 2 μm                                                                                      | 1.2 µm                     |

| Gate to channel<br>Diffusion (active) | 4 (1.0)<br>1 (0.25) | 8 (1.0)<br>1.75 (0.22)                                                                    | 16 (1.0)                   |

| Polysilicon* to substrate             | 0.4 (0.1)           | 0.6 (0.075)                                                                               | 3.75 (0.23)<br>0.6 (0.038) |

| Metal 1 to substrate                  | 0.3 (0.075)         | 0.33 (0.04)                                                                               | 0.33 (0.02)                |

| Metal 2 to substrate                  | 0.2 (0.05)          | 0.17 (0.02)                                                                               | 0.17 (0.01)                |

| Metal 2 to metal 1                    | 0.4 (0.1)           | 0.5 (0.06)                                                                                | 0.5 (0.03)                 |

| Metal 2 to polysilicon                | 0.3 (0.075)         | 0.3 (0.038)                                                                               | 0.3 (0.018)                |

Note: Relative value = specified value/gate to channel value for that technology. \*Poly 1 and Poly 2 are similar (also silicides where used).

| Table 10-4 | (Table 4–3) | Typical va | alues for | diffusion | capacitances |

|------------|-------------|------------|-----------|-----------|--------------|

|------------|-------------|------------|-----------|-----------|--------------|

| Diffusion capacitant                      | ce                                            | Typical values                             |                                            |

|-------------------------------------------|-----------------------------------------------|--------------------------------------------|--------------------------------------------|

|                                           | 5 µm                                          | 2 µm                                       | 1.2 μm                                     |

| Area C ( $C_{area}$ )<br>(as in Table 42) | $1.0 \times 10^{-4} \text{ pF/}\mu\text{m}^2$ | 1.75 × 10 <sup>-4</sup> pF/μm <sup>2</sup> | 3.75 × 10 <sup>-4</sup> рF/µm <sup>2</sup> |

| Periphery (Cperiph)                       | 8.0×10 <sup>-4</sup> pF/μm                    | negligible*                                | negligible*                                |

\* Assuming implanted regions of negligible depth.

In order to calculate the total diffusion capacitance we must add the contributions of area and peripheral components.

$$C_{total} = C_{area} + C_{periph.}$$

### Standard unit of capacitance $\Box C_{g}$

$1 \square C_{e}$  is defined as the gate-to-channel capacitance of a MOS transistor having W = L = feature size, that is, a 'standard' or 'feature size' square (the concept of  $\square C_{e}$ , originated by VTI (USA), has been adapted here).

$\Box C_g$  may be evaluated for any MOS process. For example, for 5  $\mu$ m MOS circuits:

standard value  $\Box C_{g} = .01 \text{ pF}$

or, for 2 µm MOS circuits (Orbit) :

standard value  $\Box C_{o} = .0032 \text{ pF}$

and, for 1.2 µm MOS circuits(Orbit):

standard value  $\Box C_{p} = .0023 \text{ pF}$

#### The delay unit $\tau$

We have developed the concept of sheet resistance  $R_s$  and standard gate capacitance unit  $\Box C_g$ . If we consider the case of one standard (feature size square) gate area capacitance being charged through one feature size square of n channel resistance (i.e. through  $R_s$  for an nMOS pass transistor channel), we have:

time constant  $\tau = lR_s$  (n channel)  $\times l\Box C_s$  seconds

This can be evaluated for any technology and for 5 µm technology

theoretical  $\tau = 0.1$  nsec.

and for 2 µm (Orbit) technology

theoretical  $\tau = 0.064$  nsec.

and for 1.2 µm (Orbit) technology

theoretical  $\tau = 0.046$  nsec.

However, in practice, circuit wiring and parasitic capacitances must be allowed for so that the figure taken for  $\tau$  is often increased by a factor of two or three.

Taking account of resistances and total capacitances we may set out practical guidelines on signal path lengths as in the following table (10–5), noting that the figures given are conservative but safe.

4. Inverter pair delay

In general terms, the delay through a pair of similar nMOS inverters is

$$T_d = (1 + Z_{n,u} / Z_{n,d}) \tau$$

and for a minimum size CMOS complementary inverter pair

$T_d = 7\tau$

#### 310 Chapter 10

| Layer                                                    | Maximun                             | a length of communica                                                                          | cation wire       |  |  |

|----------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------|-------------------|--|--|

|                                                          | lambda-based (5 µm)                 | µm-based (2 µm)                                                                                | µт-based (1.2 µт) |  |  |

| Metal<br>Silicicide<br>Polysilicon<br>Diffusion (active) | chip wide<br>2,000λ<br>200λ<br>20λ* | chip wide         chip w           n.a.         400 μm         250           100 μm         60 |                   |  |  |

## Table 10–5 (as for Table 4–4) Electrical rules

\* Taking account of peripheral and area capacitances. n.a. not applicable.

5. Cascaded inverters for driving capacitive load  $(C_L)$

The approach is to use N cascaded inverters, each one of which is larger than the preceding stage by a width factor f.

It has been shown that the number 'N' of stages required is given by

$$N = \frac{\ln(y)}{\ln(f)}$$

where

$$y = \frac{C_L}{\Box C_g}$$

It can also be shown that total delay is minimized if f assumes the value e (base of natural logarithms); that is, each stage should be approximately 2.7\* times wider than its predecessor. This applies to CMOS as well as nMOS inverters. See Chapter 4 for more details.

\* Note: Usually f = 3 will do since the curve is quite flat near the minimum.

6. Propagation delay through cascaded pass transistors or transmission gates (Chapter 4)

$$T_d = n^2 r c (\tau)$$

where

n = number in series

- r = relative series resistance per transistor or per transmission gate in terms of  $R_s$

- c = relative capacitance gate to channel per transistor or per transmission gate in terms of  $\Box C_g$ .

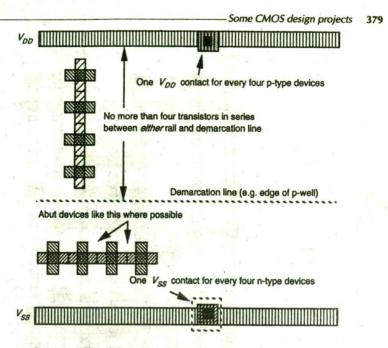

Normally, no more than four pass transistors or transmission gates should be connected in series without buffering.

7. Factors influencing choice of layer for wiring (Chapter 4)

Table 10-6 (Table 4-5) Choice of layers

|             | Rel      | ative    | all an it is the                                                                                                              |

|-------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| Layer       | R        | C        | Comments                                                                                                                      |

| Metal       | Low      | Low      | Good current capability without large<br>voltage drop use for power distribution<br>and global signals.                       |

| Silicide*   | Low      | Moderate | Modest RC product. Reasonably long<br>wires are possible. Silicide is used in place<br>of polysilicon in some nMOS processes. |

| Polysilicon | High     | Moderate | RC product is moderate; high IR drop.                                                                                         |

| Diffusion   | Moderate | High     | Moderate IR drop but high C.<br>Hence hard to drive.                                                                          |

Note: V<sub>DD</sub> and V<sub>SS</sub> (or GND) rails must always be run in metal, except for very short 'duck unders' where crossovers are unavoidable.

Not often available — depending on process line.

- 8. Subsystem/leaf-cell design guidelines (Chapter 6)

- (a) Define the requirements properly and carefully.

- (b) Consider communication paths most carefully in order to develop sensible placing of subsystems and leaf-cells.

- (c) Draw a floor plan (alternating with (b) as necessary).

- (d) Aim for regular structures so that design is largely a matter of replication.

- (e) Draw stick diagrams for basic cells, leaf-cells, and/or subsystems or enter the design in symbolic form.

- (f) Convert to a mask level layout.

- (g) Carefully and thoroughly check each mask layout for design rule errors and simulate circuit or logical operation. Correct as necessary, *rechecking* as corrections are made.

- 9. Restrictions associated with MOS pass transistors and transmission gates (Chapter 6)

- (a) No more than four in series without buffering (see Point 6).

- (b) No pass transistor gate must be driven from the output of one or more pass transistors, since logic 1 levels are degraded by threshold voltage  $V_{ip}$  (where  $V_{ip}$  can be as high as 0.3  $V_{DD}$ ).

#### 312 Chapter 10

(c) When designing switch logic networks of pass transistors or transmission gates, care must be taken to deliberately implement *both* the logic 1 and logic 0 output conditions.

Note: An if, then, else approach to specifying requirements will help to make sure that this is done.

10. Storage of logic levels on the gate capacitance of transistors

- (a) Gate/channel capacitance is suitable for storing a bit, but care must be taken to allow for the finite decay time (about 0.25 msec at room temperature).

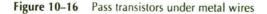

- (b) It is quite allowable to construct pass transistors, etc. under metal layers to save space. This is often convenient and is used, for example, in some multiplexer layouts, but care must be taken with overlying metal wires where gate/channel capacitance is used for bit storage.

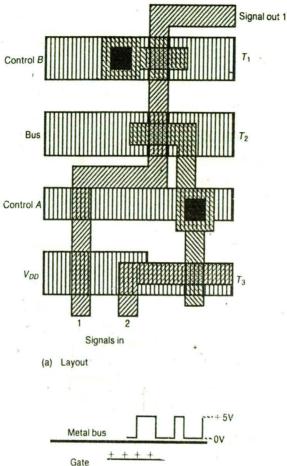

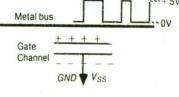

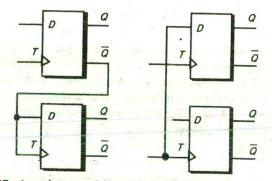

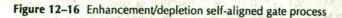

Consider Figure 10–16(a). Three such instances are illustrated here, all of which lie under metal wires. Two of these cases,  $T_1$  and  $T_3$ , will operate satisfactorily, since for  $T_1$  the metal wire is actually connected to the gate and for  $T_3$  the metal wire is at a fixed, unvarying potential (that is,  $V_{DD}$  in this case). However,  $T_2$  gate region lies under a metal bus which has no connection with the gate of  $T_2$ . If a bit is stored on  $T_2$  gate by momentarily connecting *Control A* to the required level, then the bit will be stored but can be disturbed or destroyed by variation of the voltage on the overlying bus, as Figure 10–16(b) reveals.

(c) Restrictions also apply to logic level storage on the input capacitance of a Nand gate except for the input *nearest* the GND or  $V_{SS}$  rail. Conditions are indicated in Figure 10–17.

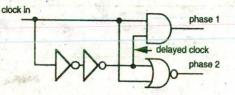

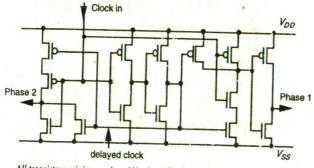

# 11. Enhanced clocking

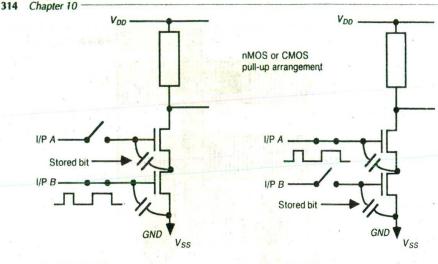

One of the basic limitations on the use of simple MOS pass transistors (see Point 9 above) is the degradation of logic 1 levels by  $V_{tp}$  and the consequent inability of one pass transistor to drive the gate of a second (or more) pass transistor. This is particularly bothersome in clocking networks and a solution to this problem is to run all clock lines at a voltage level above  $V_{DD}$  as shown in Figure 10–18.

Note that the signal propagated through  $T_1$  is  $V_{DD}$ , while that propagated through  $T_2$  is  $V_{DD} - V_{Ip}$ .

- The maximum allowable current density in aluminum wires is 1 mA/μm<sup>2</sup>. Otherwise, metal migration may occur (Chapter 6). Current density must be particularly carefully considered if the circuit is to be scaled down.

- 13. Scaling effects: see Chapter 5.

(b) Circuit model

14. System design process (Chapter 7 - refer also to point 8 in this section)

- (a) Set out a specification together with an architectural block diagram.

- (b) Suitably partition the architecture into subsystems that are, as for as possible, self-contained and give interconnections that are as simple as possible.

(a) Not allowable

(b) Allowable

Figure 10–17 Storage nodes in gate arrangements

Figure 10–18 Enhanced clocking

- (c) Set out a tentative floor plan showing the proposed relative physical disposition of subsystems on the chip.

- (d) Determine interconnection strategy.

- (e) Revise (b), (c), and (d) interactively as necessary.

- (f) Choose layers on which to run buses and main control signals.

- (g) Take each subsystem in turn and conceive a regular architecture to conform to the strategy set out in (d). Set out circuit and/or logic diagrams as appropriate. Remember that switch-based logic is such that both logic 1 and logic 0 output conditions must be deliberately satisfied (see Point 9).

- (h) Develop stick or symbolic diagrams adopting suitable tactics to meet the overall strategy (d) and choice of layers (f). Determine suitable *leaf-cell(s)* from which the subsystem may be formed.

- (i) Produce mask layouts for the leaf-cells making sure that cells can be butted together, side by side and/or top to bottom, without design rule violation or waste of space. Carefully check for any design rule errors in each standard cell itself. Determine overall dimensions of each cell and characterize in bounding box form if convenient.

- (j) Cascade the replicate leaf-cells as necessary to complete the desired subsystem. This may now be characterized in bounding box form with positions and layers of inlets and outlets. External links, etc. *must* be allowed for. Check for design rule errors.

- 15. Further observations on the design process (based on Chapter 8)

- (a) First and foremost, try to put requirements into words (often an *if, then, else* approach helps to do this) so that the most appropriate architecture or logic can be evolved.

- (b) If a standard leaf-cell(s) can be arrived at, then the actual detailed design work, including simulation, is confined initially to small areas of simple circuitry.

- (c) Aim for generality as well as regularity, that is, leaf-cells, etc. should not be highly specialized unless absolutely necessary.

- (d) Communications dominate any system design.

- (e) A good library of basic leaf-cells and subsystems will speed design and allow accurate floor planning at an early stage.

- (f) A structured and orderly 'top-down' approach to system design is highly beneficial and becomes essential for large systems.

- 16. Set out rules of system timing at an early stage in design. A sample set of such rules is set out in Chapter 9 (section 9.1).

- 17. Avoid bus contentions by setting out bus utilization diagrams or tables, particularly in complex systems and/or where bidirectional buses are used.

- 18. Do not take liberties with the design rules but do take account of the ground rules and guidelines.

- 19. Remember, IC designers should expect their systems to function first time around\* and this will happen if the design concepts are correct and if the rules are obeyed.

(We do not subscribe to the view 'If it works, it's out of date' (Stafford Beer), but we do contend that poorly conceived and badly designed systems may well be out of date before they work!)

<sup>\*</sup> Not necessarily at optimum speed ... this may take longer and depends on the designer's understanding of the properties of circuits produced in silicon.

#### 316 Chapter 10 --

# 10.8 The real world of VLSI design

Knowledge comes, but wisdom lingers.

## Alfred Lord Tennyson

The preceding sections of this book have been intended to give the reader an understanding of the way in which system, circuit, and logic requirements may be turned into silicon and a feeling for the nature of silicon circuits. The authors believe that a sound understanding of *cause and effect* is essential if the maximum benefits are to be obtained from VLSI and the fullest range of applications opened up to VLSI realizations. Thus it is without apology that we have dwelt on the fundamental aspects of design in silicon.

From a sound foundation, a VLSI designer can operate with confidence, but must face up to the following requirements when contemplating large system designs in silicon.

- CAD. The VLSI designer will need computer-aided design assistance, not only to assist in the design but also to handle the sheer complexity of the information needed to express the physical aspects of the design in a form suitable for translation into silicon.

- 2. Verification tools are essential to verify that the design is physically and logically correct and will perform correctly at the desired speed.

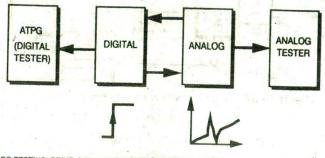

- Testability. The designer must, from the outset, face up to the requirements of being able to test a system once it is realized in silicon.

- Test facilities. Not only must testability be designed in but complex systems will need sophisticated equipment to actually test for correct operation.

Thus, it is a purpose of this chapter to present an overview of these important topics in order to put them in perspective for the budding VLSI designer. However, it is not our intention to cover comprehensively any of these topics. Although the topics are dealt with separately, it will be readily apparent that they are closely interrelated and can be significantly interdependent.

# 10.9 Design styles and philosophy

Style, like sheer silk, too often hides eczema.

Albert Camus

When wishing to implement a system design in silicon, various approaches are possible and, of course, a wide range of technologies is available to choose from. The designer must choose an appropriate design style, but at this point it must be stressed that in no case will the choice of style hide the lack of a competent and systematic approach by the designer. However, we may summarize the possibilities into three broad categories:

Practical aspects and testability 317

- 1. Full custom design of the complete system for implementation in the chosen technology. In this case, the designer designs all the circuitry and all interconnection/communication paths.

- 2. Semi-custom design using a library of standard leaf-cells together with specially designed circuits and subsystems which are placed appropriately in the floor plan and interconnected to achieve the desired functional performance. In this case, the designer designs a limited amount of circuitry and the majority of interconnections/communications.

- Gate array (uncommitted logic array) design in which standard logic elements are presented for the designer to interconnect to achieve the desired functional performance. In this case, the design is that of the interconnections and communications only.

Once again the boundaries between these categories may be blurred. For example, full custom design seldom involves the complete design of the entire chip; input/output pad circuits are more or less accepted as standard components and are generally available to the custom designer.

In all cases it is desirable to take a hierarchical approach to the system design in which the principles of iteration or replication (regularity) can be used to reduce the complexity of the design task.

The designer is usually concerned with a number of key design parameters. These will include:

- 1. performance, in terms of the function to be performed, the required speed of operation and the power dissipation of the system;

- 2. time taken for the design/development cycle;

- 3. testability

- 4. the size of the die, which is determined by the area occupied by the circuitry and in turn has a marked impact on the likely yield in production and on the cost of bonding and packaging and testing. Large die sizes are generally associated with poor yields and high costs.

Full custom design tends to achieve the best results, but *only* if the designer is fully conversant with the fundamental aspects of design in silicon so that parameters can be optimized. However, full custom design parameter optimization is usually at the expense of parameter 2, the time taken to design.

Semi-custom and gate array designs both have penalties in area and often in speed and this is contributed to by the fact that not all the available logic will be used. This is due to the need for generality in gate array and standard cell geometries. However, it may often be the case that gate arrays will be faster than a prototype full custom design in, say, MPC form and the final custom designs must often be carefully optimized.

318 Chapter 10 -

Once the approach is chosen, there remains the design philosophy which ranges through the following general possibilities.

- 1. Hand-crafted design in which, for example, the mask layouts are drawn on squared paper with layer encoding and are then digitized to give a machine-readable form of the mask detail. Digitization can be done 'by hand', with entry of coordinates through, say, a keyboard or by more direct digitization of the drawn layout using a digitizer pad and cursor.

- 2. Computer-assisted textual entry of mask detail through a keyboard using some specially developed language employing a text editing program. Such programs may have relatively low-level capabilities, allowing the entry of rectangular boxes, and 'wires', etc. only, or may be at a higher level and allow symbolic entry of circuit elements such as transistors and contact structures.

- 3. Computer-assisted graphical entry of mask geometry through either a monochrome or color graphics terminal, again with the aid of the appropriate entry, display, and editing software.

In cases 2 and 3 the software usually aids the processes of hierarchical system design in that leaf-cells (or symbols) can be instanced many times, each instance being placed as appropriate in the floor plan. Subsystems thus created may themselves be repeatedly instanced and placed as required to build up the system hierarchy.

Such tools obviously encourage regularity and are generally used with a generate then verify design philosophy.

4. Silicon compiler-based design in which a high level approach is taken to design, and special languages, analogous to high level programming language compilers, are developed to allow the designer to specify the system requirements in a manner which is convenient and compact. The silicon compiler program then translates this input code into a mask design which will generate a circuit in silicon to meet the specified system requirements. Such programs are the subject of much research and development work at this particular time. Indeed, the work has reached a stage at which silicon compilers have been in use for some time and there are textbooks on the subject (e.g. Ayres, 1983).

# 10.10 The interface with the fabrication house

## Knowledge without practice makes but half an artist.

Proverb

Obviously, real world designs in silicon are intended to be fabricated and there is no doubt that the learning processes associated with VLSI design depend heavily on actually designing systems in silicon, on having them *fabricated* and then on testing the fabricated chips. In all cases, then, good two-way communications between the fabrication house or silicon broker and the designer must be established.

Communication from the former to the latter usually takes the form of a set of design rules which specify clearances, widths, spacing, overlaps, etc. for the process to be used. The design rules used in this test are examples of such rules. The fabrication house will also supply design parameters relevant to its processes. These include layer resistance values, layer to layer capacitance values, etc., and typical values have been given and used in this text.

In return, the designer must communicate his mask layout designs to the fabricator in a form which is convenient and clearly understandable. Methods of expressing mask geometry are not entirely standardized, but a *de facto* standard appears to be CIF code.

# 10.10.1 CIF (Caltech. Intermediate Form) code

CIF is a low-level graphics language for specifying the geometry of integrated circuits (Hon and Sequin, A Guide to LSI Implementation, Xerox). The purpose of CIF code is to communicate chip geometry in a standard machine-readable form for mask-making. CIF code is reasonably compact and can cope with small and large system geometry. Its format is straightforward and it has the added advantage of being easily read. It has been widely used for the electronic transport of designs between universities and industrial laboratories, using such facilities as ARPANET in the United States and CSIRONET in Australia. Thus, it is appropriate to briefly examine some of the features of CIF so that the reader may appreciate general attributes of the code.

# 10.10.1.1 Geometric primitives

Various geometric structures such as boxes, polygons, and wires are readily defined. In general, the position, dimensions, and orientation must be specified and, also of course, the layer on which the box exists in the silicon. When examining the attributes of CIF code, the reader should be aware that CIF dimensions and positions are given in X, Y coordinate form but are in absolute dimension units, *not* in lambda form.

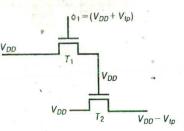

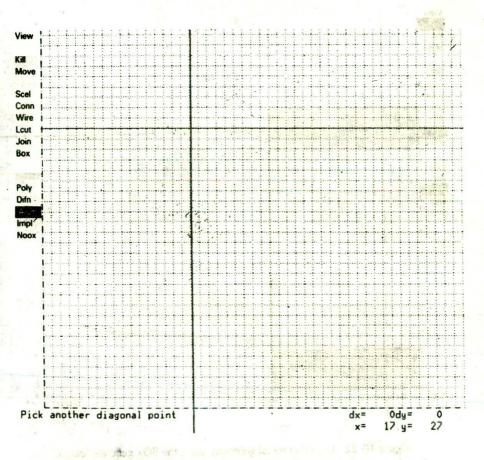

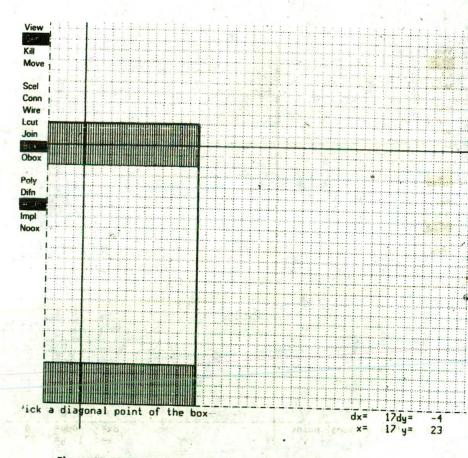

A few examples (Figure 10-19) illustrate the features of the representation.

Boxes (B) are specified as

Box

Length (L) Width (W)

Center (C)

Direction (D)

Note that direction is given as a vector assumed parallel to the length. If not given, then a vector 1,0(x,y) is assumed (that is, length will be parallel to the x-axis).

Boxes I and II in the diagram would therefore appear in code as

|           |     |        | Practical aspects and testability 32                 | 1  |

|-----------|-----|--------|------------------------------------------------------|----|

| B 25      | 60  | 50 80  | <u>-10, 10;</u> (box                                 | I) |

| (L)       | (W) | (C)    | (D) (L, W, C, D would n<br>appear in the actual code |    |

| •<br>B 40 | 20  | 40 35; | (box I                                               |    |

Polygons (P) are specified in terms of the vertices in order. An *n*-sided polygon requires *n* vertices and a connection between first and last is assumed to complete the boundary.

Polygon III in Figure 10-19 would therefore appear in code as

P - 10 - 10 40 10 20 - 25 (polygon III)

In order to represent areas with holes in them, as in polygon (IV), the vertices A, B, C, D, E, F, G, H, J, K, L, M would be used to specify the area.

Wires (W) are specified in terms of their width followed by the center line's coordinates of the wire's path. In Figure 10–19, wire (V) would be specified as follows:

W 10 90 110 120 110 120 75

Note that each segment of wire ends in a semicircular 'flash' which will overlap any connecting area.

#### 10.10.1.2 Layers

Layer selection and subsequent changes are treated by mode setting prior to or during the entry of geometric primitives. Layer setting must precede the entry of the first piece of geometry and must then precede the geometric inputs on any change of layer.

For the processes in this text the layers are named as follows:

| ND (nMOS diffusion/thinox)             | CAA       | (CMOS diff/thinox)         |

|----------------------------------------|-----------|----------------------------|

| in the second second                   | CNA       | (CMOS nDiff/thinox)        |

|                                        | CPA       | (CMOS PDiff/thinox)        |

| NP (nMOS polysilicon)                  | CPF       | (CMOS polysilicon 1)       |

| distribute the test of the             | CPS       | (CMOS polysilicon 2)       |

| NC (nMOS contact cut)                  | CC        | (CMOS contact cut)         |

| NM (nMOS metal l)                      | CMF       | (CMOS metal l)             |

| NN (nMOS metal 2)<br>NI (nMOS implant) | CMS       | (CMOS metal 2)             |

|                                        | CS or CPP | (CMOS p <sup>+</sup> mask) |

|                                        | CW or CPW | (CMOS p-well)              |

NV (nMOS Via) NB (nMOS buried contact) NG (nMOS overglass cuts)

| CVA     | 50  |  |

|---------|-----|--|

| CG or ( | COG |  |

| CBA     |     |  |

(CMOS overglass cuts) (BiCMOS p-base) (BiCMOS buried collector)

(CMOS Via)

Layer changes are indicated by the letter L followed by the layer name.

CCA

1374

CIF also accommodates calls (C) and rotations and translations, etc., but the elementary review given here should convey the essential features. To reinforce this, a simple cell layout is given as Figure 10–20 with the corresponding CIF code given in Table 10–7.

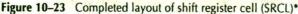

Figure 10–20 Layout of 'SRCELL' (plotted from the CIF code of Table 10–7)

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 Lambda = 2                          | 50: silisita a contait?                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1 minut in a lot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S 1001;                               | Llong                                                                                                             |

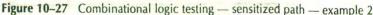

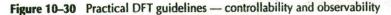

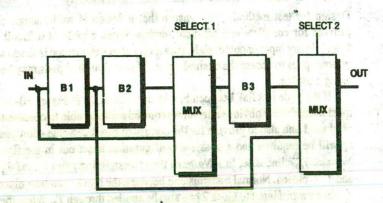

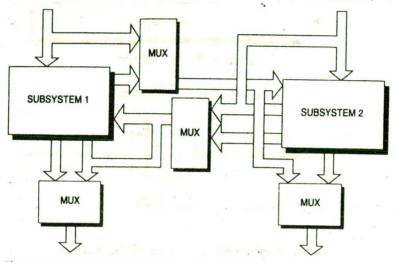

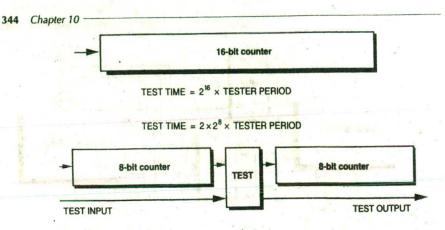

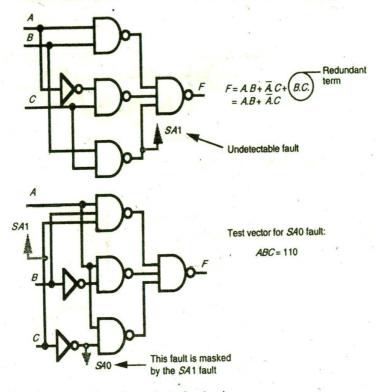

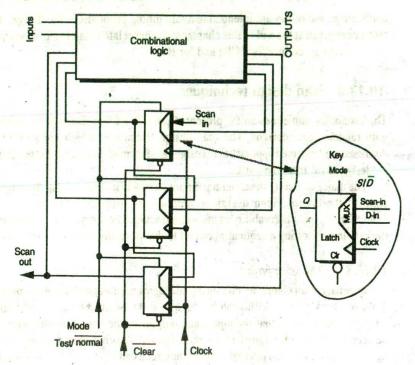

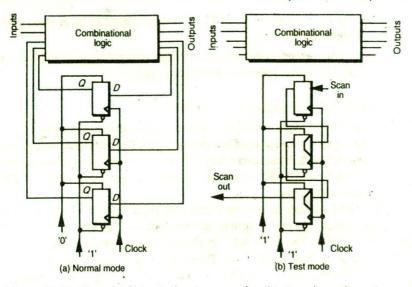

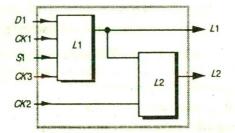

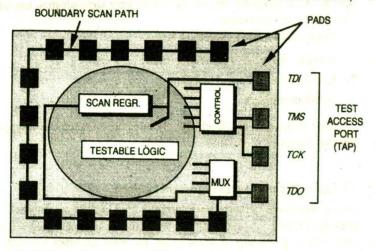

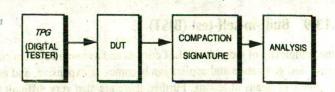

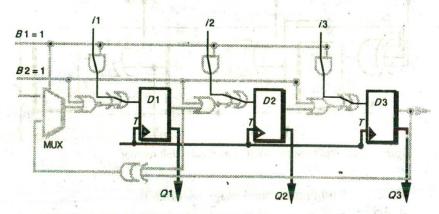

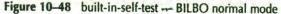

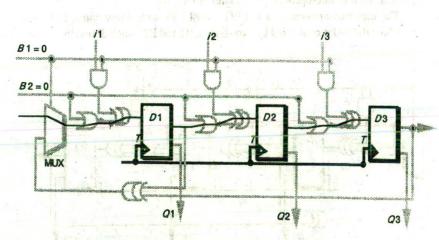

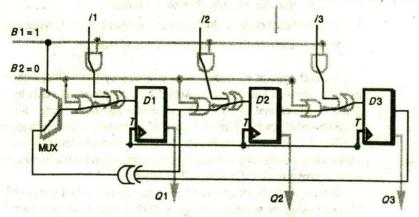

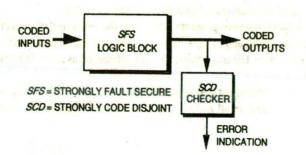

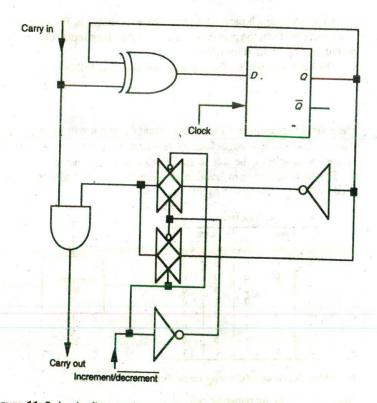

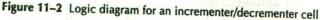

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SRCELL;                               |                                                                                                                   |