# Chapter 15 Operational Amplifier Frequency Response and Compensation

# Chapter Contents

### Introduction

1

- 15-1 Operational Amplifier Circuit Stability 506

- 15-2 Frequency Compensation Methods 511

- 15-3 Op-amp Circuit Bandwidth and Slew Rate 514

- 15-4 Stray Capacitance Effects 518

- 15-5 Load Capacitance Effects 520

15-6 Circuit Stability Precautions 523 Review Questions 524

Problems 525 Practise Problem Answers 527

# Objectives

You will be able to:

- Show how feedback can produce instability in op-amp circuits.

- 2 Sketch and explain typical gain/ frequency and phase/frequency response graphs for uncompensated and compensated operational amplifiers.

- 3 Define: loop gain, loop phase shift, phase margin.

- 4 Discuss compensation methods for stabilizing op-amp circuits, and calculate component values for compensating circuits.

- 5 Explain how the bandwidth of an op-amp circuits is affected by closedloop gain.

- 6 Define: Gain-bandwidth product, slew rate, full-power bandwidth.

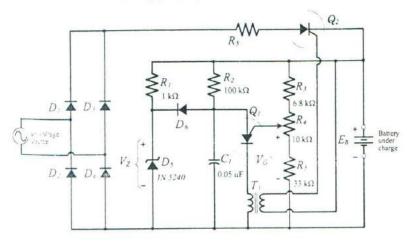

- 7 Determine the bandwidths of various op-amp circuits using: frequency response graphs, gainbandwidth product, and slew rate.

- 8 Explain how stray and load capacitance can affect op-amp circuit stability, sketch appropriate compensating circuits, and calculate suitable component values.

- List precautions that should be observed to ensure op-amp circuit stability.

# Introduction

Signals applied to operational amplifiers experience phase shifts as they pass from input to output. These phase shifts are greatest at high frequencies, and at some particular frequency the total loop phase shift (from the inverting input terminal to the output and back to the input via the feedback network) can add up to 360°. When this occurs, the amplifier circuit can go into a state of unwanted oscillation. The conditions that produce oscillation are that the loop voltage gain be greater than or equal to unity when the loop phase shift approaches 360°. Measures taken to combat instability include the use of capacitors and resistors to reduce the total phase shift. Most operational amplifiers have compensating components included in the circuitry to ensure stability.

# 15-1 Operational Amplifier Circuit Stability

# Loop Gain and Loop Phase Shift

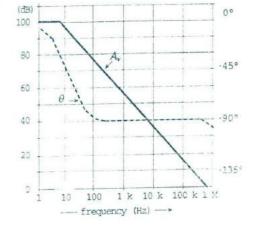

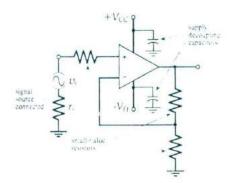

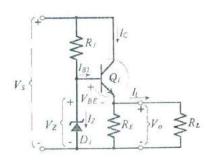

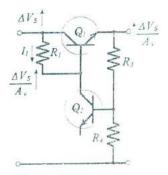

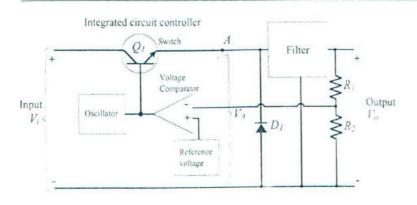

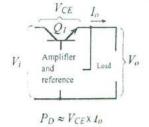

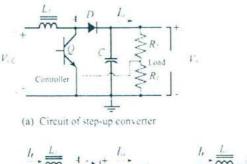

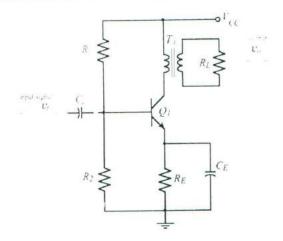

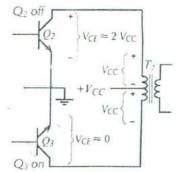

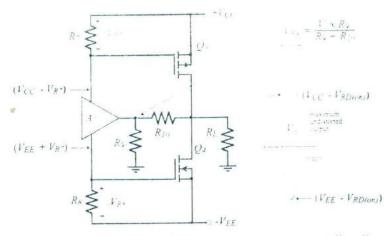

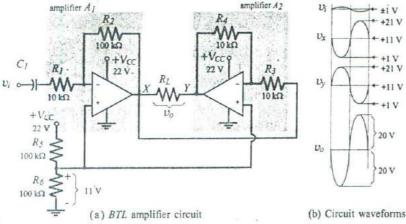

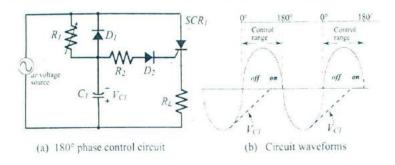

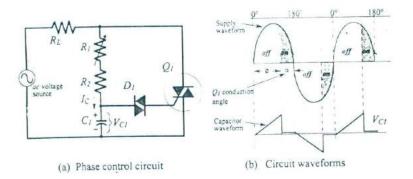

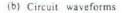

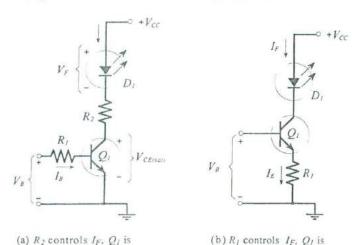

Consider the inverting amplifier circuit and waveforms in Fig. 15-1(a). The signal voltage voltage  $(v_s)$  is amplified by a factor  $R_2/R_1$ , and phase shifted through -180°. The circuit is redrawn in Fig. 15-1(b) to illustrate the fact that the output voltage  $(v_o)$  is divided by the feedback network to produce the feedback voltage (v).

For an *ac* voltage (*v*) at the op-amp inverting input terminal [in Fig. 15-1(b)], the amplified output is  $v_0 = A_v v$ , as shown. The output is divided by the feedback factor  $[B = R_1/(R_1 + R_2)]$ , and fed back to the input. An additional -180° of phase shift can occur within the op-amp at high frequencies, and this causes *v* to be inphase with  $v_0$ , as illustrated. Thus, the feed back voltage can be exactly equal to and in phase with the voltage (*v*) at the inverting input. In this case, the circuit is supplying its own *ac* input voltage, and a state of continuous oscillation exists.

Because of the feedback network, high-frequency oscillations can occur in many operational amplifier circuits, and when this happens the circuit is termed *unstable*. Measures taken to combat circuit instability are referred to as *frequency compensation*.

Two conditions normally have to be fulfilled for a circuit to oscillate; the *loop gain* must be equal to or greater than 1, and the *loop phase shift* should equal 360°. The loop gain is the voltage gain around the loop from the inverting input terminal to the amplifier output, and back to the input via the feedback network. The loop phase shift is the total phase shift around the loop from the inverting input terminal to the input terminal to the inverting input terminal to the inverting input terminal to the amplifier output, and back to the amplifier output, and back to the input via the feedback network.

The gain from the inverting input terminal to the output is the op-amp open-loop gain  $(A_v)$ . For the feedback network, the gain from the amplifier output back to the input is actually an attenuation. So,

loop gain = (amplifier gain) x (feedback network attenuation) =  $A_v B$  Assuming that the feedback network is purely resistive, it adds nothing to the loop phase shift. The loop phase shift is essentially the amplifier phase shift. The phase shift from the inverting input terminal to the output is normally -180°. (The output goes negative when the input goes positive, and vice versa.) At high frequencies there is additional phase shift caused by circuit capacitances, and the total can approach -360°. When this occurs, the circuit is virtually certain to oscillate. Most currentlyavailable operational amplifiers have internal *compensating components* to prevent oscillations. In some cases, compensating components must be connected externally to stabilize a circuit.

### Figure 15-1

Because an inverting amplifier consists of an operational amplifier and a feedback network, the circuit can supply its own ac input (v derived from  $v_o$ ), and a state of continuous oscillations can occur.

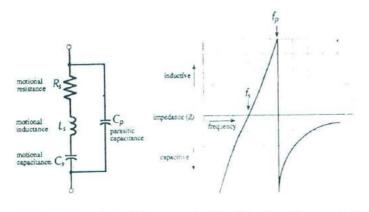

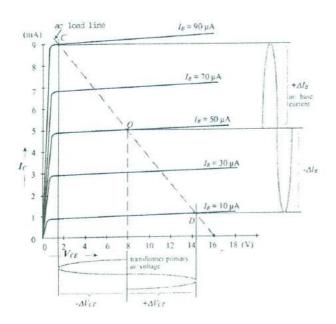

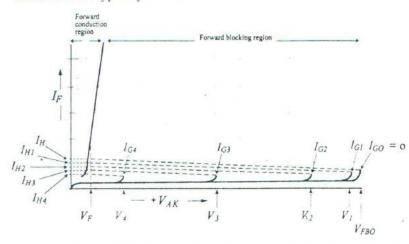

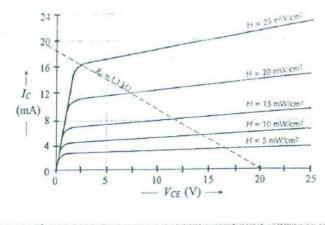

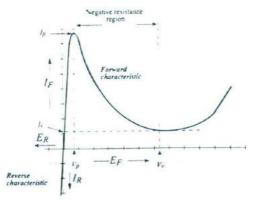

# Uncompensated Gain and Phase Response

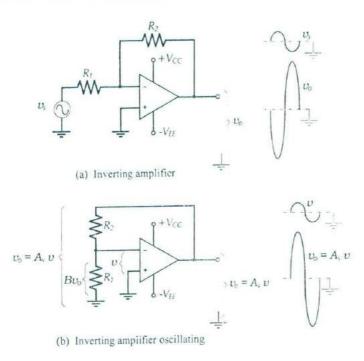

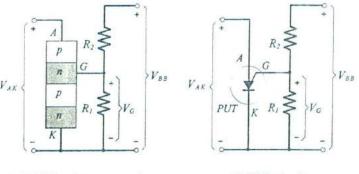

A straight-line approximation of the gain/frequency response graph for a typical operational amplifier without any compensating components is shown in Fig. 15-2. Note that the overall open-loop voltage gain ( $A_v$ ) initially falls off (from its 100 dB level) at 6 dB/octave (-20 dB/decade) from  $f_{p1}$  (pole frequency #1). From  $f_{p2}$ , the rate of decline is 12 dB/octave (-40 dB/decade), and from  $f_{p3}$ , the fall-off rate of  $A_v$  is 18 dB/octave (-60 dB/decade).

The phase/frequency response graph in Fig. 15-2 shows that the phase shift ( $\theta$ ) is approximately -45° at  $f_{pl}$ , -135° at  $f_{p2}$ , and -225° at  $f_{p3}$ . This open-loop phase shift is in addition to the -180° phase shift that normally occurs from the op-amp inverting input terminal to the output. Thus, the total loop phase shift ( $\sigma_l$ ) at  $f_{p1}$  is (-45° -180°) = -225°; at  $f_{p2}$ ,  $\sigma_l = (-135° - 180°) = -315°$ ; and at  $f_{p3}$ ,  $\sigma_l = (-225° - 180°) = -405°$ .

As already discussed, oscillations occur when the loop gain is equals or exceeds 1 and the loop phase shift is 360°. In fact, the phase shift does not have to be exactly 360° for oscillation to occur. A phase shift of 330° at  $A_vB = 1$  makes the circuit unstable. To avoid oscillations, the total loop phase shift must not be greater than 315° when  $A_vB = 1$ . The difference between 360° and the actual loop phase shift at  $A_vB = 1$  is referred to as the *phase margin* ( $\sigma_m$ ). Thus, for circuit stability, the phase margin should be a minimum of,

$ø_m = 360^\circ - 315^\circ = 45^\circ$

### Figure 15-2

The three stages of an op-amp (internal) circuit each has its own gain/irequency response with a 6 dB octave fall-off, and its own phases shift' frequency response with a maximum phase shift of  $90^{\circ}$ . These responses combine to give the overall op-amp A<sub>v</sub>/f and  $\theta$ /f responses.

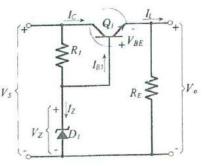

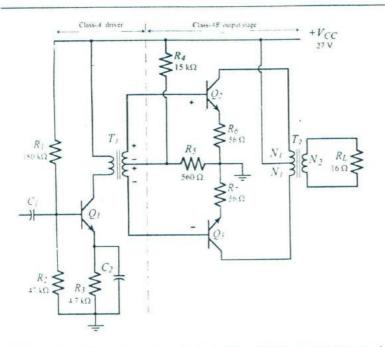

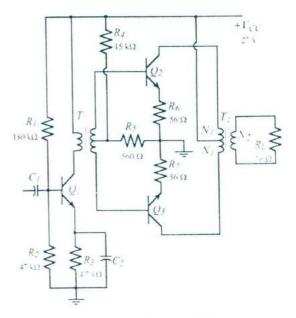

# Compensated Op-amp Gain and Phase Response

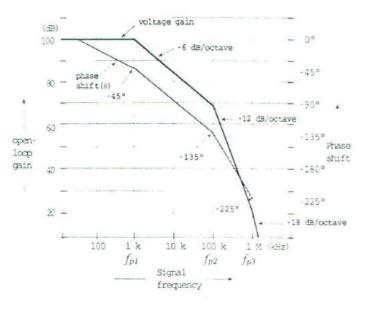

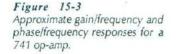

The open-loop gain/frequency and phase/frequency responses for two internally compensated operational amplifiers are shown in Figs. 15-3 and 15-4. The 741 frequency response graphs in Fig. 15-3 shows that the gain starts at 100 dB and falls by 20 dB/decade over most of its frequency range. The phase shift remains -90° or less for most of the frequency range. The open-loop gain falls off to 1 (0 dB) at a frequency of approximately 800 kHz. The 741 is known as a general purpose operational amplifier for use in relatively low frequency applications.

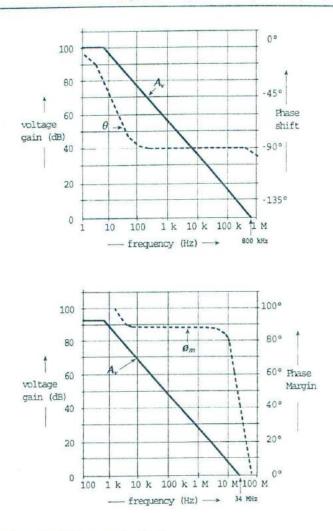

The *AD843* frequency response in Fig. 15-4 shows an open-loop gain of 90 dB at low frequencies, falling off at 20 dB per decade to 34 MHz at  $A_v$  =1. Instead of the open-loop phase shift, the phase margin is plotted versus frequency. The phase margin is close to 90° over much of the frequency range, starts to become smaller around 3.4 MHz, and falls to approximately 40° at f = 34 MHz.

Figure 15-4 Approximate gain/frequency and phase-margin/frequency response for an AD843 op-amp.

# Amplifier Stability and Gain

From Eq. 13-3, the overall voltage gain of an amplifier with negative feedback is,

$$A_{CL} \approx \frac{1}{B}$$

$$A_{v}B \approx \frac{A_{v}}{A_{CL}}$$

and the loop gain is,

So, the loop gain  $(A_v B)$  equals 1 when

$$A_{CL} \approx A_v$$

This is one of the conditions required for circuit oscillation. To determine if oscillation will occur in a given circuit, it is necessary to first find the frequency at which  $A_{CL} \approx A_v$ , then determine the op-amp phase margin at that frequency.

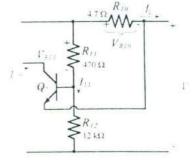

# Example 15-1

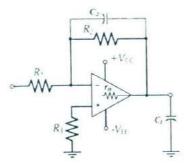

The inverting amplifier in Fig. 15-5 is to be investigated for stability. Determine the frequency at which the loop gain equals 1 and estimate the phase margin if the operational amplifier is: (a) one with the gain/frequency characteristics in Fig. 15-2, (b) a 741, (c) an AD843.

# Solution

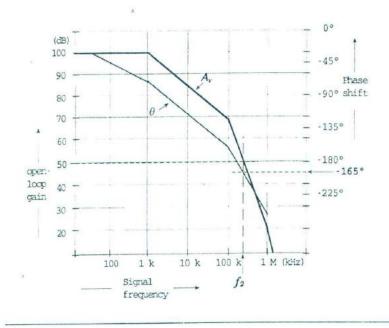

(a) Refer to the  $A_v/f$  and  $\theta f$  graphs reproduced in Fig. 15-6 (from Fig. 15-2).

$$A_{CL} = \frac{R_{-}}{R_{1}} = \frac{560 \text{ k}\Omega}{1.8 \text{ k}\Omega}$$

$$= 311$$

$$A_{Cl} = 20 \log 311$$

$\approx 50 \text{ dB}$

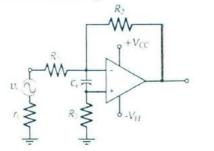

R<sub>1</sub> R<sub>1</sub> R<sub>1</sub> R<sub>2</sub> 560 kΩ +V<sub>CC</sub> +V<sub>CC</sub> -V<sub>II</sub>

Figure 15-5 Inverting amplifier circuit for Example 15-1.

Draw a horizontal line on the frequency response graph at  $A_v = A_{C1} = 50$  dB. (Fig. 15-6). Draw a vertical line where the horizontal line intersects the  $A_v f$  graph. The frequency at this point is identified as  $f_0$ .

$f_3 \approx 150 \text{ kHz}$  (logarithmic scale)

From the  $\theta$ /f graph, the op-amp phase shift at f, is,

$\theta \approx -165^{\circ}$

The loop phase shift is,

and,

Because the phase margin is less than 45°, the circuit is likely to be unstable.

(b) For a 741

A horizontal line at 50 dB on the frequency response in Fig. 15-3 gives,

$$f_2 \approx 1.5 \text{ kHz and } \theta \approx -90^\circ$$

$\theta_l = -90^\circ - 180^\circ$

$= -270^\circ$

and,

$g_m = 360^\circ - 270^\circ$

= 90° (stable circuit)

(c) For an AD843

A horizontal line at 50 dB on the frequency response in Fig. 15-4 gives,

$$f_2 \approx 90 \text{ kHz}$$

$\phi_m \approx 90^\circ \text{ (stable circuit)}$

and,

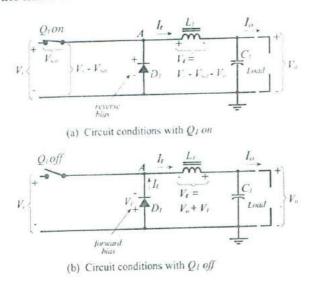

A circuit with the frequency response in Fig. 15-6 and with  $A_{CL} = 50$  dB was shown to be unstable. If the amplifier had  $A_{CL} = 70$  dB, reconsideration shows that it is stable. That is, an amplifier with a high closed-loop gain is more likely to be stable than one with the lower gain. Low gain amplifiers are more difficult to stabilize than high gain circuits. The voltage follower (with a closed-loop gain of 1) can be one of the most difficult circuits to stabilize.

Some internally compensated op-amps are specified as being stable to closed-loop gains as low as 5. In this case, external compensating components must be used with lower gain circuits.

Practise Problems 15-1.1 Investigate the stability of an inverting amplifier with a closed-loop gain of 60 dB if the operational amplifier is; (a) one with the gain/frequency characteristics in Fig. 15-2, (b) a 741, (c) a AD843.

\*

# 15-2 Frequency Compensation Methods

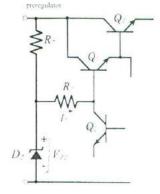

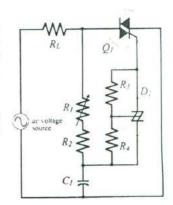

# Phase-Lag and Phase-Lead Compensation

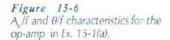

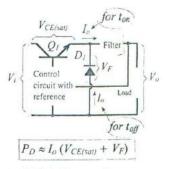

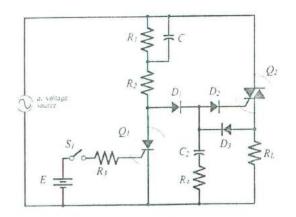

Lag compensation and lead compensation are two methods often employed to stabilize op-amp circuits. The phase-lag network in Fig. 15-7(a) introduces additional phase lag at some low frequency where the op-amp phase shift is still so small that additional phase lag has no effect. It can be shown that at frequencies where  $X_{C1} >> R_2$ , the voltage  $v_2$  lags  $v_1$  by as much as 90°. At higher frequencies where  $X_{C1} << R_2$  no significant phase lag occurs, and the lag network merely introduces some attenuation. The effect of this attenuation is that the  $A_v/f$  graph is moved to the left, as illustrated in Fig. 15-7(b). Thus, the frequency  $(f_{xl})$  at which  $A_vB = 1$  [for a given closed-loop gain  $(A_{Cl})$ ] is moved to a lower frequency  $(f_{x2})$ , as shown. Because  $f_{x2}$  is less than  $f_{xl}$ , the phase shift at  $f_{x2}$  is less than that at  $f_{xl}$ , and the circuit is likely to be stable.

### Figure 15-7

A phase-lag network reduces an amplifier open-loop gain, so that the phase shift where  $A_c B = 1$  is too small for instability. A phase-lead network cancels phase lag.

(b) Effect of lag compensation

(d) Effect of lead compensation

The network in Fig 15-7(c) introduces a phase lead. In this network, when  $X_{Cl} >> R_l$ , the voltage  $v_2$  leads  $v_l$ . This phase lead cancels some of the unwanted phase lag in the operational amplifier  $\theta/f$  graph, [see Fig. 15-7(d)], thus rendering the circuit more stable. Phase-lag and phase-lead networks are both used internally to compensate op-amp circuits. Both types of circuit can also be used externally.

# Manufacturer's Recommended Compensation

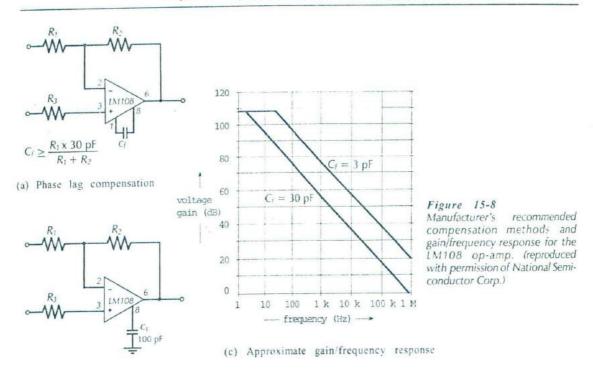

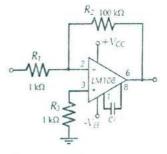

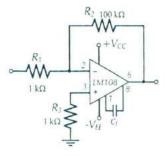

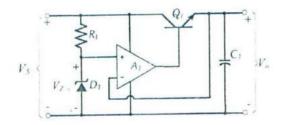

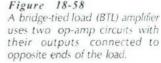

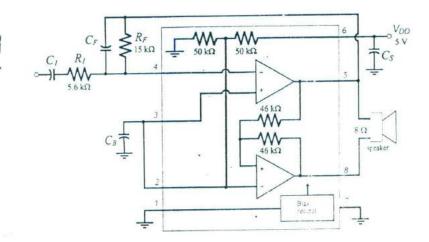

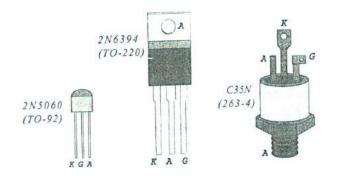

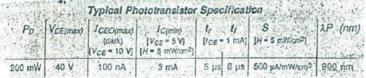

Most currently-available operational amplifiers contain internal compensating components, and do not require additional external components. Some have internal compensating resistors, and need only a capacitor connected externally to complete a compensating network. For those that require compensation, *IC* manufacturers list recommended component values and connection methods on the op-amp data sheet. An example of this is illustrated in Fig. 15-8 for the *LM108*.

When selecting standard value compensating capacitors the next larger values should be used. This is termed *over-compensation* and it results in better amplifier stability, but it also produces a smaller circuit bandwidth.

(b) Alternate phase lag compensation

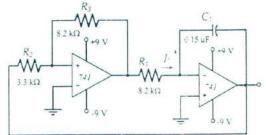

# Example 15-2

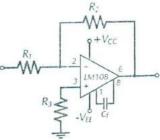

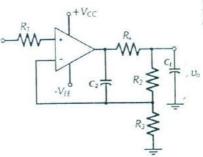

The inverting amplifier in Fig. 15-9 is required to amplify a 200 mV input by a factor of 4.5. Determine suitable component values.

### Solution

Because the LM108 has a very low input bias current (see Appendix 1-14), it should be treated as a BIFET op-amp.

Select

From Fig. 15-8,

$$R_2 = 1 M\Omega$$

$$R_{1} = \frac{R_{2}}{A_{Cl}} = \frac{1 \text{ M}\Omega}{4.5}$$

$$= 222 \text{ k}\Omega \text{ (use } 220 \text{ k}\Omega \text{ standard value}$$

$$R_3 = R_1 ||R_2 = 220 \text{ k}\Omega||1 \text{ M}\Omega$$

= 180 k $\Omega$  (standard value)

$$C_{f} = \frac{R_{1} \times 30 \text{ pF}}{R_{1} + R_{2}} = \frac{220 \text{ k}\Omega \times 30 \text{ pF}}{220 \text{ k}\Omega + 1 \text{ M}\Omega}$$

= 5.4 pF (use 10 pF standard value for over-compensation)

Connect C, between terminals 1 and 8, as shown in Fig. 15-9.

Figure 15-9 Op-amp circuit for Ex. 15 -2.

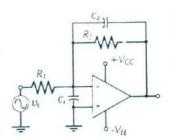

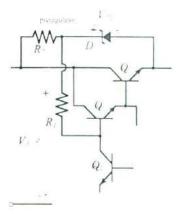

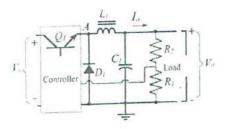

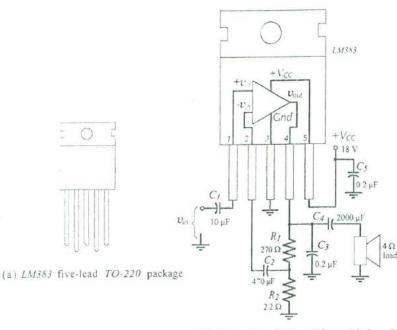

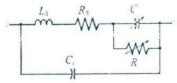

# Miller-Effect Compensation

Miller effect (discussed in Section 8-3) involves connecting a capacitor between the output and input terminals of an inverting amplifier. Miller-effect compensation of an op-amp circuit is very simple, and it is often the only external method available for stabilizing a circuit where the op-amp is internally compensated. A capacitor ( $C_f$ ) is connected across the feedback resistor, as shown or in Fig. 15-10(a) and (b). The capacitor value is calculated to have an impedance equal the feedback resistor value at the desired signal cutoff frequency ( $f_o$ ).

$$X_{cf} = R_f \operatorname{at} f_2$$

(15-1)

This reduces the closed-loop by 3 dB at the selected frequency. So long as the op-amp is stable at this frequency, the circuit will not oscillate. The op-amp used should have an upper cutoff frequency much higher than  $f_2$ .

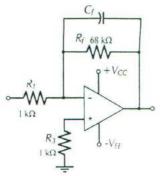

# Example 15-3

Calculate a suitable Miller-effect capacitor to stabilize the circuit in Fig. 15-10(a) at  $f_2 = 35$  kHz.

# Solution

From Eq. 15-1, C,

$$=\frac{1}{2\pi i \cdot R} = \frac{1}{2\pi \times 35 \text{ kHz} \times 68 \text{ k}\Omega}$$

$\approx$  67 pF use 68 pF standard value)

# Practise Problems

- 15 -2.1 The components of the lag and lead compensation network in Fig. 15-7 are:  $R_1 = 6.8 \text{ k}\Omega$ ,  $R_2 = 390 \Omega$ , and  $C_1 = 500 \text{ pF}$ . Calculate the approximately phase lag and phase lead at a frequency of 50 kHz.

- 15 -2.2 Calculate a suitable Miller-effect capacitor to stabilize the circuit in Fig. 15-10(b) at  $f_2 = 50$  kHz.

# 15-3 Op-amp Circuit Bandwidth and Slew Rate

# Low Cutoff Frequency

Operational amplifiers are direct-coupled internally, so where they are employed in direct-coupled applications, the circuit lower cutoff frequency  $(f_l)$  is zero. In capacitor-coupled circuits, the lower cutoff frequency is determined by the selection of coupling capacitors. The circuit high cutoff frequency  $(f_2)$  is, of course, dependent on the frequency response of the operational amplifier.

### High Cutoff Frequency

In Section 13-7 it is shown that for a negative feedback amplifier,

(a) Inverting amplifier with Millereffect compensation

(b) Noninverting amplifier with Miller-effect compensation

Figure 15-10 Miller-effect frequency compensation for amplifier circuits. the high cutoff frequency occurs when the amplifier open-loop gain approximately equals the circuit closed-loop gain:

Eq. 13-26,

$$A_v = A_{CL}$$

So, the circuit high cutoff frequency  $(f_2)$  can be found simply by drawing a horizontal line at  $A_v \approx A_{CL}$  on the op-amp open-loop gain/ frequency response graph. Because the op-amp low cutoff frequency is zero (as explained above). The circuit bandwidth is.

$$BW = f_2 - f_1$$

$$= f_2$$

Consequently, the op-amp high cutoff frequency is often referred to as the circuit bandwidth.

The frequency response graphs published on manufacturer's data sheets are typical for each particular type of operational amplifier. Like all typical device characteristics, the precise frequency response differs from one op-amp to another. All frequencies derived from the response graphs should be taken as typical quantities. The process of determining circuit cutoff frequency from the op-amp frequency response graph is demonstrated in Example 15-4.

Figure 15-11 Amplifier circuit for Example 15-4.

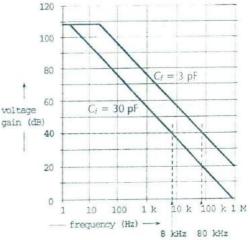

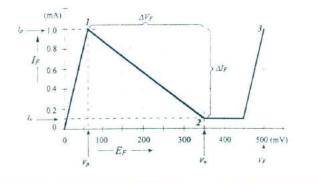

### Example 15-4

Determine the typical upper cutoff frequency for the inverting amplifier in Fig. 15-11 when the compensating capacitor ( $C_f$ ) value is; (a) 30 pF, (b) 3 pF. The  $A_f$  graph for the LM108 is shown in Fig. 15-12.

Solution

$$A_{\rm CL} = \frac{R_2}{R_1} = \frac{100 \,\mathrm{k\Omega}}{1 \,\mathrm{k\Omega}}$$

$$= 100 = 40 \, \mathrm{dB}$$

$A_v = A_{cl} = 40 \text{ dB}$

· f2 occurs at

(a) For  $C_f = 30 \text{ pF}$ :

Draw a horizontal line on the  $A_v/f$  graph at  $A_v = 40$  dB. Where the line cuts the  $A_v/f$  characteristic for  $C_f = 30$  pF read,

$$f_2 \approx 8 \text{ kHz}$$

(b) For  $C_i = 3 \text{ pF}$ : Where the  $A_v = 40 \text{ dB}$  line cuts the  $A_v/f$  characteristic for  $C_i = 3 \text{ pF}$  read,

$f_2 \approx 80 \text{ kHz}$

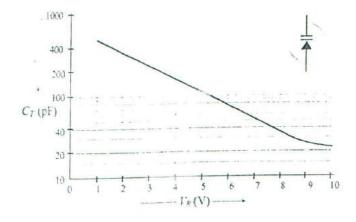

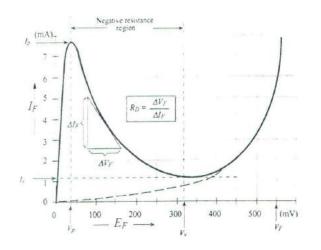

# Gain-Bandwidth Product

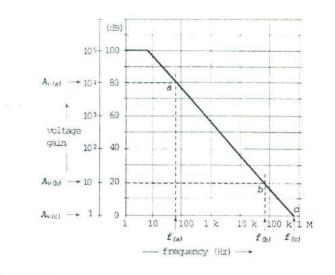

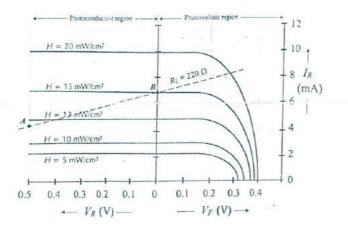

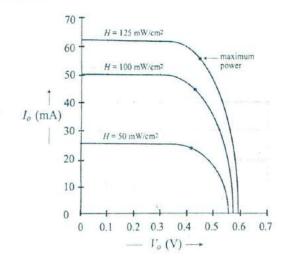

The gain-bandwidth produce (GBW), or unity-gain bandwidth, of an operational amplifier is the open-loop gain at a given frequency multiplied by the frequency. Referring to the  $A_v/f$  response for the 741 reproduced in Fig. 15-13, it is seen that at  $A_{v|av} = 10^4$ , the frequency is  $f_{av} \approx 80$  Hz. Thus,

$$GBW = A_{v(a)} \times f_{(a)} = 10^4 \times 80 \text{ Hz}$$

$$= 8 \times 10^5$$

Similarly, at  $A_{v(b)} = 10$ ,  $f_{(b)} \approx 80$  kHz, again giving  $GBW = 8 \times 10^5$ . Also, at  $A_{v(c)} = 1$ ,  $f_{(c)} \approx 800$  kHz, once more giving  $GBW = 8 \times 10^5$ . This last determination explains the term *unity-gain bandwidth*, because the *GBW* is simply equal to the frequency at which  $A_v = 1$ .

Because the high cutoff frequency for an op-amp circuit occurs when the closed-loop gain equals the open-loop gain, the circuit upper cutoff frequency can be calculated by dividing the gainbandwidth product by the closed-loop gain:

$$f_2 = \frac{GBW}{A_{CL}}$$

(15-2)

It is important to note that Eq. 15-2 applies only to operational amplifiers that have a gain/frequency response that falls off to the unity-gain frequency at 20 dB/decade. Where the  $A_v/f$  response falls off at some other rate, Eq. 15-2 cannot be used.

Figure 15-13

The gain-bandwidth product (CBW) for an operational amplifier can be used to determine the cutoff frequency for any given closed-loop gain.

### Example 15-5

Using the gain-bandwidth product, determine the cutoff frequencies for the circuit in Ex. 15-4 (reproduced in Fig. 15-14), when the compensating capacitor is (a)  $C_f = 30 \text{ pF}$ , (b)  $C_f = 3 \text{ pF}$ .

# Solution

(a) For  $C_f = 30$  pF: Referring to the LM108 A/f graph for  $C_f = 30$  pF in Fig. 15-12,

$$GBW = f$$

at  $A_i = 1$

$\approx 800 \text{ kHz}$

Eq. 15-2,

Eq. 15-2,

800 kHz

CBW

(b) For  $C_f = 3 \text{ pF}$ :

Referring to the LM108 A/f graph for  $C_f = 3$  pF in Fig. 15-12,

at  $A_v = 20 \text{ dB} = 10$ ,  $f \approx 800 \text{ kHz}$

$$GBW = f \times A_{v} = 800 \text{ kHz} \times 10$$

$$= 8 \text{ MHz}$$

$$f_{2} = \frac{GBW}{A_{Cl}} = \frac{8 \text{ MHz}}{100}$$

Figure 15-14 Amplifier circuit for Example 15-5.

### \_\_\_\_\_

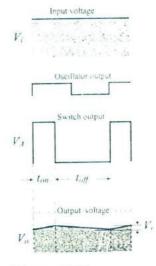

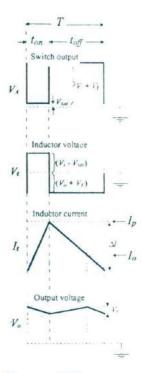

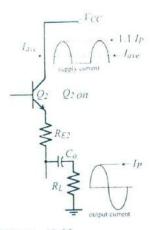

*Full-Power BW and Slew Rate* The  $A_0/f$  response graphs, upper cutoff frequencies, and *GBW* specified on op-amp data sheets normally refer to the operational amplifier performance as a small-signal amplifier. In this case, the measurements are usually made *for output amplitudes not exceeding*

$= 80 \, \text{kHz}$

100 mV peak-to-peak. Where an amplifier circuit has to produce a large output voltage, the op-amp *full-power bandwidth* ( $f_p$ ) must be used. The *AD843* operational amplifier, for example, is specified as having a typical unity gain bandwidth of 34 MHz for an output amplitude of 90 mV p-to-p, and a typical full power bandwidth of 3.9 MHz when the output amplitude is 20 V p-to-p.

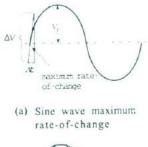

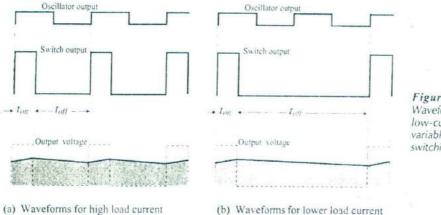

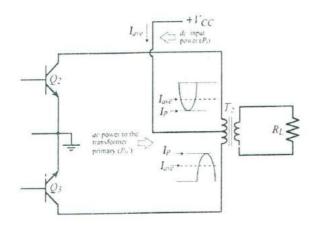

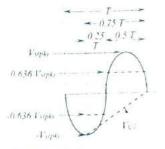

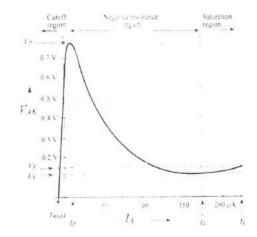

The op-amp slew rate (*SR*) (see Section 14-9) can be used to calculate the full-power bandwidth for a given output amplitude. For a sinusoidal voltage waveform, the fastest rate-of-change of voltage occurs at the point where the waveform crosses from its negative half-cycle to its positive half-cycle, and vice versa. This is illustrated in Fig. 15-15(a). It can be shown that the voltage rate-of-change at this point is,

# $\Delta V / \Delta t = 2\pi f V_p$ (volts/second)

The maximum rate-of-change of the waveform is limited by the maximum slew rate of the op-amp used. Where the waveform amplitude or frequency is higher than the limits imposed by the slew rate, distortion will occur as illustrated in Fig. 15-15(b).

(b) Sine wave distortion caused by the slew rate

### Figure 15-15

The op-amp slew-rate limits the upper cutoff frequency of an opamp circuit, and limits the output amplitude at a given frequency. The SR can be equated to the sine wave rate-of-change,

$$SR = 2\pi f_p V_p$$

(15-3)

where  $f_p$  is the slew-rate limited frequency, or full-power bandwidth, and  $V_p$  is the peak level of the circuit output voltage. Equation 15-3 can be used to determine the full-power bandwidth of an op-amp circuit for a given output voltage amplitude. Sometimes Eq. 15-3 gives an  $f_p$  value greater than that determined from the  $A_v/f$  graph or the *GBW* product. In these cases, the circuit bandwidth is still dictated by the  $A_v/f$  graph or the *GBW* product.

### Example 15-6

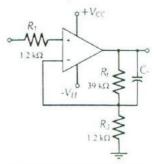

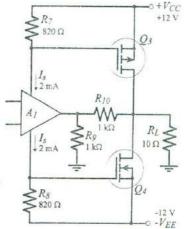

- (a) Calculate the full-power bandwidth for an AD843 op-amp circuit (Fig. 15-16), given a 1 V peak input and op-amp slew rate of 250 V/μs.

- (b) Determine the maximum peak output voltage obtainable from a 741 opamp circuit with a 100 kHz signal frequency. (SR = 0.5 V/µs for a 741.)

### Solution

(a) For the AD843:

$$V_{o(p)} = \frac{R_2 + R_3}{R_3} \times V_{n(p)} = \frac{39 \text{ k}\Omega + 4.7 \text{ k}\Omega}{4.7 \text{ k}\Omega} \times 1 \text{ V}$$

$$= 9.3 \text{ V}$$

From Eq. 15-3,  $f_p = \frac{SR}{2\pi V} = \frac{250 \text{ V/}\mu\text{s}}{2\pi v 0.23}$

$$2 \pi V_p = 2 \pi$$

$\approx 4.2 \text{ MHz}$

(b) For a 741:

From Eq. 15-3,

$$V_p = \frac{SR}{2 \pi f_p} = \frac{0.5 \text{ V/}\mu\text{s}}{2 \pi \text{ x 100 kHz}}$$

= 0.79 V

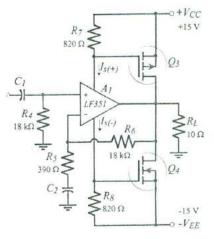

# R<sub>7</sub> +V<sub>CC</sub> 4.7 kΩ +15 V -V<sub>FE</sub> 39 kΩ -15 V -15 V

Figure 15-16 Amplifier circuit for Example 15-6.

### Practise Problems

- 15-3.1 Determine the typical upper cutoff frequency for an inverting amplifier with a closed-loop gain of 15 using a 741 op-amp. The A<sub>v</sub>/f graph for the 741 is shown in Fig. 15-13.

- 15-3.2 Using the gain-bandwidth product, calculate the cutoff frequencies for an inverting amplifier with a closed-loop gain of 30 when the opamp used is (a) 741, (b) an AD843.

- 15-3.3 Calculate the full-power bandwidth for an *LF353* op-amp circuit, with a 14 V peak-to-peak output voltage.

# 15-4 Stray Capacitance Effects

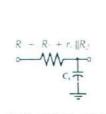

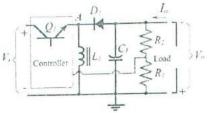

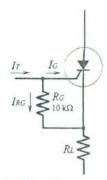

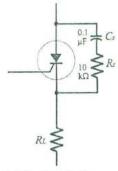

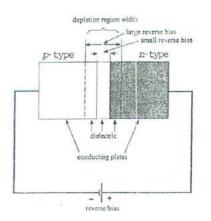

Stray capacitance  $(C_s)$  at the input terminals of an operational amplifier effectively introduces an additional phase-lag network in

the feedback loop, (see Fig. 15-17), thus making the op-amp circuit unstable. Stray capacitance problems can be avoided by good circuit construction techniques that keep the stray to a minimum. The effects of stray capacitance also depend upon the resistor values used in the feedback network. High resistance values make it easier for small stray capacitances to produce phase lag. With low-resistances, small stray capacitances normally have little effect on the circuit stability.

(a) Stray capacitance  $(C_3)$  at amplifier input

(b) C, and its series resistance

Analysis of an *RC* phase lag circuit shows that the capacitor voltage lags the input voltage by 45° when the capacitor impedance (*X*<sub>c</sub>) equal the series resistance (*R*). Also, when *X*<sub>c</sub> = 10 *R*, the phase lag is approximately 10°, and it is this 10° of additional phase lag that might make the circuit oscillate if its phase margin is already close to the minimum for stability. If the phase margin is known to be large at the frequency where  $A_c B = A_{CL}$  (the frequency at which the circuit is likely to oscillate), the stray capacitance might be unimportant. Where the phase margin is small, for circuit stability the op-amp input stray capacitance should normally be much less than.

$$C_s = \frac{1}{2 \pi f(10 \text{ R})}$$

(15-4)

where *R* is the equivalent resistance in series with the stray capacitance. In Fig. 15-17,  $R = R_3 + (R_1 + r_s) ||R_2$ .

From Eq. 15-4 it is seen that (as already mentioned) the larger resistor values the smaller the stray capacitance that can produce circuit instability. If the signal source is disconnected from the circuit, *R* becomes equal to  $(R_2 + R_3)$ , which is much larger than  $[R_3 + (r_s + R_j)]|R_2|$ . In this situation, extremely small stray capacitance values can make the circuit unstable.

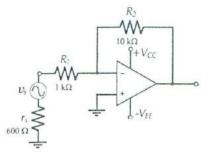

Miller-effect compensation can be used to compensate for stray capacitance at an op-amp input, as shown in Fig. 15-18. To eliminate the phase shift introduced by the stray capacitance the division of the output voltage produced by  $C_S$  and  $C_2$  in series should be equal to the division produced by  $R_1$  and  $R_2$ . Therefore,

$$\frac{X_{\rm CS}}{X_{\rm C2}} = \frac{R_1}{R_2}$$

Figure 15-18 Use of Miller-effect compensation for stray capacitance at the input terminals of an op-amp.

This gives,

$$C_2 R_2 = C_S R_1$$

$$(15-5)$$

Note that Eq. 15-5 does not allow for  $r_s$  or  $R_3$  in Fig. 15-17. Where  $r_s$  is not very much smaller than  $R_i$ , it must be added to  $R_i$ . Also, resistor  $R_3$  could be bypassed with another capacitor to reduce the total series resistance.

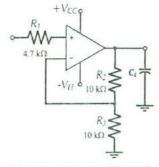

# Example 15-7

Calculate the op-amp input terminal stray capacitance that might cause instability in the circuit of Fig. 15-19 if the amplifier cutoff frequency is 800 kHz. Also, determine a suitable Miller-effect compensating capacitor value.

### Solution

Stray capacitance:

Eq. 15-4,

$$C_{s} = \frac{1}{2 \pi f \times 10[(r_{s} + R_{t}) ||R_{s}]}$$

$$= \frac{1}{2 \pi \times 800 \text{ kHz} \times 10 [(690 \ \Omega + 1 \ \text{k}\Omega) ||10 \ \text{k}\Omega}$$

$$= 14.4 \text{ pF}$$

Compensation:

Eq. 15-5, C.

$$= \frac{C_s (r_s + R_l)}{R_2} = \frac{14.4 \text{ pF x } (600 \ \Omega + 1 \text{ k}\Omega)}{10 \text{ k}\Omega}$$

$$= 2.3 \text{ pF}$$

*Figure 15-19* Op-amp amplifier circuit for Example 15-7.

# Practise Problems

- 15-4.1 Determine the op-amp input stray capacitance that might cause instability in an inverting amplifier with  $R_1 = 1.8 \text{ k}\Omega$ ,  $R_2 = 560 \text{ k}\Omega$ , and  $f_2 = 600 \text{ kHz}$ ; (a) when the signal source is open-circuited, (b) when  $r_s = 600 \Omega$ , and  $R_1$  and  $R_2$  are reduced by a factor of 10.

- 15-4.2 Determine a suitable Miller-effect compensating capacitor value for the circuit in part (b) of Problem 15-4.1.

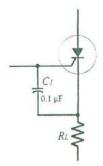

# 15-5 Load Capacitance Effects

Capacitance connected at the output of an operational amplifier is termed *load capacitance*  $(C_l)$ . Figure 15-20 shows that  $C_L$  is in series with the op-amp output resistance  $(r_o)$ , so  $C_L$  and  $r_o$  constitute a phase-lag circuit in the feedback network. As in the case of stray capacitance, another 10° of phase lag introduced by  $C_L$  and  $r_o$  could cause circuit instability where the phase margin is already small. The equation for calculating the load capacitance; that might cause instability is similar to that for stray capacitance;

$$C_L = \frac{1}{2 \pi f(10r_c)}$$

(15-6)

In Eq. 15-6 *f* is the frequency at which  $A_v B = A_{CL}$ . If  $r_o$  is reduced, Eq 15-6 gives a larger  $C_L$  value. Thus, an op-amp with a low output resistance can tolerate more load capacitance than one with a higher output resistance.

### Figure 15-20

Load capacitance at an op-amp output can cause instability by introducing additional phase lag in the feedback network.

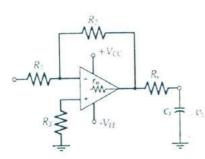

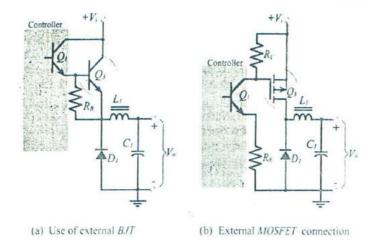

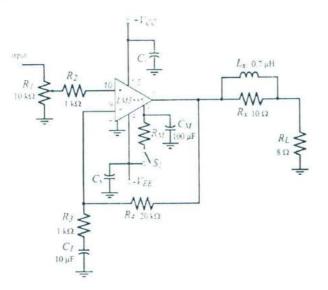

One method often used to counter instability caused by load capacitance is shown in Fig. 15-21(a). A resistor ( $R_x$ ), usually ranging from 12  $\Omega$  to 400  $\Omega$ , is connected in series with the load capacitance. The presence of  $R_x$  (with  $R_2$  connected at the op-amp or.tput) can severely reduce the phase lag produced by  $r_o$  and  $C_t$ . However,  $R_x$  also has the undesirable effect of increasing the circuit output impedance to approximately the resistance of  $R_x$ .

(a) Use of  $R_x$  to reduce phase lag

(c) Inverting amplifier with combination of  $R_x$  and  $C_2$  for  $C_L$  compensation

(b) Miller-effect compensation for CL

Figure 15-21 Compensation methods for load capacitance.

(d) Noninverting amplifier with  $R_x C_2$ combination for  $C_L$  compensation A Miller-effect capacitor ( $C_2$ ) connected across feedback resistor  $R_2$  may be used to compensate for the load capacitance. [see Fig. 15-21(b)]. In this case,  $C_2$  introduces some phase-lead in the feedback network to counter the phase-lag. The equation for calculating a suitable capacitance for  $C_2$  is, once again, similar to that for stray capacitance;

$$C_2 R_2 = C_L r_o$$

(15-7)

A modified form of Miller-effect compensation for load capacitance is shown in Fig. 15-21(c). An additional resistor  $(R_x)$  is included in series with  $C_L$  to reduce the phase lag, as discussed. But now,  $R_2$  is connected at the junction of  $R_x$  and  $C_L$ , so that (because of feedback)  $R_x$  has no significant effect on the circuit output impedance. Also,  $C_2$  is connected from the op-amp output terminal to the inverting input. With this arrangement, Eq. 15-7 is modified to,

$$C_2 R_2 = C_L (r_0 + R_x) \tag{15-8}$$

It should be noted from Equations 15-7 and 15-8 that, as for stray capacitance, smaller resistance values for  $R_2$  give larger, more convenient, compensating capacitor values.

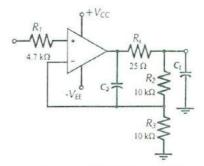

### Example 15-8

Calculate the load capacitance that might cause instability in the circuit of Fig. 15-22(a) if the amplifier cutoff frequency is 2 MHz and its output resistance is 25  $\Omega$ . Also, determine a suitable compensating capacitor value for the circuit as modified in Fig. 15-22(b) with a 0.1  $\mu$ F load capacitance.

### Solution

Load capacitance:

Eq. 15-6,

$$C_{L} = \frac{1}{2 \pi f (10 r_{o})} = \frac{1}{2 \pi x 2 \text{ MHz} \times 10 \times 25 \Omega}$$

$$= 318 \text{ pF}$$

Compensation:

$$C_2 = \frac{C_1 (r_0 + R_x)}{R_2} = \frac{0.1 \,\mu\text{F} \,x \,(25 \,\Omega + 25 \,\Omega)}{10 \,\text{k}\Omega}$$

$$= 500 \,\text{pF} \text{ (standard value)}$$

# Practise Problems

15 -5.1 Calculate the load capacitance that might cause instability in the circuit in Ex. 15-7 if the op-amp output resistance is 20 Ω. Determine a suitable Miller-effect compensating capacitor value.

15-5.2 The circuit is Problem 15-5.1 is modified as in Fig. 15-21(c) with  $R_x = 5 R_0$  and  $C_1 = 0.5 \mu$ F. Calculate the required  $C_2$  value.

(a) Noninverting amplifier with load capacitance (C<sub>L</sub>)

(b) Amplifier compensated with R<sub>x</sub> and C<sub>2</sub>

### Figure 15-22 Circuits for Example 15-8.

# 15-6 Circuit Stability Precautions

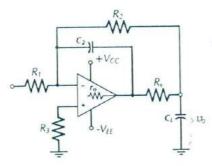

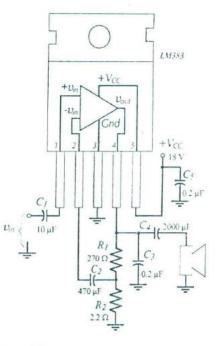

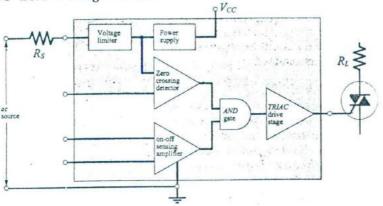

### Power Supply Decoupling

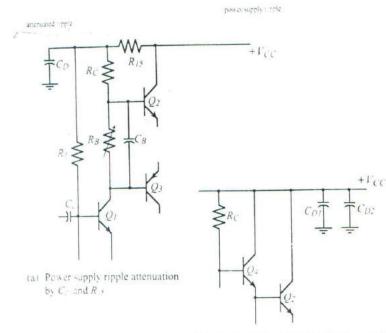

Feedback along supply lines is another source of op-amp circuit instability. This can be minimized by connecting 0.01  $\mu$ F high-frequency capacitors from each supply terminal to ground (see Fig. 15-23). The capacitors must be connected as close as possible to the *IC* terminals. Sometimes larger-value capacitors are required.

### Figure 15-23

For op-amp circuit stability, keep resistor values to a minimum, use the recommended compensating components, bypass the supply terminals to ground, and keep the signal source connected

### Stability Precautions

The following precautions should be observed for circuit stability:

- 1. Where low-frequency performance is required, use an internally compensated op-amp. Alternatively, use Miller-effect compensation to give the lowest acceptable cutoff frequency.

- 2. Use small-value resistors in the feedback network, if possible, instead of using the largest possible resistor values.

- 3. With an op-amp that must be compensated, use the methods and components recommended by the *IC* manufacturer.

- 4. Keep all component leads as short as possible, and take care with component placement. A resistors connected to an opamp input terminal should have the resistor body placed close to the input terminal.

- 5. Use 0.01  $\mu$ F capacitors (or 0.1  $\mu$ F capacitors if necessary) to bypass the supply terminals of op-amp (or groups of op-amps) to ground. Connect these capacitors close to the *ICs*.

- 6. Always have a signal source connected to a circuit being tested. Alternatively, ground the circuit input. With an open-circuited input, very small stray capacitances can cause instability.

- Do not connect oscilloscopes or other instrument at the opamp input terminals. Instrument input capacitance can cause instability.

- 8. If a circuit is unstable after all of the above precautions have been observed, reduce the value of all circuit resistors (except compensating resistors). Also, reduce the signal source resistance if possible.

# Chapter-15 Review Questions

# Section 15-1

- 15-1 Show how feedback in an op-amp inverting amplifier can produce instability. Explain the conditions necessary for oscillations to occur in an op-amp circuit.

- 15-2 Show how feedback in an op-amp noninverting amplifier circuit can produce instability.

- 15-3 Define: loop gain, loop phase shift, phase margin.

- 15-4 Sketch typical gain/frequency response and phase/ frequency response graphs for an uncompensated operational amplifier. Identify the pole frequencies and rates of fall of voltage gain, and show the typical phase shift at each pole frequency.

- 15-5 Sketch typical gain/frequency response and phase/ frequency response graphs for a compensated operational amplifier. Briefly explain.

- 15-6 Derive an equation for the open-loop gain of an operational amplifier when the loop gain equals 1.

### Section 15-2

- 15-7 Sketch a lag compensation circuit. Explain its operation and show how it affects the frequency and phase response graphs of an operational amplifier.

- 15-8 Sketch a lead compensation circuit. Explain its operation and show how it affects the frequency and phase response graphs of an operational amplifier.

- 15-9 Show how Miller-effect compensation can be applied to an op-amp circuit. Briefly explain.

### Section 15-3

- 15-10 Define bandwidth, gain-bandwidth product, and fullpower bandwidth for an operational amplifier. Explain the circuit conditions that apply in each case.

- 15-11 Define slew-rate, and explain its effect on the output waveform from an operational amplifier.

### Section 15-4

- 15-12 Discuss the effects of stray capacitance at the input terminals of an operational amplifier. Explain the precautions that should be observer to deal with input stray capacitance problems.

- 15-13 Show how Miller-effect compensation can be used to counter the effects of op-amp input stray capacitance.

### Section 15-5

15-14 Discuss the effects of op-amp load capacitance.

15-15 Show how op-amp instability due to load capacitance can be countered by means of: an additional resistor, Miller-effect compensation, a combination of both.

### Section 15-6

15-16 List precautions that should be observed for operational amplifier circuit stability. Briefly explain in each case.

# Chapter-15 Problems

# Section 15-1

- 15-1 Investigate the stability of the circuit in Fig. 15-11, if the *LM108* is replaced with an op-amp that has the gain/ frequency and phase/frequency responses in Fig. 15-2.

- 15-2 Investigate the stability of the inverting amplifier circuit in Fig. 15-10(a) if the op-amp used is (a) a 741, (b) an *AD843*. Use the response graphs in Fig. 15-3 and 15-4.

- 15-3 Investigate the stability of an amplifier circuit with  $A_{CL}$  = 70 dB if the op-amp has the gain/frequency and phase/ frequency responses in Fig. 15-2.

### Section 15-2

- 15-4 The phase-lag network in Fig. 15-7(a) has:  $R_1 = 8.2 \text{ k}\Omega$ .  $R_2 = 470 \Omega$ , and  $C_1 = 3300 \text{ pF}$ . Calculate the approximate phase lag at 7.5 kHz and at 750 kHz.

- 15-5 The phase-lead network in Fig. 15-7(c) has:  $R_1 = 560 \Omega$ ,  $R_2 = 27 k\Omega$ , and  $C_1 = 1000 \text{ pF}$ . Calculate the approximate phase lead at 6 kHz and 300 kHz.

- 15-6 If the circuit in Fig. 15-22(a) uses an *LM108* op-amp. determine suitable compensation capacitor values. Refer to the *LM108* information in Fig. 15-8.

- 15-7 Calculate a suitable Miller-effect compensating capacitor to stabilize the circuit in Fig. 15-19 at an 80 kHz cutoff frequency.

- 15-8 The circuit in Fig. 15-10(b) is to be stabilized at  $f_2 = 50$  kHz. Determine the value of a suitable Miller-effect compensating capacitor.

### Section 15-3

- 15-9 Determine the bandwidth of the circuit in Fig. 15-10(a) if the op-amp has the gain/frequency response graph in Fig. 15-2. Also, determine the bandwidth of the circuit in Fig 15-10(b) if the op-amp is a 741.

- 15-10 Find the upper cutoff frequency for the circuit in Fig. 15-19 if the op-amp is (a) a 741, (b) an AD843. Use the response graphs in Fig. 15-3 and 15-4.

# 526 Electronic Devices and Circuits, 4th ed.

- 15-11 Using the gain-bandwidth product, determine the upper cutoff frequencies for the circuits in Problem 15-10.

- 15-12 Use the gain-bandwidth product to determine the upper cutoff frequencies for the circuits in Figs. 15-10(a) and (b) if they both have *LM108* op-amps with  $C_f$  = 30 pF.

- 15-13 The circuits in Examples 14-5 and 14-8 use 741 op-amps. Use the gain-bandwidth product to determine the upper cutoff frequency for each circuit.

- 15-14 If the circuit in Fig. 15-11 has the *LM108* replaced with an *LF353*, use the gain-bandwidth product to determine the upper cutoff frequency.

- 15-15 Calculate the full-power bandwidth for an amplifier using 741 op-amp if the output voltage is to be (a) 5 V peak-to-peak. (b) 1 V peak-to-peak.

- 15-16 Recalculate the full power bandwidth in each case in Problem 15-15 if the 741 is replaced with an *LF353*.

- 15-17 Calculate the full-power bandwidth for the circuit in Example 14-5 if the peak output is to be 2 V. Also, determine the maximum peak output voltage that can be produced by the circuit at the cutoff frequency calculated in Problem 15-13.

- 15-18 Calculate the slew-rate limited cutoff frequency for the circuit in Example 14-8 if the peak input is 20 mV. Also, determine the maximum peak output voltage at the circuit cutoff frequency calculated in Problem 15-13.

# Section 15-4

- 15-19 A circuit as in Fig. 15-10(a) with  $C_f$  removed has a cutoff frequency of 600 kHz. Determine the op-amp input stray capacitance that might cause instability; (a) when the signal source is open-circuited, (b) when a 300  $\Omega$  signal source is connected.

- 15-20 Determine the input stray capacitance that might make the circuit in Fig. 15-10(b) become unstable when a 300  $\Omega$  signal source is connected. Assume that the circuit cutoff frequency is 30 kHz and that  $C_f$  is removed.

- 15-21 Calculate the Miller-effect capacitor value required to compensate for 250 pF of input stray capacitance in the circuitry of Problem 15-19(b).

- 15-22 Calculate the Miller-effect capacitor value required to compensate for 90 pF of stray capacitance in the circuit of Problem 15-20.

- 15-23 An inverting amplifier (as in Fig. 15-19) uses a *LF353* opamp, and has:  $r_s = 600 \Omega$ ,  $R_1 = 220 k\Omega$ ,  $R_2 = 2.2 M\Omega$ ,  $f_2 =$ 18 kHz. Calculate the input stray capacitance that might make the circuit unstable; (a) when the signal source is

connected, (b) when the signal source is open-circuited.

15-24 Repeat Problem 15-23 when  $R_1$  and  $R_2$  are each reduced by a factor of 10.

# Section 15-5

- 15-25 Determine the load capacitance that might cause instability in the circuit in Fig. 15-10(a) with  $C_f$  removed, if the circuit cutoff frequency is 600 kHz, and  $r_o = 100 \Omega$ .

- 15-26 An inverting amplifier (as in Fig. 15-19) uses an op-amp with a 300  $\Omega$  output resistance, and has;  $R_1 = 220 \text{ k}\Omega$ ,  $R_2 = 2.2 \text{ M}\Omega$ . Calculate the load capacitance that might make the circuit unstable.

- 15-27 Calculate the Miller-effect capacitor value required to compensate for a 0.1  $\mu$ F load capacitance in the circuit of Fig. 15-10(a) if  $f_2 = 600$  kHz.

- 15-28 Calculate the Miller-effect capacitor value required to compensate for the load capacitance in Problem 15-26.

- 15-29 Determine the load capacitance that might cause instability in the circuit in Fig. 15-22(a), if the cutoff frequency is 400 kHz, and the op-amp has  $r_o = 150 \Omega$ .

- 15-30 The circuit in Problem 15-29 is rearranged as in Fig. 15-22(b) with  $R_x = 10 r_o$ . Calculate the required  $C_2$  value to compensate for a 5000 pF load capacitance.

# Practise Problem Answers

15-1.1 30°, 90°, 90° 15-2.1 -48.5°, 41.5° 15-2.2 82 pF 50 kHz 15-3.1 15-3.2 27 kHz, 1.13 MHz 296 kHz 15-3.3 0.05 pF, 34.5 pF 15-4.1 15-4.2 0.5 pF 995 pF, 2 pF 15-5.1 15-5.2 6000 pF

528 Electronic Devices and Circuits, 4th ed.

and Circuits, 4th ed.

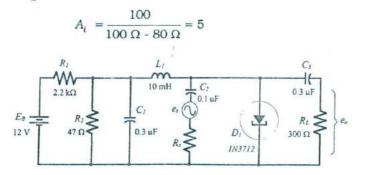

# Chapter 16 Signal Generators

# Chapter Contess

Introduction 16-1 Phase Shift Octators 530 16-2 Colpitts Oscillars 534 16-3 Hartley Oscillars 538 16-4 Wein Bridge Octator 541 16-5 Oscillator Ampude Stabilization 543 16-6 Square Wave merator 548 16-7 Triangular Was Generator 550 16-8 Oscillator Freency Stabilization 553 Review Questions 58 Problems 559 Practise Problem Amers 561

# Objectives

You will be able to:

- 1 Draw the following pes of sine wave oscillator chits, and explain the operation of a Phase shift. Colpitts, Hartley in bridge

- Analyze each operabove oscillator circuits to determ the oscillation frequency.

- 3 Design each of thebove oscillator circuits to produce specified output frequency.

- Sketch oscillator elitude stabilization circa and explain their operation.

- 5 Design circuits init oscillator outputs to a speed amplitude.

- 6 Draw square use and triangular wave generator wits. Sketch the circuit waveformend explain the operation of early uit.

- 7 Analyze square and triangular waveform generators to determine the amplitude and frequency of the output waveform.

- 8 Design square and triangular waveform generators to produce a specified output amplitude and frequency.

- 9 Explain plezoelectric crystals, sketch the crystal equivalent circuit, and the crystal impedance/frequency graph.

- 10 Show how crystals may be used for oscillator frequency stabilization, and design crystal-controlled oscillators.

# 5 3 0 ---- Electronic Devices and Circuits, 4th ed.

### Introduction

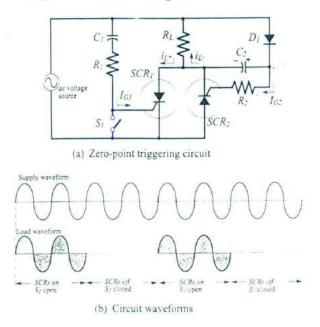

A sinusoidal oscillator usually consists of an amplifier and a phase-shifting network. The amplifier receives the output from the network, amplifies it, phase shifts it by 180°, and applies it to the network input. The network phase shifts the amplifier output by a further 180°, and attenuates it before feeding it back to the amplifier input. When the amplifier gain equals the inverse of the network attenuation, and the amplifier phase shift equals the network phase shift, the circuit is amplifying an input to produce an output which is attenuated to become the input. The circuit is generating its own input signal, and a state of oscillation exists.

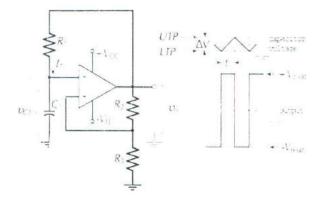

Some signal generators produce square or triangular waveforms. These normally use nonlinear circuits and resistor/capacitor charging circuits.

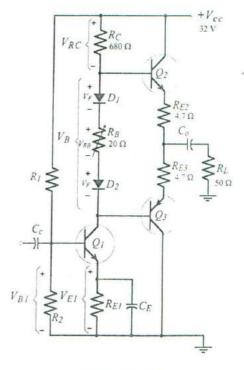

# 16-1 Phase Shift Oscillators

# Op-Amp Phase Shift Oscillator

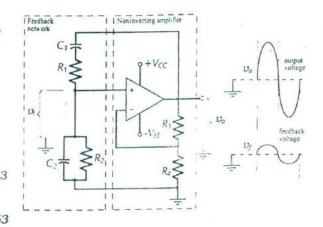

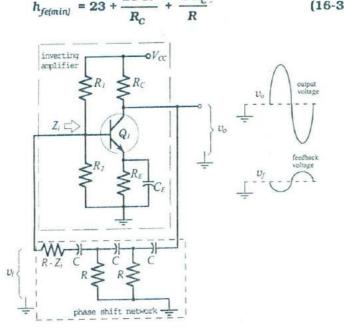

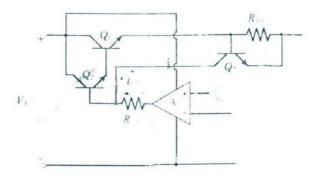

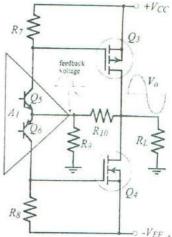

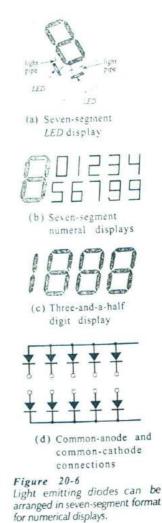

Figure 16-1 shows the circuit of a *phase shift oscillator*, which consists of an inverting amplifier and an *RC* phase-shifting network. The amplifier phase-shifts its input by  $-180^{\circ}$ , and the *RC phase-lead* network phase-shifts the amplifier output by a  $+180^{\circ}$ , giving a total loop phase shift of zero. The attenuated feedback signal (at the amplifier input) is amplified to reproduce the output. In this condition the circuit is generating its own input signal, consequently, it is oscillating. The output and feedback voltage waveforms in Fig. 16-1 illustrate the circuit operation.

For a state of oscillation to be sustained in any sinusoidal oscillator circuit, certain conditions, known as the Barkhausen criteria, must be fulfilled:

The loop gain must be equal to (or greater than) one. The loop phase shift must be zero.

The *RC* phase-lead network in Fig. 16-1 consists of three equalvalue resistors and three equal-value capacitors. Resistor  $R_1$ functions as the last resistor in the *RC* network and as the amplifier input resistor. A *phase-lag* network would give a total loop phase shift of -360°, and so it would work just as well as the phase lead network.

The frequency of the oscillator output depends upon the component values in the *RC* network. The circuit can be analyzed to show that the phase shift is 180° when

$$X_c = \sqrt{6} R$$

This gives an oscillation frequency.

$$f = \frac{1}{2 \pi R C \sqrt{6}}$$

(16-1)

As well as phase shifting the amplifier output, the RC network

attenuates the output. It can be shown that, when the required 180° phase shift is produced, the feedback factor (*B*) is always 1/29. This means that the amplifier must have a closed-loop voltage gain ( $A_{Cl}$ ) of at least 29 to give a loop gain ( $B A_{Cl}$ ) of one; otherwise the circuit will not oscillate. For example, if the amplifier output voltage is 10 V, the feedback voltage is,

$$v_{\rm f} = B v_{\rm o} = 10 \, {\rm V}/29$$

To reproduce the 10 V output,  $v_f$  must be amplified by 29.

$$v_o = A_{CL} v_f = 29 \times (10 \text{ V}/29)$$

= 10 V

If the amplifier voltage gain is much greater than 29, the output waveform will be distorted. When the gain is slightly greater than 29, a reasonably pure sine wave output can be expected. The gain is usually designed to be just over 29 to ensure that the circuit oscillates. The output voltage amplitude normally peaks at  $\pm(V_{CC} - 1 \text{ V})$ , unless a rail-to-rail op-amp is used (see Section 14-9).

### Figure 16-1

A phase shift oscillator consists of an inverting amplifier and an RC phase shifting feedback network. The RC network attenuates the output and phase shifts it by 180°. The amplifier amplifies the network output and phase shifts it through a further 180°.

### Circuit Design

Design of a phase shift oscillator begins with design of the amplifier to have a closed-loop gain just greater than 29. The resistor values for the *RC* network are then selected equal to the amplifier input resistor ( $R_1$ ), and the capacitor values are calculated from Eq. 16-1. In some cases, this procedure might produce capacitor values not much larger than stray capacitance. So, alternatively, the design might start with selection of convenient capacitor values. Equation 16-1 is then used to calculate the resistance of *R* (and  $R_1$ ). Finally,  $R_2$  is selected to give the required amplifier gain.

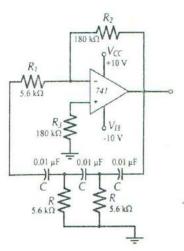

### Example 16-1

Using a 741 op-amp with a  $\pm 10$  V supply, design the phase shift oscillator in Fig. 16-2 to produce a 1 kHz output frequency.

# Solution

Select

$$I_{1} \approx 100 \times I_{B(max)} = 100 \times 500 \text{ nA}$$

= 50 \mu A

$$v_{o} \approx \pm (V_{CC} - 1 \text{ V}) \approx \pm (10 \text{ V} - 1 \text{ V})$$

\approx \pm 9 \textbf{V}

$$v_{i} = \frac{v_{o}}{A_{CL}} = \frac{\pm 9 \text{ V}}{29}$$

= \pm 0.31 \textbf{V}

$$R_{1} = \frac{v_{i}}{I_{1}} = \frac{0.31 \text{ V}}{50 \mu \text{ A}}$$

= 6.2 k\Omega (use 5.6 k\Omega standard value)

$$R_{2} = A_{CL}R_{1} = 29 \times 5.6 \text{ k\Omega}$$

\approx 162 k\Omega (use 180 k\Omega to give A\_{CL} > 29)

$$R_{3} = R_{2} = 180 \text{ k\Omega} (\text{the } dc \text{ path through } R_{1} \text{ is interrupted by } C)$$

$$R = R_{1} = 5.6 \text{ k\Omega}$$

1,

$$C = \frac{1}{2 \pi R f \sqrt{6}} = \frac{1}{2 \pi \times 5.6 \text{ k\Omega x 1 kHz} \times \sqrt{6}}$$

From Eq. 16-1

Although the 741 op-amp used in Ex. 16-1 is likely to be quite

$\approx 0.01 \,\mu\text{F}$  (standard value)

suitable for the particular circuit, some care should always be taken when selecting an operational amplifier. It should be recalled (from Ch. 15) that when a large output voltage swing is required, the op-amp full-power bandwidth is involved. This must be considered when selecting an operational amplifier for an oscillator circuit.

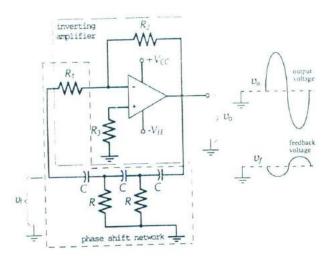

### **BJT** Phase Shift Oscillator

A phase shift oscillator using a single BJT amplifier is shown in Fig. 16-3. Once again, the amplifier and phase shift network each produce 180° of phase shift, the BJT amplifies the network output, and the network attenuates the amplifier output.

First thoughts about this circuit (in comparison to the op-amp phase shift oscillator) would suggest that a BJT amplifier with a voltage gain of 29 is required. An attempt to design such a circuit

Figure 16-2 Phase shift oscillator circuit for Example 16-1.

(16-3)

reveals that in many cases the amplifier output is overloaded by the phase shift network, or else the network output is overloaded by the amplifier input. The problem can be solved by including an emitter follower in the circuit. However, the circuit can function satisfactorily without any additional components if the transistor is treated as a current amplifier, rather than as a voltage amplifier. In this case, circuit analysis gives,

$$f = \frac{1}{2 \pi R C \sqrt{6 + 4R_{\rm C}/R}}$$

(16-2)

and.

Figure 16-3 Phase shift oscillator using an inverting BJT amplifier and an RC feedbacknetwork.

The circuit oscillates only if the BJT current gain is equal to (or larger than) the minimum value determined from Eq. 16-3. With R =  $R_c$ , a minimum  $h_{fe}$  of 56 is required to sustain circuit oscillation. With  $R = 10 R_c$ ,  $h_{fe(min)}$  must be greater than 300. The output waveform is likely to be distorted if  $h_{fe}$  is substantially greater than the calculated  $h_{fe(min)}$ . Because  $h_{fe}$  varies widely from one transistor to another,  $R_c$  should be partially adjustable to minimize distortion. Note that in Fig. 16-3, the amplifier input resistance  $(Z_i)$ constitutes part of the last resistor in the phase shift network.

### Circuit Design

BJT phase shift oscillator design should be approached by first selecting R equal to or greater than the estimated amplifier  $Z_i$ . Then,  $R_c$  is selected equal to R, C is calculated from Eq. 16-2, and the rest of the component values are determined for the circuit dcconditions. The impedance of  $C_E$  should be much lower than  $h_{ie}/(1$ +  $h_{fc}$ ) at the oscillating frequency.

# Practise Problems

- 16-1.1 Using a BIFET op-amp with rail-to-rail operation, design a phase shift oscillator to produce a 6.5 kHz, ±12 V output.

- 16-1.2 Design a *BJT* phase shift oscillator, as in Fig. 16-3, to produce a 900 Hz waveform with a 10 V peak-to-peak amplitude. Assume that the *BJT* has  $h_{te(m,n)} \approx 60$  and  $h_{ie} \approx 1.5 \text{ k}\Omega$ .

# 16-2 Colpitts Oscillators

# Op-Amp Colpitts Oscillator

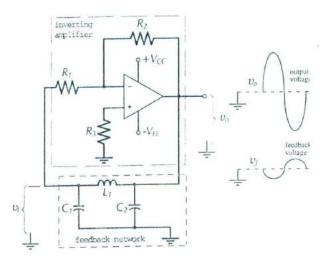

The *Colpitts oscillator* circuit show in Fig. 16-4 is similar to the opamp phase shift oscillator, except that an *LC* network is used to produce the necessary phase shift in the feedback voltage. In this case, the *LC* network acts as a filter that passes the oscillating frequency and blocks all other frequencies. The filter circuit resonates at the required oscillating frequency. For resonance,

$$X_L = X_{CT}$$

where  $X_{CT}$  is the total capacitance in parallel with the inductor. This gives the resonance frequency (and oscillating frequency) as,

$$f = \frac{1}{2 \pi \sqrt{(L_1 C_1)}}$$

(16-4)

Capacitors  $C_1$  and  $C_2$  are connected in series across  $L_1$ ; so,

$$C_T = \frac{C_1 C_2}{C_1 + C_2} \tag{16-5}$$

Consideration of the *LC* network shows that its attenuation (from the amplifier output to input) is due to the voltage divider effect of *L* and  $C_1$ . This gives,

$$B = \frac{X_{CI}}{X_{LI} - X_{CI}}$$

It can be shown that the required 180° phase shift occurs when

$$X_{C2} = X_{L1} - X_{C1}$$

and this gives.

$$B = \frac{X_{C1}}{X_{C2}} = \frac{C_2}{C_1}$$

As in the case of all oscillator circuits, the loop gain must be a minimum of one to ensure oscillation. Therefore,

$$A_{CL(min)} B = 1$$

OF,

$$min) = \frac{C_1}{C_2}$$

(16-6)

When deriving the above equations, it was assumed that the inductor coil resistance is very much smaller than the inductor impedance; that is, that the coil Q factor ( $\omega L/R$ ) is large. This must be taken into considered when selecting an inductor. It was also assumed that the amplifier input resistance is much greater than the impedance of  $C_1$  at the oscillating frequency. Because of the inductor resistance and the amplifier input resistance, and because of stray capacitance effects when the oscillator operates at a high-frequency, the amplifier voltage gain usually has to be substantially larger than  $C_1/C_2$ .

### Figure 16-4

A Colpitts oscillator consists of an inverting amplifier and an LC phase shifting feedback network.

### Circuit Design

Colpitts oscillator design can commence with selection of the smallest capacitor ( $C_2$ ) much larger than stray capacitance, or with selection of a convenient value of L. To keep the amplifier input voltage to a fairly low level, the feedback network is often designed to attenuate the output voltage by a factor of 10. This requires that  $C_1/C_2 \approx 10$ . (It should be recalled that large  $A_{CL}$  values require larger op-amp bandwidths.) Also,  $X_{C2}$  should be much larger than the amplifier output impedance. Using the desired oscillating frequency, L can be calculated from Eq. 16-4. Amplifier input resistor  $R_1$  must be large enough to avoid overloading the feedback network, ( $R_1 \gg X_{Cl}$ ). Resistor  $R_2$  is determined from  $A_{CL}$  and  $R_1$ .

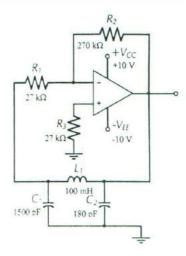

### Example 16-2

Design the Colpitts oscillator in Fig. 16-5 to produce a 40 kHz output frequency. Use a 100 mH inductor and an op-amp with a  $\pm$ 10 V supply.

1

# Solution

From Eq. 1

# From Eq. 16-4

From Eq. 16-4,

$$C_T = \frac{1}{4 \pi^2 f^2 L} - 4 \pi^2 x (40 \text{ kHz})^2 x 100 \text{ mH}$$

= 153.8 pF

For C,  $\approx 10 C_2$ ,  $C_1 \approx 10 C_T = 10 x 153.8 \text{ pF}$

$\approx 1538 \text{ pF}$  (use 1500 pF standard value)

From Eq. 16-5,  $C_2 = \frac{1}{(1/C_T) - (1/C_T)} = \frac{1}{(1/158.3 \text{ pF}) - (1/1500 \text{ pF})}$

= 177 pF (use 180 pF standard value)

$X_{C2} = \frac{1}{2 \pi f C_2} = \frac{1}{2 \pi x 40 \text{ kHz} x 180 \text{ pF}}$

= 22 kΩ

1

$$X_{C2} >> Z_{o} \text{ of the amplifier}$$

$$X_{C1} = \frac{1}{2 \pi f C_{1}} = \frac{1}{2 \pi x + 0 \text{ kHz } x + 1500 \text{ pF}}$$

$$= 2.65 \text{ k}\Omega$$

Select

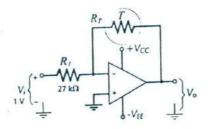

$$R_1 >> X_{C1}$$

$$R_1 = 10 X_{C1} = 10 \times 2.65 \text{ k}\Omega$$

$$= 26.5 \text{ k}\Omega \text{ (use } 27 \text{ k}\Omega \text{ standard value)}$$

From Eq. 16-6,

$$A_{Cl(min)} = \frac{C_1}{C_2} = \frac{1500 \text{ pF}}{180 \text{ pF}}$$

= 8.33

$$R_2 = A_{\Omega} R_1 = 8.33 \times 27 \text{ k}\Omega$$

$$= 225 \text{ k}\Omega \text{ (use } 270 \text{ k}\Omega \text{ standard value)}$$

$$R_3 = R_1 ||R_2 = 27 \text{ k}\Omega||270 \text{ k}\Omega$$

$$= 24.5 \text{ k}\Omega \text{ (use } 27 \text{ k}\Omega \text{ standard value)}$$

The op-amp full-power bandwidth ( $f_p$ ) must be a minimum of 40 kHz when  $v_o$  $\approx \pm 9$  V and  $A_{CL} = 8.33$ .

| from Eq. 15-2, | $f_2 = A_{CL} \times f_p = 8.33 \times 40 \text{ kHz}$<br>= 333 kHz               |

|----------------|-----------------------------------------------------------------------------------|

| from Eq. 15-3, | $SR = 2 \pi f_p v_p = 2 \pi \times 40 \text{ kHz} \times 8 \text{ V}$<br>= 2 V/µs |

|                |                                                                                   |

. ...

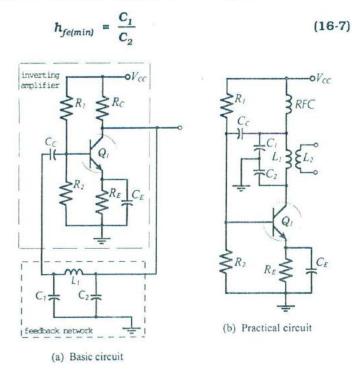

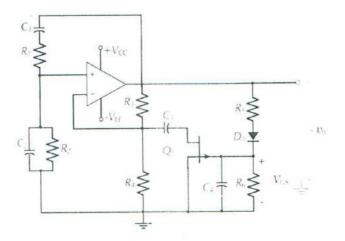

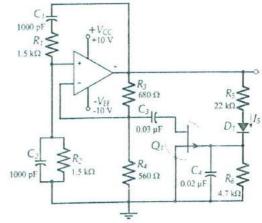

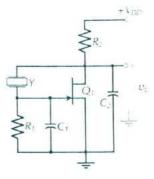

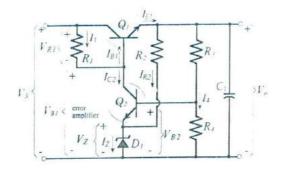

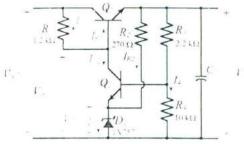

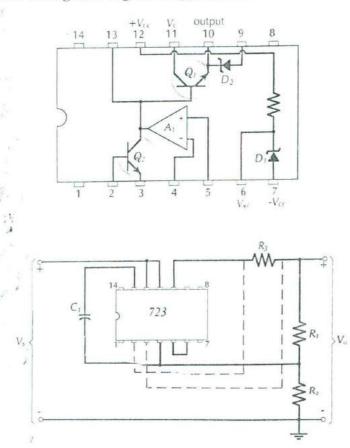

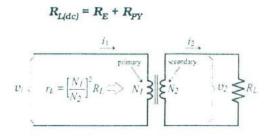

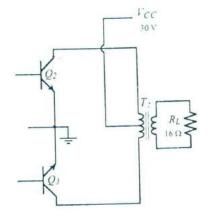

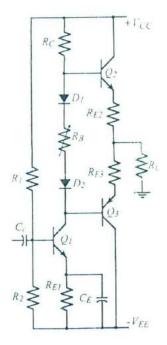

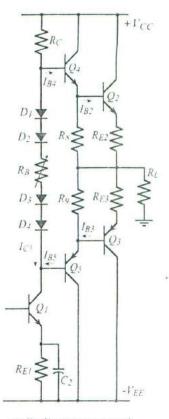

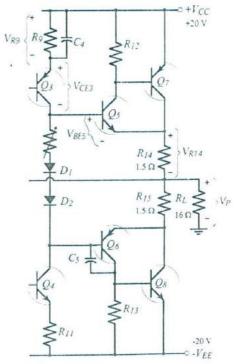

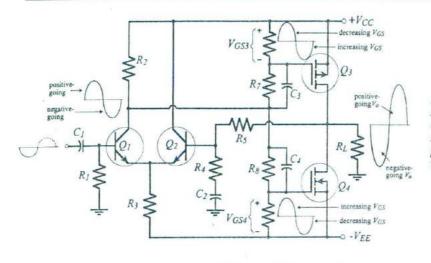

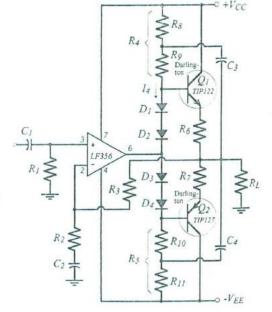

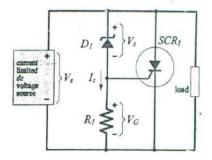

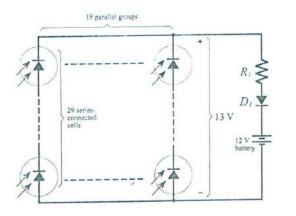

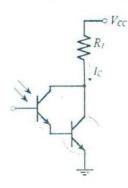

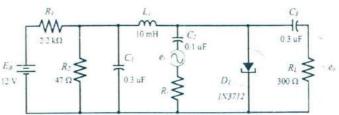

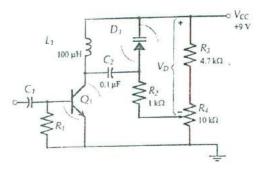

# BJT Colpitts Oscillator

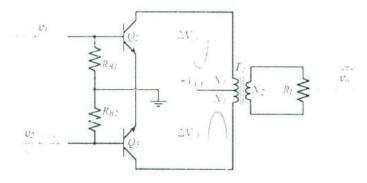

A Colpitts oscillator using a single *BJT* amplifier is shown in Fig. 16-6(a). This is the basic circuit, and its similarity to the op-amp Colpitts oscillator is fairly obvious. A more complex version of the circuit is shown in Fig. 16-6(b). Components  $Q_1, R_1, R_2, R_E$ , and  $C_E$  in (b) are unchanged from (a), but collector resistor  $R_C$  is replaced with inductor  $L_1$ . A radio frequency choke (*RFC*) is included in series with  $V_{CC}$  and  $L_1$ . This allows dc collector current ( $I_C$ ) to pass, but offers a very high impedance at the oscillating frequency, so that the top of  $L_1$  is ac isolated from  $V_{CC}$  and ground. The output of the *LC* network ( $L_1, C_1, C_2$ ) is coupled to via  $C_c$  to the amplifier input. The circuit output voltage ( $v_o$ ) is derived from a secondary winding ( $L_2$ ) coupled to  $L_1$ . As in the case of the *BJT* phase shift oscillator, the transistor current gain is important. Circuit analysis gives Eq. 16-4 for frequency, and for current gain.

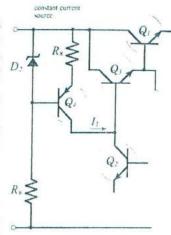

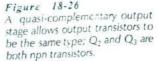

Figure 16-6

Colpitts oscillator using an inverting BJT amplifier and an LC feedback network.

# Practise Problems

- 16-2.1 Design a Colpitts oscillator circuit to produce a 12 kHz, ±10 V output. Use a 741 op-amp.

- 16-2.2 Design the oscillator in Fig. 16-6(a) to produce a 20 kHz, 6 V p-to-p output. Use a 10 mH inductor and assume that the *BJT* has  $h_{1b} \approx 26 \Omega$  and  $h_{ie} \approx 1.5 \text{ k}\Omega$ .

# 16-3 Hartley Oscillators

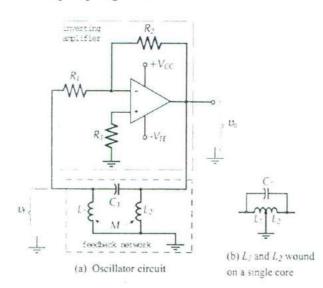

# **Op-Amp** Hartley Oscillator

The *Hartley oscillator* circuit is similar to the Colpitts oscillator, except that the feedback network consists of two inductors and a capacitor instead of two capacitors and an inductor. Figure 16-7(a) shows the Hartley oscillator circuit, and Fig. 16-7(b) illustrates the fact that  $L_1$  and  $L_2$  may be wound on a single core so that there is mutual inductance (*M*) between the two windings. In this case, the total inductance is.

$$L_T = L_1 + L_2 + 2 M \tag{16-8}$$

Oscillation occurs at the feedback network resonance frequency ;

$$f = \frac{1}{2 \pi \sqrt{(C_1 L_T)}}$$

(16-9)

The attenuation of the feedback network is.

$$B = \frac{X_{LI}}{X_{LI} - X_{CI}}$$

It can be shown that the required 180° phase shift occurs when

$$X_{L2} = X_{L1} - X_{C1}$$

The loop gain must be a minimum of one, giving;

$$A_{CL(min)} = \frac{L_2}{L_1}$$

(16-10)

Design procedure for a Hartley oscillator circuit is similar to that for a Colpitts oscillator.

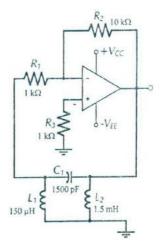

# Example 16-3

Design the Hartley oscillator in Fig. 16-8 to produce a 100 kHz output frequency with an amplitude of approximately  $\pm 8$  V. For simplicity, assume that there is no mutual inductance between  $L_1$  and  $L_2$ .

# Solution

select

$$V_{CC} \approx v_{o} + 1 V = \pm (8 V + 1 V)$$

$$\approx \pm 9 V$$

$X_{1,2} >> Z_0$  of the amplifier

$$X_{l2} \approx 1 \text{ k}\Omega$$

$$l_2 = \frac{X_{l2}}{2 \pi f} = \frac{1 \text{ k}\Omega}{2 \pi \times 100 \text{ kHz}}$$

= 1.59 mH (use 1.5 mH standard value)

select

$$\approx \frac{L_2}{10} = \frac{1.5 \text{ mH}}{10}$$

$L_1$

=  $150 \,\mu\text{H}$  (standard value)

$$L_7 = L_1 + L_2 = 1.5 \text{ mH} + 150 \,\mu\text{H} \text{ (assuming } M = 0)$$

= 1.65 mH

From Eq. 16-9,

$$C_{7} = \frac{1}{4 \pi^{2} f^{2} L_{7}} = \frac{1}{4 \pi^{2} x (100 \text{ kHz})^{2} x 1.65 \text{ mH}}$$

= 1535 pF (use 1500 pF with additional parallel capacitance, if necessary)

$$C_{7} >> \text{ stray capacitance}$$

$$X_{l1} = 2 \pi f L_1 = 2 \pi \times 100 \text{ kHz} \times 150 \,\mu\text{H}$$

= 94.2 \Over \Ove

Select

$$A_{CL(min)} = \frac{L_2}{L_1} = \frac{1.5 \text{ mH}}{150 \mu \text{H}}$$

= 10

$R_1 = 1 \ k\Omega$  (standard value)

$R_{1} >> X_{11}$

$$R_2 = A_{Ct} R_1 = 10 \times 1 \text{ k}\Omega$$

= 10 k\Omega (standard value)

$$R_3 = R_1 ||R_2 = 1 \text{ k}\Omega||10 \text{ k}\Omega$$

= 909 \Omega (use 1 k\Omega standard value)

*Figure 16-8* Hartley oscillator circuit for Example 16-3.

The op-amp full-power bandwidth ( $f_p$ ) must be a minimum of 100 kHz when  $v_0 \approx \pm 8$  V and  $A_{Cl} = 10$ .

from Eq. 15-2,  $f_2 = A_{CL} \times f = 10 \times 100 \text{ kHz}$  = 1 MHzfrom Eq. 15-3,  $SR = 2 \pi f_p v_p = 2 \pi \times 100 \text{ kHz} \times 8 \text{ V}$  $= 5 \text{ V/}\mu\text{s}$

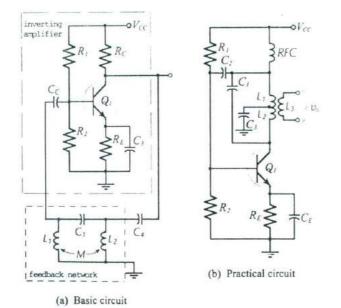

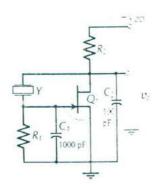

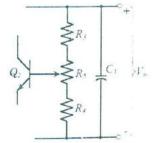

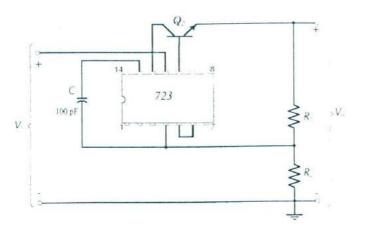

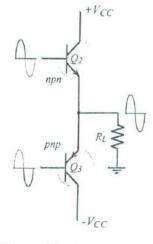

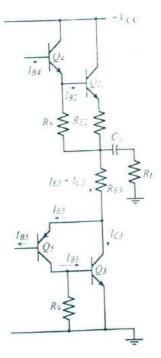

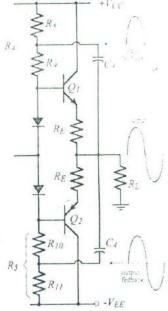

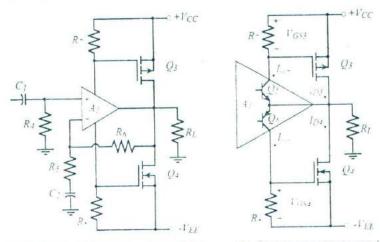

### **BJT Hartley Oscillator**

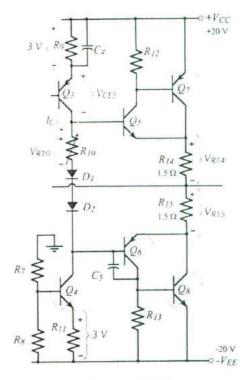

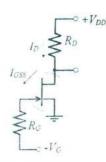

Figure 16-9 shows the circuit of a Hartley oscillator using a *BJT* amplifier. The basic circuit in Fig. 16-9(a) is similar to the op-amp Hartley oscillator, and its operation is explained in the same way as for the op-amp circuit. Note that coupling capacitors  $C_2$  and  $C_4$  are required to avoid *dc* grounding the transistor base and collector terminals through  $L_1$  and  $L_2$ .

In the practical *BJT* Hartley oscillator circuit shown in Fig. 16-9(b)  $L_1$ ,  $L_2$ , and  $C_1$  constitute the phase shift network. In this case, the inductors are directly connected in place of the transistor collector resistor ( $R_c$ ). The circuit output is derived from the additional inductor winding ( $L_3$ ). The radio frequency choke (*RFC*) passes the direct collector current, but *ac* isolates the upper terminal of  $L_1$  from the power supply. Capacitor  $C_2$  couples the output of the feedback network back to the amplifier input. Capacitor  $C_4$  at the *BJT* collector in Fig. 16-9(a) is not required in Fig. 16-9(b), because  $L_2$  is directly connected to the collector terminal. The junction of  $L_1$  and  $L_2$  must now be capacitor coupled to ground (via  $C_3$ ) instead of being direct coupled.

Figure 16-9 Hartley oscillator consisting of a BJT inverting amplifier and an LC feedback network.

# Practise Problems 16-3.1 A Hartley oscillator circuit using a 741 op-amp is to produce a 7 kHz, ±10 V output. Determine suitable component values. 16-3.2 Analyze the BJT Hartley oscillator in Fig. 16-9(b) to determine the oscillating frequency. Some of the component values are: L<sub>1</sub> = L<sub>2</sub> = 4.7 mH; C<sub>1</sub> = 600 pF, C<sub>2</sub> = C<sub>3</sub> = 0.03 µF. The mutual inductance

between  $L_1$  and  $L_2$  is 100  $\mu$ H.

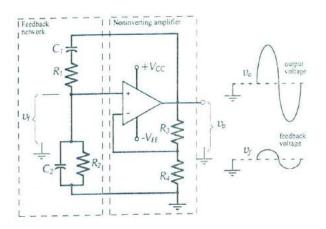

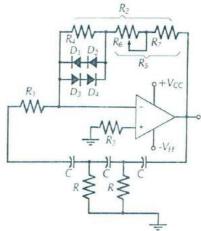

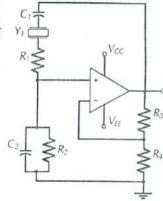

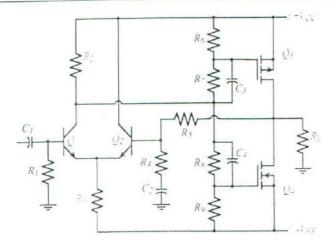

# 16-4 Wein bridge Oscillator

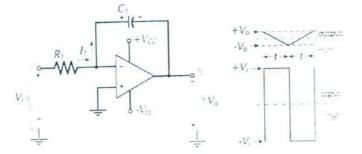

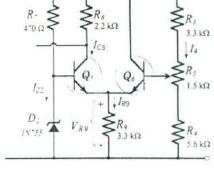

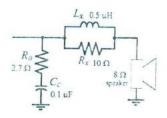

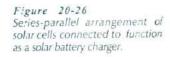

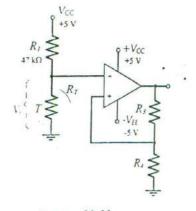

The Wein bridge is an *ac* bridge that balances only at a particular supply frequency. In the Wein bridge oscillator (Fig. 16-10), a Wein bridge circuit is used as a feedback network between the amplifier output and input. The bridge is made up of all of the resistors and capacitors. The operational amplifier together with resistors  $R_3$  and  $R_4$  constitute a noninverting amplifier. The feedback network from the amplifier output to its noninverting input terminal is made up of components  $C_1$ ,  $R_1$ ,  $C_2$  and  $R_2$ .

At the balance frequency of the Wein bridge, the feedback voltage is in phase with the amplifier output. This (in-phase) voltage is amplified to reproduce the output. At all other frequencies, the bridge is off balance: that is, the feedback and output voltages do not have the correct phase relationship to sustain oscillations. The Barkhausen requirement for zero loop phase shift is fulfilled in this circuit by the amplifier and feedback network both having zero phase shift at the oscillation frequency.

Analysis of the bridge circuit shows that balance is obtained when two equations are fulfilled:

$$\frac{R_3}{R_4} = \frac{R_1}{R_2} + \frac{C_2}{C_1}$$

(16-11)

5 4 2 Electronic Devices and Circuits, 4th ed.

and,

$$2\pi f = \frac{1}{\sqrt{(R_1 C_1 R_2 C_2)}}$$

(16-12)

If  $R_1 C_1 = R_2 C_2$ . Eq. 16-12 yields,

$$f = \frac{1}{2\pi R_1 C_1}$$

(16-13)

For simplicity, the components are often selected as,  $R_1 = R_2$  and  $C_1 = C_2$ , causing Eq. 16-11 to give,

$$R_3 = 2 R_4 \tag{16-14}$$

In this case, the amplifier closed-loop gain is,  $A_{CL} = 3$ .

Sometimes it is preferable to have an amplifier voltage gain substantially greater than 3, then the relationship between the component values is determined by Equations 16-11 and 16-12.

Design of a Wein bridge oscillator can be commenced by selecting a current level for each arm of the bridge. This should be much larger than the op-amp input bias current. Resistors  $R_3$  and  $R_4$  can then be calculated using the estimated output voltage and the closed-loop gain. After that, the other component values can be determined from the above equations.

An alternative design approach is to start by selecting a convenient value for the smallest capacitor in the circuit. The other component values are then calculated from the equations.

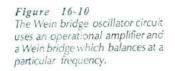

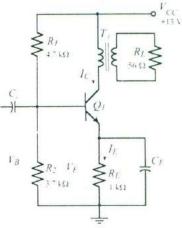

#### Example 16-4

Design the Wein bridge oscillator in Fig. 16-11 to produce a 100 kHz,  $\pm 9$  V output. Design the amplifier to have a closed-loop gain of 3.

#### Solution

|                      | $V_{CC} \approx \pm (V_o + 1 \text{ V}) = \pm (9 \text{ V} + 1 \text{ V})$ $= \pm 10 \text{ V}$                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| for $A_{\Box} = 3$ , | $R_1 = R_2 \text{ and } C_1 = C_2$                                                                                                                                           |

| also,                | $R_3 = 2 R_4$                                                                                                                                                                |

| select,              | $C_{\gamma} = 1000 \text{ pF}$ (standard value)                                                                                                                              |

|                      | $C_2 = C_1 = 1000 \text{ pF}$                                                                                                                                                |

| From Eq. 16-13,      | $R_{1} = \frac{1}{2 \pi f C_{1}} = \frac{1}{2 \pi x  100 \text{ kHz x } 1000 \text{ pF}}$ $= 1.59 \text{ k}\Omega \text{ (use } 1.5 \text{ k}\Omega \text{ standard value)}$ |

|                      | $R_2 = R_1 = 1.5 \text{ k}\Omega$                                                                                                                                            |

| select,              | $R_4 \approx R_2 = 1.5 \text{ k}\Omega$ (standard value)                                                                                                                     |

Figure 16-11 Wein bridge oscillator circuit for Example 16-4.

$R_{2} = 2 R_{4} = 2 \times 1.5 \text{ k}\Omega$ = 3 kQ (use 3.3 kQ standard value)

The op-amp must have a minimum full-power bandwidth (fp) of 100 kHz when  $v_c \approx \pm 9$  V and  $A_c = 3$ .

from Eq. 15-2,  $i_2 = A_{cl} \times f = 3 \times 100 \text{ kHz}$ = 300 kHz

from Eq. 15-3,

$$SR = 2 \pi f_p v_p = 2 \pi x 100 \text{ kHz } x 9 \text{ V}$$

$$\approx 5.7 \text{ V/}\mu\text{s}$$

#### Practise Problems

16-4.1 Resistors  $R_1$  and  $R_2$  in Fig. 16-11 are switched to (a) 15 k $\Omega$  and (b) 5.6 k $\Omega$ . Calculate the new oscillating frequency in each case.

16-4.2 A Wein bridge oscillator using an op-amp is to produce a 15 kHz,  $\pm 14$  V output. Design the circuit with the amplifier having  $A_{cr} = 11$ .

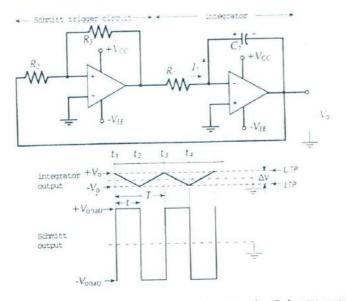

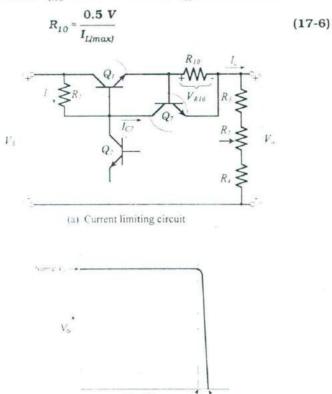

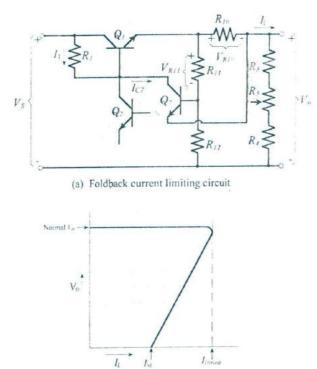

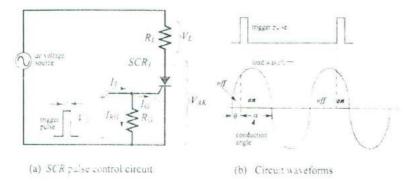

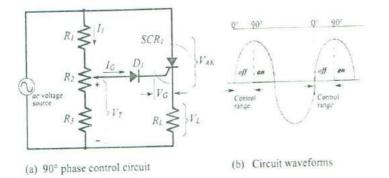

#### Oscillator Amplitude Stabilization 16-5

#### Output Amplitude

For all of the oscillator circuits discussed, the output voltage amplitude is determined by the amplifier maximum output swing. The output waveform may also be distorted by the amplifier output saturation limitations. To minimize distortion and reduce the output voltage to an acceptable level, amplitude stabilization circuitry must be employed. Amplitude stabilization operates by ensuring that oscillation is not sustained if the output exceeds a predetermined level.

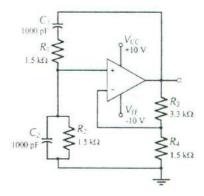

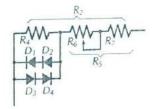

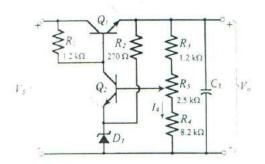

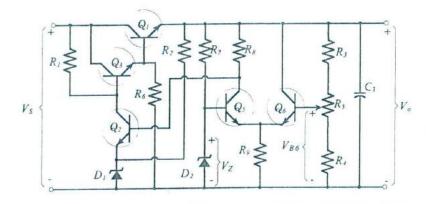

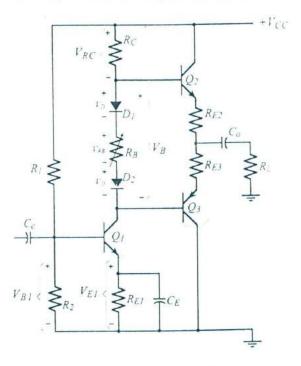

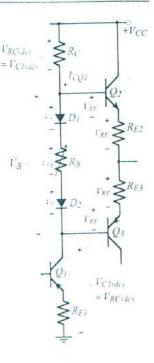

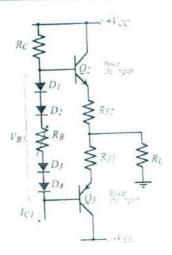

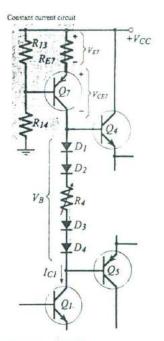

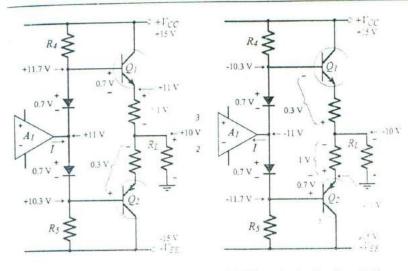

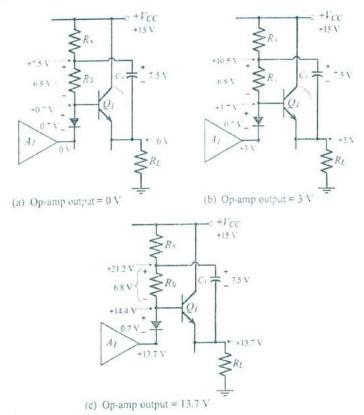

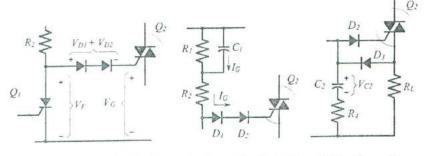

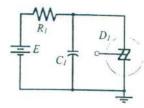

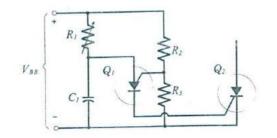

# Diode Stabilization Circuit for a Phase Shift Oscillator

The phase shift oscillator discussed in Section 16-1 must have a minimum amplifier gain of 29 for the circuit to oscillate. Consider the oscillator circuit in Fig. 16-12(a) that has part of resistor  $R_2$ bypassed by series-parallel connected diodes. When the output amplitude is low, the diodes do not become forward biased, and so they have no effect on the circuit. At this time, the amplifier voltage gain is,  $A_{CL} = R_2/R_1$ . As always for a phase shift oscillator,  $A_{CL}$  is designed to exceed the critical value of 29. When the output amplitude becomes large enough to forward bias either  $D_1$  and  $D_2$ . or  $D_3$  and  $D_4$ , resistor  $R_4$  is short-circuited, and the amplifier gain becomes,  $A_{CL} = R_5/R_1$ . This is designed to be too small to sustain oscillations. So, this circuit cannot oscillate with a highamplitude output, however it can (and does) oscillate with a lowamplitude output.

(a) Phase shift oscillator with amplitude stabilization

(b) Use of adjustable resistor for distortion control

#### Figure 16-12

The output amplitude of a phase shift oscillator can be limited by using diodes to modify the amplifier gain.

In designing the amplitude stabilization circuit, the inverting amplifier is designed in the usual manner with one important difference. The current  $(I_l)$  used in calculating the resistor values must be selected large enough to forward bias the diodes into the near-linear region of their characteristics. This usually requires a minimum current around 1 mA. Resistor  $R_l$  is calculated using,

$$R_{I} = \frac{v_{o}/29}{I_{I}}$$

(16-15)

and  $R_2$  is determined as.

$$R_2 = 29 R_1$$

(16-16)

The diodes should become forward biased just when the output voltage is at the desired maximum level. At this time,  $l_i$  produces a voltage drop of 2  $V_F$  across  $R_q$ .

$$R_4 \approx \frac{2 V_F}{I_I} \tag{16-17}$$

and,

The resultant component values should give  $(R_{\ddagger} + R_{5})/R_{1}$  slightly greater than 29, and  $R_{5}/R_{1}$  less than 29.

$R_5 = R_2 - R_4$

Some distortion of the waveform can occur if  $(R_4 + R_5)/R_1$  is much larger than 29, however, attempts to make the gain close to 29 can cause the circuit to stop oscillating. Making a portion of  $R_5$ adjustable, as illustrated in Fig. 16-12(b), provides for gain adjustment to give the best possible output waveform. Typically,  $R_6$ should be approximately 40% of the calculated value of  $R_5$ , and  $R_7$ should be 80% of  $R_5$ . This gives a ±20% adjustment of  $R_5$ .

The diodes selected should be low-current switching devices. The diode reverse breakdown voltage should exceed the circuit supply voltage, and the maximum reverse recovery time  $(t_{rrimax})$  should be around one-tenth of the time period of the oscillation frequency.

$$t_{rr(max)} = \frac{T}{10}$$

(16-18)

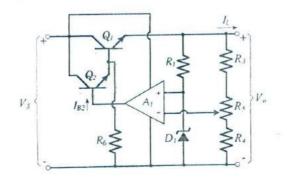

#### Example 16-5

Design the phase shift oscillator in Fig. 16-13 to produce a 5 kHz,  $\pm 5$  V output waveform.

#### Solution

Select

$I_1 \approx 1 \text{ mA when } v_{o(\text{oeak})} = 5 \text{ V}$

$$R_{1} = \frac{\upsilon_{o}/29}{I_{1}} = \frac{5 \text{ V}/29}{1 \text{ mA}}$$

$$= 170 \text{ }\Omega \text{ (use } 150 \text{ }\Omega\text{)}$$

Figure 16-13 Amplitude-controlled phase shift oscillator circuit for Ex. 16-5.

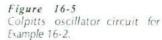

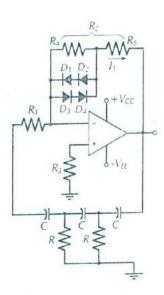

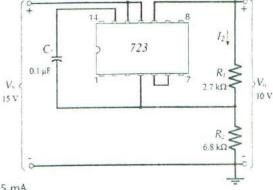

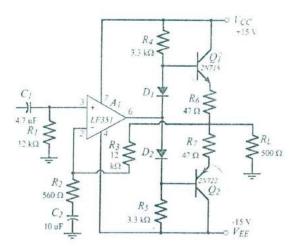

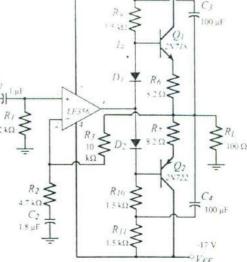

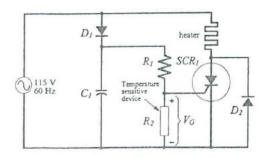

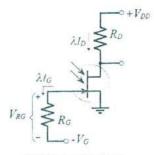

*Diode Stabilization Circuit for a Wein Bridge Oscillator* Figures 16-14, and 16-15 show two output amplitude stabilization methods that can be used with a Wein bridge oscillator. These can also be applied to other oscillator circuits, because they all operate by limiting the amplifier voltage gain.

The circuit in Fig. 16-14 uses diodes and operates in the same way as the amplitude control for the phase-shift oscillator. Resistor  $R_6$  becomes shorted by the diodes when the output amplitude exceeds the design level, thus rendering the amplifier gain too low to sustain oscillations.

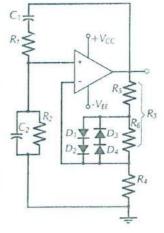

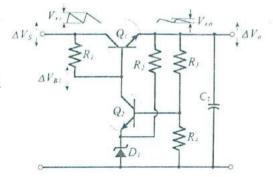

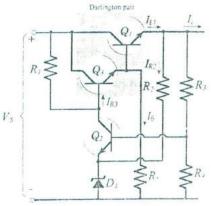

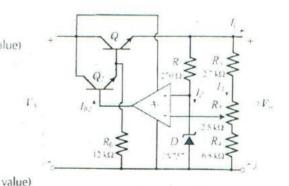

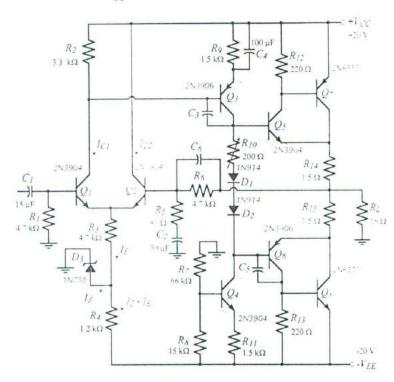

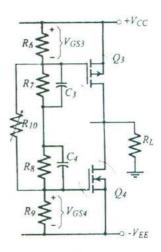

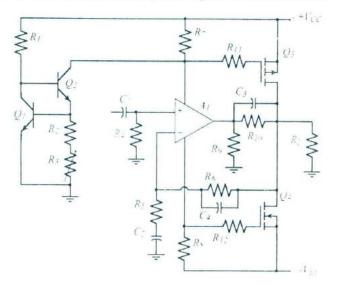

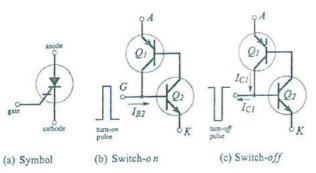

**FET** Stabilization Circuit for a Wein Bridge Oscillator The circuit in Fig. 16-15 is slightly more complex than the diode circuit, however, like other circuits, it stabilizes the oscillator output amplitude by controlling the amplifier gain. The channel resistance  $(r_{DS})$  of the *p*-channel FET  $(Q_1)$  is in parallel with resistor  $R_4$ . Capacitor  $C_3$  ensures that  $Q_1$  has no effect on the amplifier dc conditions. The amplifier voltage gain is,

$$A_{CL} = \frac{R_3 + R_4 || r_{DS}}{R_4 || r_{DS}}$$

(16-19)

The FET gate-source bias voltage is derived from the amplifier ac output. The output voltage is divided across resistors  $R_5$  and  $R_6$ .

#### Figure 16-14 Wein bridge oscillator with its output amplitude stabilized by a diode circuit that modifies the amplifier gain.

and rectified by diode  $D_1$ . Capacitor  $C_4$  smoothes the rectified waveform to give the *FET dc* bias voltage ( $V_{GS}$ ). The polarity shown on the circuit diagram reverse biases the gate-source of the *p*channel device. When the output amplitude is low,  $V_{GS}$  is low and this keeps the *FET* drain-source resistance ( $r_{DS}$ ) low. When the output gets larger,  $V_{GS}$  is increased causing  $r_{DS}$  to increase. The increase in  $r_{DS}$  reduces  $A_{CL}$ , thus preventing the circuit from oscillating with a high output voltage level. It is seen that the *FET* is behaving as a voltage variable resistance (*VVR*).

Figure 16-15

Wein bridge oscillator with the output amplitude stabilized by a FET voltage controlled resistance circuit.

#### Design of a FET Stabilization Circuit

To design the *FET* amplitude stabilization circuit, knowledge of a possibly suitable *FET* is required; in particular, the channel resistance at various gate-source voltages must be known.

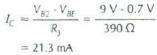

Suppose the circuit is to oscillate when  $r_{DS} = 6 \text{ k}\Omega$  at  $V_{CS} = 1 \text{ V}$ , and that the peak output is to be  $V_{o(pk)} = 6 \text{ V}$ . Resistors  $R_5$  and  $R_6$ should be selected to give  $V_{CS} = 1 \text{ V}$  when  $V_{o(pk)} = 6 \text{ V}$ , allowing for  $V_F$  across the diode. Capacitor  $C_4$  smoothes the half-wave rectified waveform, and discharges via  $R_6$  during the time interval between peaks of the output waveform. The capacitance of  $C_4$  is calculated to allow perhaps a 10% discharge during the time period of the oscillating frequency. The voltage divider current ( $I_5$ ) should be a minimum of around 100 µA for satisfactory diode operation.

$C_3$  is a coupling capacitor; its impedance at the oscillating frequency should be much smaller than the  $r_{DS}$  of the *FET*. Resistors  $R_3$  and  $R_4$  are calculated using Eq. 16-19 to give the required amplifier voltage gain when  $r_{DS} = 6 \text{ k}\Omega$ .

#### Example 16-6