The digital world is a world of ones and zeros. It utilizes circuits that are on or off, logic conditions that are true or false, and voltages that are high or low. By recognizing only two possible conditions, errors due to component tolerance and temperature drift are all but completely eliminated. The real world is an analog world. The speed of a motor, the temperature of a process, and the intensity of a laser beam are all examples of analog measures. There are an infinite number of actual values in the analog world. It is possible to use digital circuits to measure, control, and generally interact with the analog world. The current trend is to use more digital and less analog circuitry in industrial electronics. The industrial technician must understand both types of circuits and how they are interfaced.

# 11-1

# CHARACTERISTICS OF DIGITAL CIRCUITS

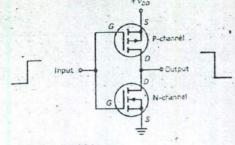

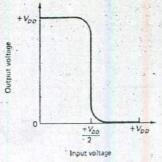

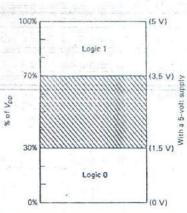

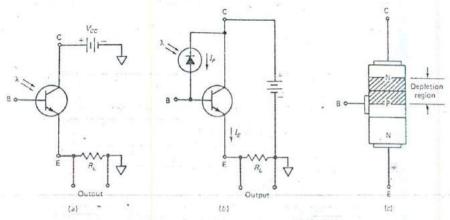

Early digital circuits used vacuum tubes. Then, in the 1960s, integrated digital circuits were developed. The first integrated digital circuits were based on resistors, diodes, and transistors. They were resistortransistor logic (RTL) circuits. Diode-transistor logic (DTL) was the next step. By the 1980s, RTL and DTL devices were obsolete for modern designs. They have been replaced by the transistor-transistor logic (TTL) and the complementary metallic oxide semiconductor (CMOS) families. This section will cover the important electrical parameters of TTL family devices; a later section will cover the CMOS family.

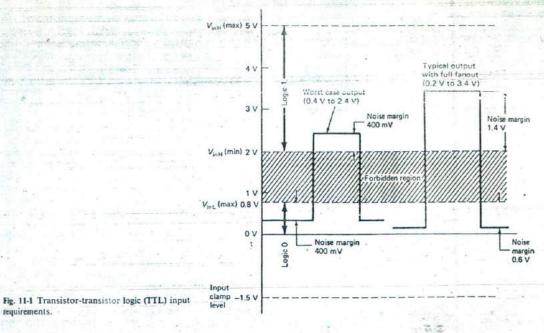

Figure 11-1 shows the input signal requirements for a TTL circuit. Any signal voltage from 2 to 5 V is interpreted as a logic 1. These levels are called  $V_{\text{INH}(\text{MIN})}$  and  $V_{\text{INH}(\text{MAN})}$ , respectively. Any voltage

from 0 to 0.8 V is interpreted as a logic 0. Notice that the region from 0.8 to 2 V is forbidden. Any signal in that region would produce unpredictable output results. Obviously, a signal that is changing from 0 to 1 or from 1 to 0 must go through the forbidden region. This is acceptable. A signal that remains in the forbidden region for any length of time is not acceptable. An input that is floating (not connected to anything) will measure between 1.1 and 1.5 V, which is in the forbidden region. The device will interpret this as a high input (logic 1), but a floating input invites noise pickup. Therefore, an input that is to be fixed at logic 1 should be tied to the positive supply. The TTL systems run on a 5-V power supply. Most signals will be between 0 and 5 V. Signals more positive than 5 V should not be applied to a TTL input because damage may result. A signal that is negative with respect to ground can also damage a TTL device. Most devices have input clamp diodes to protect against negative signals, but a signal more negative than 1.5 V may damage the input.

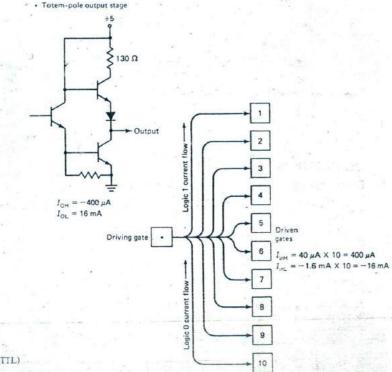

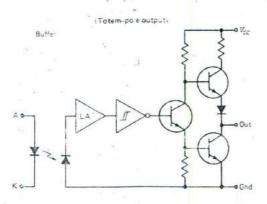

Most often TTL inputs are driven by TTL outputs. When the expected output levels are compared to the required input levels, the margin for error can be evaluated. The rectangular waveforms shown in Fig. 11-1 are for the worst-case and typical levels that can be expected at the output of a device. Worst case means that the manufacturer guarantees the logic 1 level from the device supplying the signal to be at least 2.4 V and the logic 0 level to be no more than 0.4 V when the device is fully loaded. The difference between the worst-case driving signal levels and the input thresholds at the driven device is seen to be 400 mV. This is called the noise margin. In practice, the actual noise margin is better. The typical TTL signal source will swing from 0.2 V (logic 0) to 3.4 V (logic 1) when fully loaded. A full load is also called a full fanout and is shown in Fig. 11-2. The signal source, called the driving gate, must supply logic 0 or a logic 1 to 10 driven gates. By the nature of the totem pole output stage (discussed in Chapter 2) in the driving gate, the logic 0 sink current capability is greater than the logic 1 source current capability. The totem pole pair uses a load resistor of

CHAPTER 11, DIGITAL CIRCUITS AND DEVICES 267

Fig. 11-2 Transistor-transistor logic (TTL) fanout.

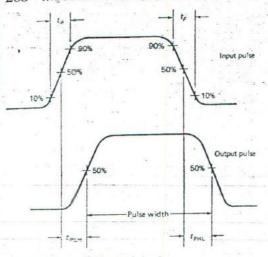

Fig. 11-3. Digital pulse characteristics.

approximately 130  $\Omega$  between the supply and the top transistor. This resistor limits the current that the output can source when it is at logic 1. The sink current,  $I_{OL}$ , is rated at 16 mA, and the source current  $I_{OH}$  is rated at only  $-400 \ \mu$ A. The negative sign indicates that the current is flowing away from the driving gate when it is sourcing current. The inpur requirements for each driven gate are  $I_{INH} = 40 \ \mu$ A and  $I_{INL} = -1.6 \ m$ A. This means that a TTL output can drive no more than 10 TTL inputs, or the guaranteed noise margin will be lost. If the maximum fanout is exceeded, the output voltage may fall in the forbidden region. This can happen when the driving gate is sourcing or sinking current.

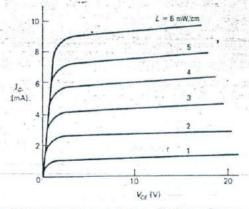

Figure 11-3 shows the characteristics of digital pulses. Rise time  $(I_R)$  is the time required for the pulse to change from its 10 to its 90 percent level. Fall time  $(I_F)$  is the time required for the pulse to change from the 90 to the 10 percent level. When the pulse is applied to the input of a TTL device, it takes time before the output changes. The propagation delay from low to high  $(I_{PLH})$  is measured from the 50

percent point on the input waveform to the 50 percent point on the output waveform. The propagation delay from high to low  $(t_{PHL})$  is also measured from 50 percent point to 50 percent point. Digital circuits with short propagation delays are faster and are capable of high-frequency operation. The pulse width is measured from the 50 percent point on the rising edge of a pulse to the 50 percent point on the falling edge of the same pulse.

Table 11-1 lists a few important characteristics for the TTL logic family. This family has four subfamily members. It is important to note that the part numbers clearly identify the subfamily members. For example, a 7400 gate is a TTL device, and a 74LS00 is a low-power Schottky (LS) clamped device, which is a TTL subfamily. The part numbers 7490 and 74LS90 represent another example: the 7490 is a TTL device, and the 74LS90 is an LS TTL subfamily device. You may also encounter 5400 series numbers, which are military versions of the 7400 TTL family. The military devices are rated from - 55°C to + 125°C; commercial and industrial devices are rated from 0°C to + 70°C. Different manufacturers may deviate from the 7400 numbering system, and 8000 numbers are also popular. The TTL and LS TTL devices are the most widely applied. Table 11-1 shows that the LS devices are faster (less propagation delay) than the TTL devices and use less current. The LS devices used to cost more but now are about as expensive as TTL parts, and designers choose them most often : Since they are more power-efficient and faster devices, there is usually no reason to specify TTL devices in new designs unless the LS version of the required device is not available.

All TTL devices and TTL subfamily devices are rated at a fanout of 10, except when subfamilies are mixed or when subfamily devices are mixed with TTL devices. A low-power Schottky device will drive 10 gates in its own subfamily but will drive only 5 TTL gates. There are also speed differences. Some LS devices can approach twice the speed of their TTL counterparts. If a circuit is operating near its top speed, a substitution may not work or, worse yet, may work intermittently. The current drain is also different. Multiple substitutions of standard TTL for LS TTL could overload a power supply or add to the heat build-up in a circuit. Substitutions may

| TABLE 11 | -I THE TI                    | L LOGIC | FAMILY |

|----------|------------------------------|---------|--------|

|          | and the second second second |         |        |

|     | Family Name                  | Part Number | f <sub>PLH</sub><br>nS | t <sub>PHL</sub><br>ns | I <sub>max</sub><br>mA | Comments                                          |

|-----|------------------------------|-------------|------------------------|------------------------|------------------------|---------------------------------------------------|

| TTL | transistor-transistor logic) | 7400        | 11                     | 7                      | 22                     | Being replaced by LS subfamily devices            |

|     | speed TTL                    | 74H00       | 5.9                    | 6.2                    | 40                     | High power consumption; not popular               |

|     | power TTL                    | 74L00       | 35                     | 31                     | 2.04                   | Being replaced by CMOS family devices             |

|     | oower Schottky clamped       | 74L.S00     | 5.                     | 5                      | 4.4                    | Very popular; used heavily in modern de-<br>signs |

|     | tky clamped TTL              | 74500       | 3                      | 3                      | 36                     | Very fast; used in high-speed circuits            |

| <b>TABLE 11-2</b> | COUNTING | WITH | SEVERAL NUMBER |  |

|-------------------|----------|------|----------------|--|

| SYSTEMS           |          |      |                |  |

| 0101 Lino                          |       |                         |                  |

|------------------------------------|-------|-------------------------|------------------|

| Decimal, Binary,<br>Base 10 Base 2 |       | Hexadecimal,<br>Base 16 | Octal,<br>Base 8 |

| 0                                  | 0     | - 0                     | - 0              |

| 1                                  | 1     | 1                       | i                |

| 2                                  | 10*   | 2                       | 2                |

| 3                                  | 11    | 3                       | 3                |

| 4                                  | 100   | 4                       | 4                |

| 5                                  | 101   | 5                       | 5                |

| 6                                  | 110   | 6                       | 6                |

| 7                                  | 111   | 7                       | 7                |

| 8                                  | 1000  | 8                       | 10*              |

| 9                                  | 1001  | 9                       | 11               |

| 10                                 | 1010  | A                       | 12               |

| 11                                 | 1011  | В                       | 13               |

| 12                                 | 1100  | C                       | 14 .             |

| 13                                 | 1101  | D                       | 15               |

| 14                                 | 1110  | E                       | 16               |

| 15                                 | 1111  | F                       | 17               |

| 16                                 | 10000 | 10*                     | 20†              |

| 17                                 | 10001 | 11                      | 21               |

| 18                                 | 10010 | 12                      | 22               |

\* Read as "one-zero," not "ten."

\* Read as "two-zero," not "twenty."

be acceptable, but be sure to investigate fanout, speed, current demand, and heat. The best replacement usually has exactly the same part number.

Since digital circuits recognize only two conditions, the binary number system is used for operations involving counting, arithmetic, and for representation of analog quantities. Table 11-2 compares several number systems. The decimal number system has 10 symbols, 0 through 9. The quantity of symbols in a number system is referred to as its base or radix. Therefore, the radix of our familiar decimal system is 10. When a quantity larger than 9 must be represented, more than one symbol is used at a time. The same technique applies to binary, which uses only two symbols, 0 and 1. Follow the count in Table 11-2. You should determine that it is possible to represent any quantity in binary that can be represented in decimal, provided there is provision for enough 0s and 1s. Table 11-2 also shows the hexadecimal number system, which has a radix of 16. It adds the characters A through F to the familiar decimal is a convenient shortcut when working with binary systems as we shall see. The *octal* system is also shown in the table. It has a base of 8 and is also used as a shortcut for working with binary, although hexadecimal is more popular.

Binary, hexadecimal, and octal are all weighted codes, making converting them to decimal straightforward. Table 11-3 shows how weighted codes work. Starting to the immediate left of the radix point (we call it the decimal point when working with decimal numbers) it is seen that the weight is the base raised to the 0 power. Any number raised to the zero power has a value of 1. Therefore, the weight of this position is always 1. Moving to the left, the next position is weighted equal to the base of the number system raised to the first power. Any number raised to the first power is equal to itself. Therefore, the weight of this position is equal to 2 in binary, 16 in hexadecimal, and 8 in octal. Moving to the left again we find the weight equal to the base raised to the second power. Therefore, the weight of this position is equal to 4 in binary, 256 in hexadecimal, and 64 in octal. The fractional parts of a number are represented by positions to the right of the radix point.

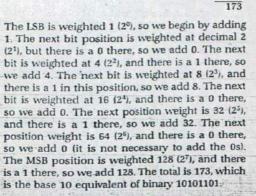

To convert a binary number to decimal, it is necessary to add up the decimal weights for each binary digit. The word bit is a contraction for binary digit and will be used from now on. Suppose we wish to convert binary 10101101 to decimal. The process begins at the far right, which is called the *least significant bit* (LSB), and progresses to the leftmost bit, which is called the *most significant bit* (MSB).

#### **EXAMPLE 1**

Convert binary 10101101 to decimal.

|                                                                                      |                                                                                                          |                                                                         | Whole                                        | Part                                    |                                     |                                                                       |                                                                     |                                | Fract<br>Pa                                                            |                                                                        |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|-------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|

| Binary<br>Decimal weight<br>Hexadecimal<br>Decimal weight<br>Octal<br>Decimal weight | $2^{7}$<br>128<br>16 <sup>7</sup><br>2.68 × 10 <sup>8</sup><br>.8 <sup>7</sup><br>2.10 × 10 <sup>6</sup> | $2^{5}$<br>64<br>$16^{6}$<br>$1.63 \times 10^{7}$<br>$8^{6}$<br>262,144 | 25<br>32<br>165<br>1,048,576<br>85<br>32,763 | 24<br>16<br>164<br>65,536<br>84<br>4096 | 23<br>8<br>163<br>4095<br>83<br>512 | 2 <sup>2</sup><br>4<br>16 <sup>2</sup><br>256<br>8 <sup>2</sup><br>64 | 2 <sup>1</sup><br>2<br>16 <sup>1</sup><br>16<br>8 <sup>1</sup><br>8 | 2°<br>1<br>16°<br>1<br>8°<br>1 | $2^{-1}$ $\frac{1}{2}$ $16^{-1}$ $\frac{1}{26}$ $8^{-1}$ $\frac{1}{8}$ | 2-2<br>1<br>16-3<br>16-3<br>16-3<br>16-3<br>16-3<br>16-3<br>16-3<br>16 |

TARIE 11-3 WEIGHTED CODES

Radix Point

# SOLUTION

it is not necessary to add 0's

Because there may be a possibility of confusion, the base of a number may be specified with a subscript. For example,  $10101101_2 = 173_{10}$

The same general technique is used to convert hexadecimal numbers to decimal.

#### EXAMPLE 2

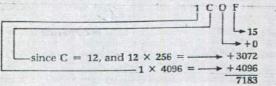

Convert hexadecimal 1COF to decimal.

#### SOLUTION

The weight of the least significant position is 1 (16<sup>9</sup>), and there is an F there. In decimal F is equal to 15 so we add 15. The next weight is 16 (16<sup>1</sup>), but there is a 0 there, so we can add 0 or not. The weight of the next position is 256 (16<sup>2</sup>), and there is a C there. Since C is equal to decimal 12 we add 12 × 256, or 3072. The last position is weighted 4096 (16<sup>3</sup>), and there is a 1 there, so we add 4096. The total is 7183. Therefore,  $1COF_{18} = 7183_{19}$ .

Converting from octal to decimal uses the same process and is demonstrated in Example 3:

# EXAMPLE 3

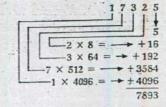

Convert octal 17325 to decimal.

#### SOLUTION

0

1

0

+ 32

+128

0

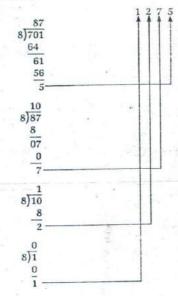

We must also be able to convert from decimal to other number systems. This process involves dividing the decimal number by the base of the given number system while keeping a record of all remainders. The division continues until the decimal number is exhausted. The list of remainders is the number in the given number system.

#### EXAMPLE 4

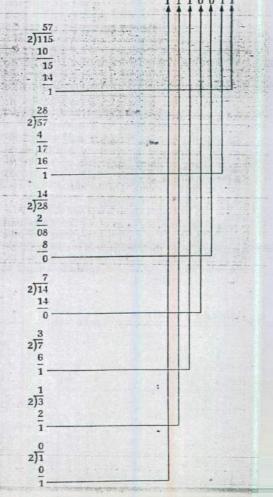

Convert decimal 115 to binary.

# CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 271

When 2 is divided into 115, the quotient is 57 with a remainder of 1. This first remainder becomes the LSB of the answer. Next 57 is divided by 2 with a quotient of 28 and a remainder of 1. This remainder becomes the next bit of the answer. Then 28 is divided by 2 with a quotient of 14 and a remainder of 0. This 0 remainder becomes the next bit of the answer. The process continues until the quotient is 0, and the last remainder has been recorded as the MSB of the answer. Therefore,  $115_{10} = 1110011_2$ .

Converting from decimal to hexadecimal involves repeated division by 16 until the number is exhausted. All remainders are converted to hexadecimal characters and recorded. The process ends when the quotient is 0 and the last remainder has been placed in the leftmost position.

#### **EXAMPLE 5**

Convert decimal 7307 to hexadecimal.

#### SOLUTION

Note that the first remainder is decimal 11, which is equal to B in hexadecimal.

Hexadecimal (and occasionally octal) is used to enter information into and extract information from digital systems quickly. The trouble with binary is that too many bits are required to represent numbers of moderate size. It takes too long to enter or read a lot of 0s and 1s, and the process is error-prone. A digital system does not understand hexadecimal any better than it understands' decimal. Digital systems are strictly binary in nature. However, there is a natural relationship between binary and hexadecimal that makes conversion very easy. Decimal 16 is a power of 2, and each hex character can be represented by 4 bits.

# EXAMPLE 6

Convert decimal 701 to octal.

#### SOLUTION

# EXAMPLE 7

Convert hexadecimal A4E to binary.

SOLUTION

Each digit of  $A4E_{16}$  is converted to a binary number as shown.

It is just as easy to convert from binary to hex.

## EXAMPLE 8

Convert binary 10010100111 to hexadecimal.

#### SOLUTION

Group the bits into 4s, starting with the rightmost bits. Do not be concerned if the leftmost group does not have 4 bits. Convert whatever is in the leftmost group to the appropriate hex character.

Octal is also convenient since 8 is also a power of 2. To convert octal to binary, each octal character must be represented by a group of 3 bits.

# EXAMPLE 9

Convert octal 725 to binary.

| 1.1.2.5   | Decimal | Binary | BCD        |

|-----------|---------|--------|------------|

|           | 0       | . 0    | 0000       |

| 書記        | 1       | 1      | 0001       |

| Section . | 2       | 10     | 0010       |

|           | 3       | - 11   | 0011       |

|           | 4       | 100    | 0100       |

|           | 5       | 101    | 0101       |

|           | 6       | 110    | 0110       |

|           | 7       | 111    | 0111       |

|           | 8       | 1000   | 1000       |

|           | 9       | 1001   | 1001       |

|           | 10      | 1010   | 0000 10000 |

|           | 11      | 1011   | 0001 0001  |

|           | 12      | 1100   | 0001 0010  |

| -         | 13      | 1101   | 0001 0011  |

| X 89 -    | 14      |        | 0001 0100  |

| -         | 15      | 1111   | 0001 0101  |

|           | 16      | 10000  | 0001 0110  |

|           | - 17    | 10001  | 0001 0111  |

|           | 18      | 10010  | 0001 1000  |

TABLE 11-4 BINARY CODED DECIMAL

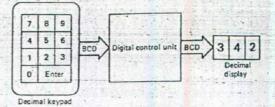

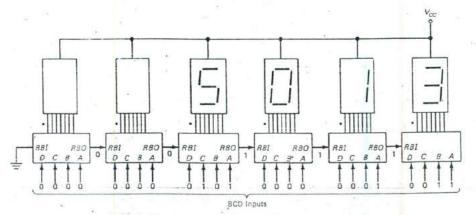

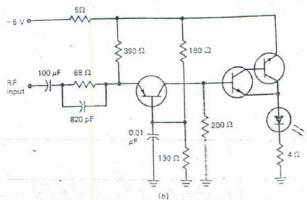

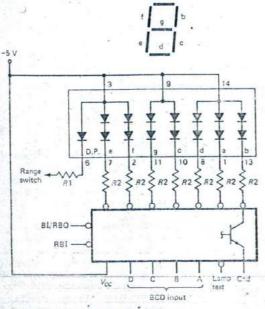

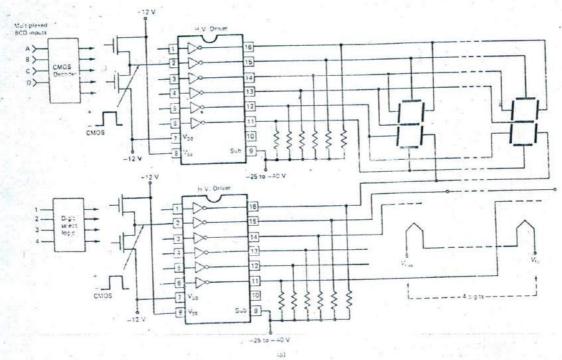

Fig. 11-4 Binary-coded decimal applications.

# SOLUTION

Hex and octal are fine for engineers, technicians, and programmers who have taken the time to learn other number systems. Operators are often not familiar with these number systems. They simply use digital equipment and do not need an understanding of the digital circuits. Figure 11-4 shows a decimal keypad connected to the input of a digital control unit. The output goes to a decimal display. This environment is far more comfortable for most people than a hexadecimal keypad or a binary display. Another code has been developed to interface between the decimal operator and the binary machine conveniently. It is called binary-coded decimal (BCD) and is shown in Table 11-4. It is the same as ordinary binary until numbers greater than decimal 9 are represented. These numbers require an additional group of 4 bits for each decimal digit. The decimal number 309 would require 12 bits, 1234 would require 16 bits,

SOLUTION

# Binary to octal is the reverse process.

# **EXAMPLE 10**

Convert binary 11010100 to octal.

TABLE 11-5 AMERICAN STANDARD CODE FOR INFORMATION INTERCHANGE

| THE PARTY | Column                                                                                          | 0   | 1   | 2        | . 3 | 4   | 5   | 6   | 7    |

|-----------|-------------------------------------------------------------------------------------------------|-----|-----|----------|-----|-----|-----|-----|------|

| Row       | $\begin{array}{c} \text{Bits} \\ 4321 \\ \downarrow \end{array} 765 \rightarrow \\ \end{array}$ | 000 | 001 | 010      | 011 | 100 | 101 | 11  | 0 11 |

| 0         | 0000                                                                                            | NUL | DLE | SP       | 0   | 6   | Ρ.  | . / | р    |

| 1         | 0001 .                                                                                          | SOH | DC1 | 0.51     | 1   | A   | Q   | a   | q    |

| 2         | 0010                                                                                            | STX | DC2 |          | 2   | B   | R   | b   | r    |

| 3         | 0011                                                                                            | ETX | DC3 | #        | 3   | С   | S   | C   | 5    |

| 4         | 0100                                                                                            | EOT | DC4 | S        | 4   | D   | Т   | d   | t    |

| 5         | 0101                                                                                            | ENQ | NAK | %        | 5   | E   | U   | e   | u    |

| 6         | 0110                                                                                            | ACK | SYN | &        | 6   | F   | v   | , f | v.   |

| 7         | 0111                                                                                            | BEL | ETB | 1. 1. 1. | 7   | G   | W   | g   | w    |

| 8         | 1000                                                                                            | BS  | CAN | (        | 8   | Н   | X   | h   | X    |

| 9         | 1001                                                                                            | HT  | EM  | )        | 9   | I   | Y   | i   | У    |

| 10        | 1010                                                                                            | LF  | SUB | •        | 12: | J   | Z   | : j | 2    |

| 11        | 1011                                                                                            | VT  | ESC | +        | :   | K   | [   | k   | 1    |

| 12        | 1100                                                                                            | FF  | FS  | 12 .2    | <   | L   | ١.  | 1   | 1    |

| 13        | 1101                                                                                            | CR  | GS  | -        | =   | М   | 1   | m   | }    |

| 14        | 111:0                                                                                           | SO  | RS  |          | >   | N   | n   | п   | ~    |

| 15        | 1111                                                                                            | SI  | US  | 1        | ?   | 0   | -   | 0   | DE   |

CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 273

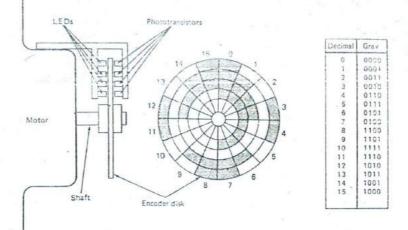

Fig. 11-5 Gray code shaft encoder.

and so on. Binary-coded decimal is not a convenient code for arithmetic operations, and it usually requires more bits than binary. For these reasons, BCD may be used for input and output operations only, and binary-to-BCD and BCD-to-binary code converters will be required.

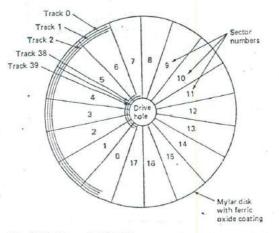

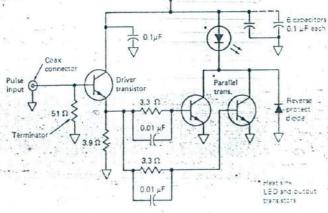

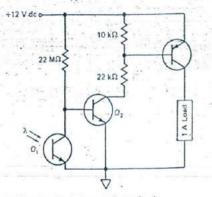

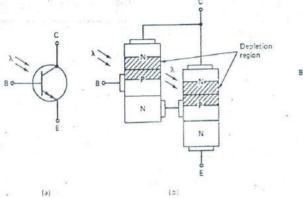

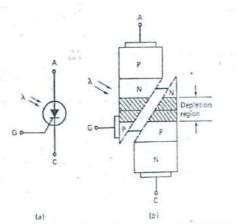

Other special codes are required for special applications. Some are nonweighted, meaning that each bit position does not have a definite weight. The Gray code is an example. Figure 11-5 shows how the Gray code can be used to convert the angular position of a motor shaft, which is analog, into a group of nonweighted 0s and 1s. As the shaft turns, the encoder disk turns with it and presents a clear or an opaque sector to each pair of light-emitting diodes and phototransistors. The 4-bit code that is read from the phototransistor outputs represents one of 16 shaft positions. A five-level code would resolve 32 shaft positions, a six-level code 64 shaft positions, and so on. The Grav code is unique in that no more than 1 bit changes at a time as the shaft rotates. Examine the table in Fig. 11-5 to verify this point. A binaryencoded disk would be error-prone because more than one bit would change at a time as the shaft turned. The Gray code does not lend itself to arithmetic operations, and so code conversion to binary will be required.

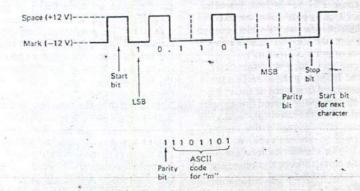

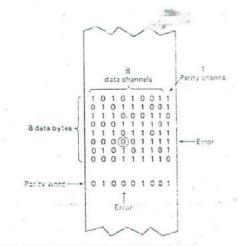

An alphanumeric code is one that represents letters and numbers. The most popular one is the American Standard Code for Information Interchange (ASCII). Table 11-5 shows an ASCII code chart. The bit pattern for each row and column is given. For example, the letter A is in row 1. All characters in this row end with the bit pattern 0001. A is in column 4, and all characters in this column begin with the bit pattern 100. Therefore, the ASCII bit pattern for A is 1000001. Note that ASCII is a 7-bit code. Sometimes an eighth bit is tidded in the leftmost position to act as a parity bit. *Parity* is an error-checking technique. If the parity is supposed to be even, the letter A will be represented by 01000001, which has an even number of 1s in the group. If the parity is odd, the letter A will be represented by 11000001, which contains an odd number of 1s.

#### REVIEW QUESTIONS

1. A digital signal that remains at a level between 0.2 and 2.0 V is in the \_\_\_\_\_ region.

2. The worst-case noise margin in TTL logic circuits is \_\_\_\_\_.

3. Do worst-case noise margins occur with small fanouts or with full fanouts?

4. Can a totem pole output stage source or sink more current?

5. A digital pulse ranges from 0.2 to 3.4 V. What two voltage points will be used when measuring the rise time of the pulse?

6. What voltage point will be used for the pulse of question 5 when measuring propagation delay?

7. Is it always acceptable to substitute a TTL device for an LS TTL device?

8. Is it always acceptable to substitute an LS TTL device for a TTL device?

9. Use Table 11-5 and determine the ASCII code for the letter Z in an odd parity system.

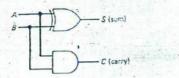

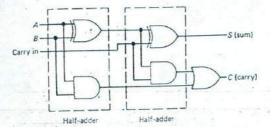

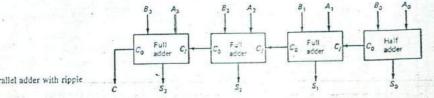

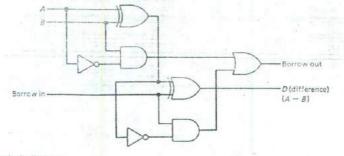

# 11-2 GATES AND COMBINATIONAL LOGIC

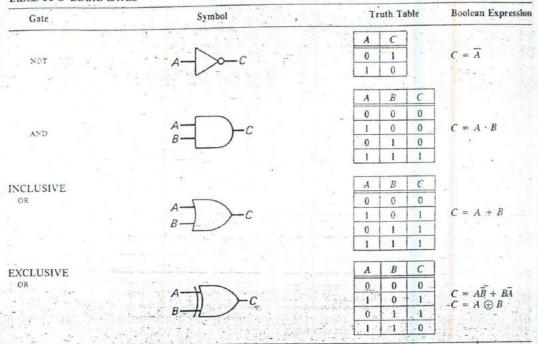

A gate is a decision-making element. It produces an output that is high or low, depending on its input conditions. Table 11-6 shows the basic logic gates.

## TABLE 11-6 LOGIC GATES

The NOT gate, shown at the top of the table, is also called an inverter. The truth table for the NOT gate shows that the input (A) can be low (0) or high (1). When the input is low, the output (C) is high. When the input is high, the output is low. This function is known as logical inversion. The NOT symbol is a triangle with a circle at the output. The circle is important because it tells us that the output is inverted. Boolean algebra is a special branch of mathematics used to describe and design binary systems. The boolean expression for the NOT gate is read as C is equal to NOT A. The bar over the A is an inversion bar. The NOT gate is useful in many situations. Suppose, for example, that a limit switch produces a logic 0 when activated, but it would be more convenient if it produced a logic 1. A NOT gate can be used to invert the switch logic.

Now look at the AND gate in Table 11-6. It has two inputs and its truth table has four rows, one for each possible input combination. The output is high when input A and input B are high. The boolean expression is read C is equal to A AND B. The dot between the A and the B is the symbol for the AND operator. The dot is optional; thus C = AB is an equivalent expression, and so is C = A(B). The AND gate is an "all or nothing" circuit and is useful for activating a load when all of the inputs are high. For example, it may be desirable to activate an alarm circuit when both the pressure and the temperature of some process go high.

Table 11-6 shows two types of OR gates. The inclusive OR gate is often simply referred to as an OR gate. However, to avoid confusion, the other version must be referred to by its full name, exclusive OR. The inclusive OR is an "any or all" gate and produces a high output when either or both of its inputs are high. The exclusive OR gate produces a high output when either A or B is high but excludes the condition where both are high. The inclusive OR gate includes a high output for the condition where both inputs are high. The boolean expression for the inclusive OR gate is read C is equal to A OR B. The plus (+) sign is the OR operator, but you should not read the expression as C is equal to A plus B. The inclusive OR is useful for detecting those situations in which any or all of its inputs are high. For example, it may be desirable to activate an alarm circuit when the pressure is high, or the temperature is high. or both conditions are true. The exclusive OR gate is useful for detecting inequality. Note that it produces a high output only when its inputs are not equal. It may also be used as a comparator because its output is low when its inputs are equal. The boolean expression for the exclusive OR gate is read C is equal to A AND NOT B OR B AND NOT A. This is often shortened as Table 11-6 shows by using the

- ---

#### CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 275

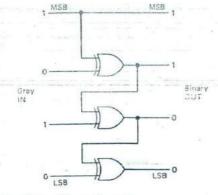

Fig. 11-6 Gray-to-binary code converter.

ring sum symbol, which is the exclusive OR operator. The expression is read C is equal to A exclusive OR B. It can also be read C is equal to A ring sum B.

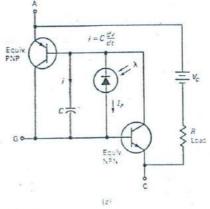

The last section introduced the Gray code. It is a nonweighted code that is often used to encode shaft position. Unfortunately, since it is nonweighted, it is not useful when arithmetic operations are required. Figure 11-6 shows a Gray-to-binary code converter that uses exclusive OR gates. Suppose that Gray code 1010 is presented to the converter. The MSB is a 1 and connects straight through to the output. The next bit is exclusively ORed with the MSB and produces an output of 1. This I is exclusively ORed with the next Gray bit, which is also a 1, producing the next output of 0. This 0 is exclusively ORed with the last Gray bit, which is also a 0; the LSB of the output is 0. By following the decision of each gate, you should be able to verify that the output is equal to binary 1100 or decimal 12. Now, refer again to Fig. 11-5. Try a couple of other shaft positions to test your understanding of the converter circuit.

Except for the inverter, logic gates can have more than two inputs. Figure II-7 shows a three-input AND gate. There are eight possible input combinations, and the truth table has a row for each. The number of combinations is predicted by  $2^N$ , where N is equal to the number of inputs. A four-input gate has 16 input combinations, a five-input gate has 32 input combinations, and so on. Note that only one input combination produces a high output in Fig. 11-7. This occurs when A, B, and C are high.

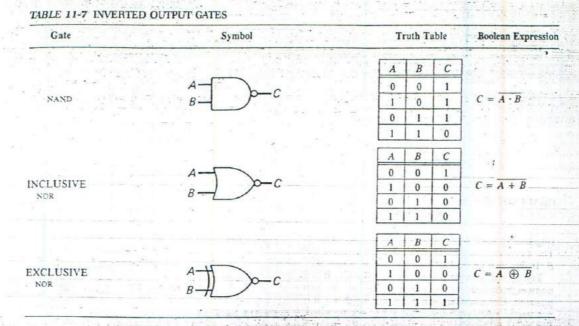

Gate outputs are often inverted (refer to Fig. 11-8). This can be accomplished by following a gate with an inverter. More commonly, it is obtained in one package. The symbol on the right is for a NOT-AND gate or simply NAND gate. Note the inversion circle on the NAND output. Table 11-7 shows the symbols, truth tables, and boolean expressions for the inverted output gates. The truth tables show that the output conditions are inverted from those shown in Table 11-6. The boolean expressions show the inversion bar over the terms and their operators.

| D | - | A | * | B | 4 | C |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| A | 8 | C | -0 |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 1 | 0 | 0 | 0  |

| 0 | 1 | 0 | 0  |

| 1 | 1 | 0 | 0  |

| 0 | 0 | 1 | 0  |

| 1 | 0 | 1 | 0  |

| 0 | 1 | 1 | 0  |

| 1 | 1 | 1 | 1. |

|   |   |   |    |

Fig. 11-7 Three-input AND gate.

Fig. 11-8 NAND gate.

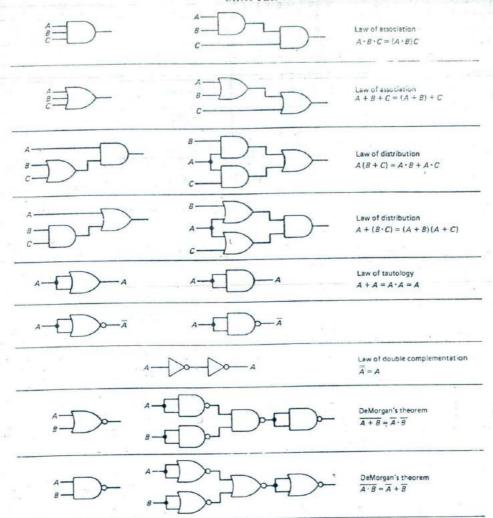

Figure 11-9 shows some of the laws of combination for gates. These laws are useful because they will help you to understand how any logic function can be synthesized from other logic functions. For example, the law of association shows us how to obtain a three-input AND function from two-input AND gates. It also shows that it is possible to obtain a three-input OR function from two-input OR gates. Simply stated, the associative law tells us that it makes no difference as to the order of how AND or OR expressions are combined. The law of distribution shows that there can be two forms of an expression and a circuit can be realized for each. In general, the circuit containing the fewest number of gates is the most desirable. The distributive law is useful when examining an expression to determine whether it can be simplified. For example, as Fig. 11-9 shows, a logic function may be implemented with two or three gates and have the same function. The law of tautology shows that when a variable is ORed or ANDed with itself the result is equal to the variable. Taking this one step further, if the gate is a NOR or a NAND, an inverter is realized by tying the inputs together. The law of double complementation shows that two inversions cancel and that the variable is restored.

The last two rows of Fig. 11-9 illustrate De-Morgan's theorem, which states that the complement of a sum is equal to the product of the complements. Likewise, the complement of a product is equal to the sum of the complements. The word complement means the inversion of a variable or expression. The complement of A means the same

thing as NOT A. Simply stated, the theorem tells us we can break an inversion bar over an operator if we change the operator. For example, in the equation  $\overline{A} + \overline{B} = \overline{A} \cdot \overline{B}$ , the bar is broken over the OR operator and the operator is changed to AND. The theorem shows that it is possible to synthesize a NOR gate from four NAND gates. Figure 11-9 shows that the first two NAND gates are used as inverters since their inputs are tied together. The next gate NANDs the complemented inputs. The theorem shows that the complements are to be ANDed, and the last NAND gate acts as an inverter to meet that requirement because when a NAND gate is followed by an inverter the AND operation results. An OR function can therefore be realized by leaving off the last inverter. The last row of Fig. 11-9 shows that the NAND function can be synthesized from four NOR gates. The complement of A is NORed with the complement of B and then inverted. The AND function is realized by leaving off the last inverter. NAND gates are often referred to as universal logic elements because it is possible to synthesize any logic function by combining them. The same thing is true of NOR gates.

DeMorgan's theorem has led to alternate symbols for NAND and NOR gates. Figure 11-10 shows these alternate symbols. The NAND gate is sometimes represented as an OR gate with inverted inputs. The NOR gate may be represented as an AND gate with inverted inputs. You may find both the standard and the alternate symbols used on the same logic diagram. The purpose of using both is to represent circuit operation more clearly by emphasizing high inputs or inverted (low) inputs.

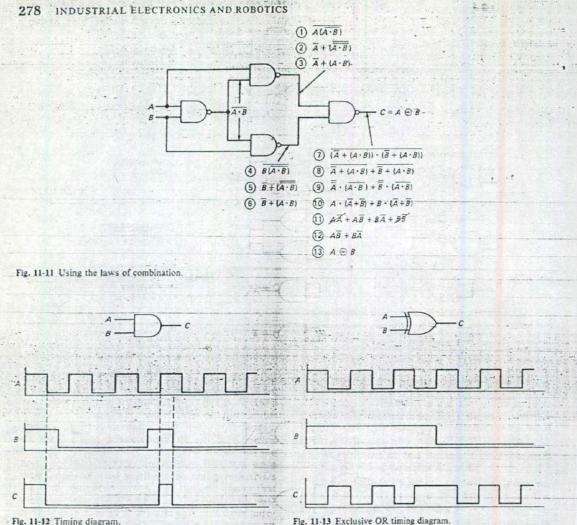

The *laws of combination* are also useful to solve circuits. For example, Fig. 11-11 shows a combinational logic circuit based on four NAND gates. What is the output supposed to be? Follow the steps:

- 1. At this point we find variable A combined with the NAND of variables A and B.

- It is desired to simplify this so the bar is broken, and the AND operator is changed to the OR operator (DeMorgan's theorem).

- The law of double complementation allows us to remove the bars.

- 4-6. These steps are the same as the first three.

- 7. The simplified terms from steps 3 and 6 are NANDed.

- The bar is broken in the middle, and the operator is changed to OR.

- 9. The bar is broken at the left and at the right, and the operators are changed.

- 10. The double bars are removed.

- 11. The term is multiplied (ANDed) with each expression in the parentheses. Two terms cancel, since any time a variable is ANDed with its complement the result is 0. You may verify this by looking at the AND gate truth table.

- 12-13. The result is the exclusive-OR operation.

Another basic understanding that you will need to work with digitial systems is in the area of dynamic

# CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 277

Fig. 11-9 Laws of combination.

operation. A logic circuit is *dynamic* if it is undergoing change. Look at Fig. 11-12, which shows some timing diagrams for a two-input AND gate. Timing diagrams relate dynamic conditions among inputs and outputs. Input A is shown as a square wave. Input B is a rectangular wave of low duty cycle. Output C is high only during those periods when both A and B are high. Now look at Fig. 11-13; it shows the timing diagram for an exclusive OR gate. Note that the output waveform is the inverse of input A when input B is high. When B is low, the output is in phase with input A. Verify this operation by looking at the exclusive OR truth table if necessary. The exclusive OR gate is sometimes called a *program*-

Alternate NOR symbol

Fig. 11-10 Alternate symbols.

Fig. 11-12 Timing diagram.

mable inverter since its output will be the complement of its input when its other input is high.

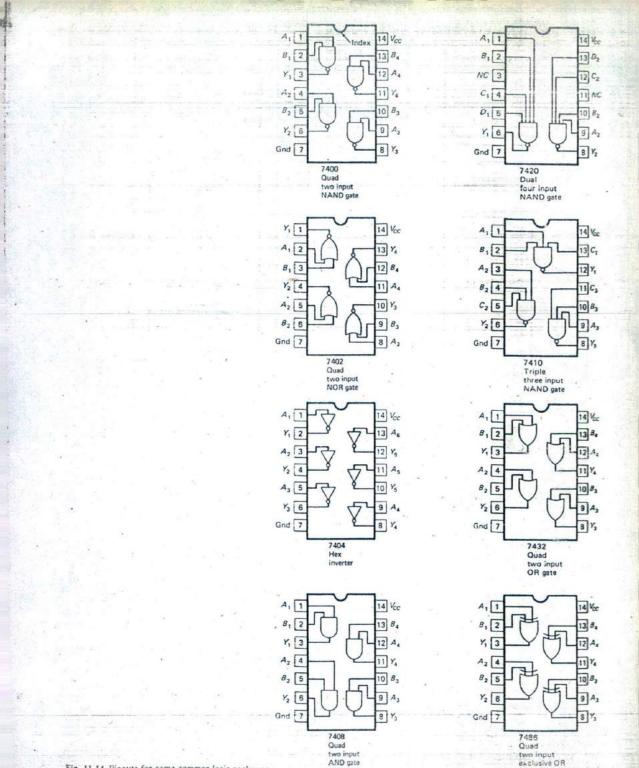

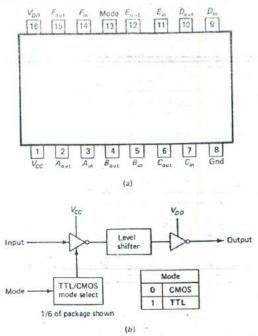

Digital integrated circuits often contain several logic gates in one package. Figure 11-14 shows the pinouts for some common 7400 series devices. The 7400 is a quad two-input NAND gate. It has four gates per package. The 7404 is called a hex inverter since it has six gates per package. The 7420 contains only two NAND gates because each one has four inputs and there are only 14 pins available. In the TTL family and subfamilies  $V_{CC}$  is +5 V and is applied to pin 14 of each package. Pin 7 is grounded in each case. This is not a uniform standard, however. Some 7400 devices have different ground and supply pins, and some have more than 14 pins. The output pins are labeled Y so they are not confused with the input pins, which are labeled A through D and beyond, depending upon how many inputs there are

per gate. As mentioned before, the pins are counted counterclockwise from the index when viewing the packages from the top.

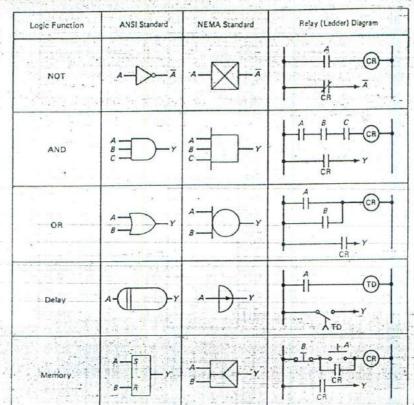

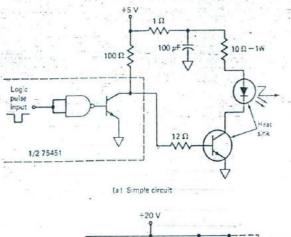

The industrial technician is exposed to many types of control circuits. Relays were the mainstay of controls at one time but are now being replaced by static controls. Static controls are so named because they have no moving parts. Figure 11-15 compares static controls with relay controls. The American National Standard Institute (ANSI) logic symbols have gained widespread acceptance, but the National Electrical Manufacturer's Association (NEMA) logic symbols are found on many industrial schematics and wiring diagrams. The NOT function can be achieved with a gate or by using a relay with normally closed contacts. The ladder diagram for the AND function shows the control contacts in series so all will have to be closed to energize the relay contacts. The OR

Fig. 11-14 Pinouts for some common logic packages.

gate

i,

280 INDUSTRIAL ELECTRONICS AND ROBOTICS

Fig. 11-15 A comparison of static and relay controls.

function is realized by wiring the control contacts in parallel. A time delay relay can be replaced with a static device such as an NE555 timer. The memory function is based on a static device such as a latch or uses a second set of relay contacts to hold the circuit on until it is reset by switch B. Latches are discussed in the next section of this chapter.

# **REVIEW QUESTIONS**

10. Which gate acts as an all or nothing decision element?

11. If a gate is simply referred to as OR, which type is it?

12. Will the circuit of Fig. 11-6 produce the correct output instantaneously? Why?

13. Calculate the total propagation delay for Fig. 11-6 if the circuit is built by using standard TTL components.

14. Refer to Fig. 11-12. What will waveform C look like if waveform B is constant at logic 1?

# 11-3 LATCHES AND FLIP-FLOPS

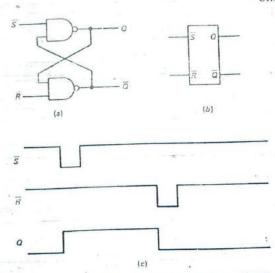

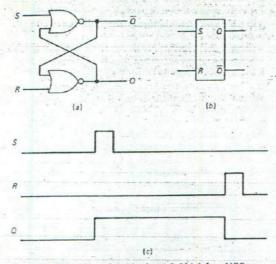

A latch is a sequential logic element. It has a memory characteristic that makes it useful for storing events and binary numbers. Figure 11-16(a) shows an R-S latch based on two NAND gates. The R is the reset input, and the S is the set input. The inputs are activated by logic low signals. This is why the standard symbol shown in Fig. 11-16(b) of the illustration indicates NOT S and NOT R. The latch has two outputs: Q and NOT Q. When Q = 0, NOT Q = 1, and this is the reset condition of the latch. When Q = 1, NOT Q = 0, and this is the set condition of the latch. Figure 11-16(c) of the illustration shows the timing diagram. Starting at the left, the latch is initially in the reset condition since Q is low. Moving to the right, the set input goes momentarily low. The Q output responds by going high, and the latch is now set. Moving more to the right, the reset input goes momentarily low, and the Q output goes low again. The latch has been reset.

The R-S latch works because of feedback. Look

Fig. 11-16 Low activated R-S latch. (a) R-S latch from NAND gates. (b) Symbol. (c) Timing diagram.

at Fig 11-16(a). The output of each NAND gate feeds back to the input of the other gate. Recall that the truth table for the NAND gate shows a logic high at the output for all input conditions except the one where both inputs are high. Assume that the latch is in the reset condition (Q = 0 and NOT Q = 1) and that both inputs are high. This means that the top NAND gate has two high inputs and its output must be low. The bottom NAND gate will have one high input and one low input, and its output must be high. The truth tables are satisfied, and the circuit is stable in this condition. Now, suppose the set input goes low. The top gate now has one low input and one high input, and its output goes high. This high is fed back to the bottom gate, so that it now has both inputs high and its output goes low. Note that the latch is now in the set state: Q = 1 and NOT Q =0. The low output from the bottom gate feeds back to the top gate, and it now has both inputs low. This changes nothing, and the top gate still has a high output. When the set pulse ends, the top gate has one high input and one low input and there is no change. The latch is now stable in the set condition. Because of the feedback, it remembers that it was set and will stay in the set mode until a reset pulse comes along or the circuit is powered down.

To analyze digital circuits that use feedback, begin with the circuit in some stable condition. Verify that the truth tables are correct for each gate. Then, introduce a change and follow the change through by using the truth table for each gate. Use this technique now with the circuit of Fig. 11-16(a). Start with the latch in the set condition and with both inputs high. Verify the truth tables. Then apply a reset pulse

# CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 281

(logic 0) and trace the changes through the circuit. Prove to yourself that the outputs change as expected and that the circuit remains reset after the reset pulse is removed.

Simple R-S latches work very well, but they are susceptible to being forced to an illegal output state. They are also capable of settling to an unpredictable output state in some cases. For example, what would happen in Fig. 11-16(a) if logic 0 pulses were applied to the inputs at the same time? Both NAND gates would have high outputs. Both Q and NOT Q would be high at the same time. This is illegal, since a variable and its complement cannot be the same. Then, what would happen if both pulses returned to logic 1 at the same time? Both gates would "race" to have a low output. The gate with the shorter propagation delay would win the race and force the other gate to have a high output. The latch would resume a legal output state, in either the set mode or the reset mode. Such unpredictable behavior is unacceptable in digital circuits. This condition is known as pulse race or simply race and must be avoided.

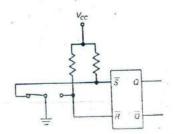

Figure 11-17 shows an application for the R-S latch. It is being used to debounce a mechanical switch. When switch contacts close, they bounce. They make and break rapidly until the bouncing stops. This process lasts for several milliseconds and can create dozens of extra pulses in a circuit. The bounceless switch circuit avoids this problem because when the switch is thrown, it grounds either the set or the reset input of the latch, so the latch is either set or reset. As the contacts bounce open and closed, there is no change in the latch because once it is set it is not affected by subsequent set pulses. Likewise, once it is reset it is not affected by subsequent reset pulses. The pull-up resistors ensure a logic high at the inputs when not grounded by the switch. The circuit will work without the resistors if the latch is a TTL family device since the inputs float high. However, it is considered good practice to use the resistors.

Figure 11-18 shows an R-S latch configured from two NOR gates. Note that the Q output is taken from the bottom gate and the NOT Q output is taken from the top gate. The symbol, shown in Fig. 11-18(b), locates the Q output on top because this is its stan-

Fig. 11-17 A bounceless switch circuit.

Fig. 11-18 High activated R-S latch. (a) R-S latch from NOR gate. (b) Symbol. (c) Timing diagram.

dard position. It is activated by logic high signals applied to the set and reset inputs. Remember that the output of a NOR gate is low if any or all of its inputs are high. Study the timing diagram and verify circuit operation. The NOR latch is susceptible to the same problems as the NAND latch. If both inputs are driven high, the outputs will assume an invalid condition: both Q and NOT Q will be at logic 0. Then, if both inputs go low at the same time, the outputs will race, and the latch will settle into the set or reset condition.

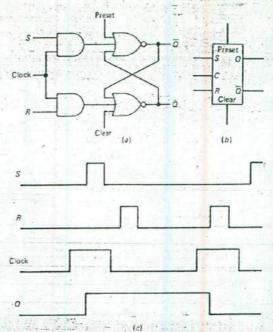

It is often desirable to enable a latch only during a specified period of time. Figure 11-19 illustrates a clocked R-S latch with asynchronous preset and clear inputs. Note that Fig. 11-19(a) shows two AND gates at the front end-of the latch. These gates share a common input line called the clock or enable input. It does not matter what is happening at the set and reset inputs if the clock input is low, since all inputs to an AND gate must be high for the output to go high. Study the timing diagram in Fig. 11-19(c). Start at the left, where the latch is initially in the reset condition (Q is low). The clock signal goes high, enabling both inputs. Next, the set input goes high and the latch is set. Then the clock signal goes low. Now a reset pulse comes along, but the latch is not reset because the inputs are disabled. The next reset pulse does reset the latch since it occurs when the clock is high. That time when the clock is high is often referred to as a window. Input pulses must be synchronized with the clock window to have any effect on the output; the S and R inputs are considered to be synchronous inputs for this reason. The preset and clear inputs are asynchronous since they can be applied at any time to set or clear the latch. The asynchronous inputs are often used to initialize the circuits to a known condition after power-on.

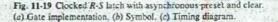

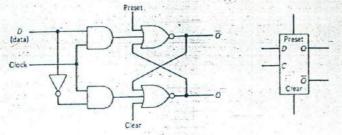

Figure 11-20 shows a clocked D latch. The D input is the only synchronous input. An inverter has been added to supply inverted data to the bottom gate. If the D input is high during the clock window, a logic high is applied to the top NOR gate, and a logic low is applied to the bottom NOR gate. The latch is driven to the set condition if it hasn't already been set. If the D input is low during the window, a high will be applied to the bottom NOR gate; it will reset the latch if it wasn't previously in that mode. The latch is said to be transparent because the output follows the data input during the time that the clock is high. The advantage of the D latch is that race has been eliminated at the synchronous input. It is also no longer possible to force the outputs to an illegal mode since there is only one input. However, it is still possible to race the latch and force the outputs to an illegal mode with the asynchronous preset and clear inputs.

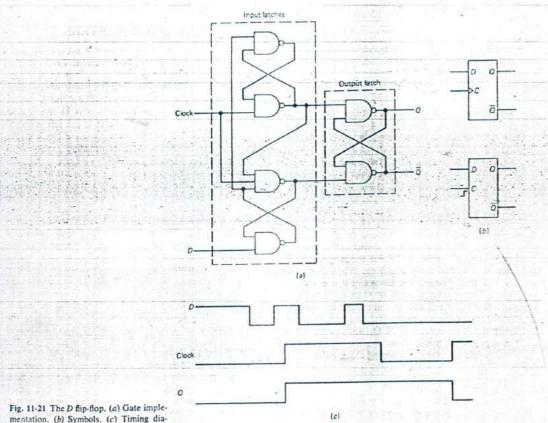

Now it is time to look at *flip-flops*; these are circuits with much in common with latches. In fact, many people use the term *flip-flop* to describe any bistable circuit, including the latches studied to this point. However, the digital IC manufacturers generally reserve the term for devices that trigger on a clock edge. Latches are level-sensitive, by comparison. Figure 11-21 shows the circuit, symbol, and the timing diagrams for a D flip-flop. The circuit uses a combination of input latches with the familiar NAND output latch. The D input is sampled only during the

. .

# CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 283

Fig. 11-20 Clocked D latch with asynchronous preset and clear.

(a) Gate implementation

(b) Symbol

mentation. (b) Symbols. (c) Timing diagram.

positive edge of the clock and not during a clock window. There is no clock window in a flip-flop. Study the timing diagram. The flip-flop starts out in the reset mode. Next, the D input goes low and this has no effect on the output. Next, the D input goes high, with no immediate effect on the output. Now, the clock goes high, enabling the input latches, and the D input is sampled at this time. Note that the Dinput goes low again while the clock is still high with no effect on the output; again there is no clock window. Finally, on the last positive clock edge, the flipflop is reset because the D input is low at that time. Figure 11-21(b) shows two symbols that are used to differentiate between edge- and level-sensitive devices. A triangle can be added at the clock input, or a positive edge can be drawn near the clock input.

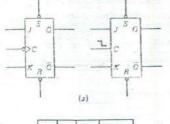

The J-K flip-flop is one of the most versatile and popular of all sequential logic circuits. Figure 11-22 depicts two symbols and a truth table for the circuit. Most J-K flip-flops are negative-edge devices. They

| 7 | ĸ | 0 1 | Mode    |

|---|---|-----|---------|

| 0 | 0 | 0,  | Inhibit |

| 0 | 1 | 0   | Reset   |

| 1 | 0 | 1   | Set     |

| 1 | 1 | à,  | Toggie  |

Fig. 11-22 Negative edge J-K flip-flop with asynchronous set and reset. (a) Symbols. (b) Truth table.

sample the J and the K inputs at the time when the clock is falling from logic 1 to logic 0. Figure 11.22(a) shows an inversion circle at the clock input. and Figure 11-22(c) shows the alternate symbol, which uses a negative edge. The truth table in Figure 11-22(b) requires some explanation. It uses a notation that refers to Qn and to Qn+1. The Qn refers to the Q output just before the negative edge, and Qn+1 refers to the Q output just after the negative edge. When J = 0 and K = 0, the truth table shows that the output is Qn. This simply means that Q did not change. It is in the same condition as it was before the clock edge. This is called the inhibit mode since the flipflop is inhibited from changing. When J = 0 and K = 1, the Q output will always be 0 after the clock edge. This is known as the reset mode. When J = 1and K = 0, the Q output will always be 1 after the edge; this is the set mode. If J = 1 and K = 1, the output will be equal to NOT Qn, and the flip-flop will change states; this is known as the toggle mode. It will toggle on every succeeding clock pulse.

# **REVIEW QUESTIONS**

15. Refer to Fig. 11-16(c). If the diagram included a waveform for NOT Q, how would it compare with the Q waveform?

16. Refer to Fig. 11-16(c). If a second set pulse followed the first set pulse and preceded the reset pulse, how would the Q waveform change?

17. Refer to Fig. 11-17. What are the resistors called?

18. Refer to Fig. 11-18. What output state results if both the set and reset inputs are high? What is the condition called if both inputs go low at the same time?

19. Refer to Fig. 11-19. What will happen if the set and reset inputs race when the clock is at logic 0?

20. Refer to Fig. 11-20. If the latch portion of the circuit were constructed with NAND gates instead of NOR gates, what gates should be substituted for the AND gates to ensure an identical timing diagram?

21. Refer to Fig. 11-20. Is it possible to "race" this latch? If so, at which input(s)?

22. Refer to Fig. 11-21(c). Why doesn't the Q output change when the data change in the clock window?

## 11-4

## COUNTERS AND REGISTERS

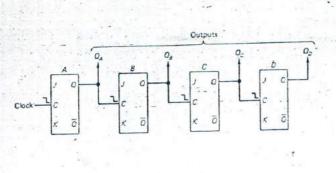

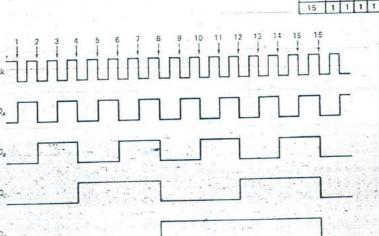

A counter is a circuit based on the sequential logic elements studied in the last section. Look at the binary ripple counter in Fig. 11-23. It is an arrangement of four J-K flip-flops and is capable of counting from binary 0000 to binary 1111. The J and K inputs are all floating, so every flip-flop is in the toggle mode. The timing diagram starts at the left with all four outputs at 0. On the first negative clock edge. QA goes high. On the second negative clock edge. QA goes low, providing a negative edge for the second flip-flop so that QB goes high. Follow the timing diagram through to the sixteenth negative clock edge and note that the counter is reset at this time and all four outputs are once again at 0. Thus, the counter has 16 unique states. This is also called the modulus of the counter. The modulus is equal to 2", where N is the number of sequential logic elements in the counter.

Most electronic diagrams are drawn with the input signals entering at the left. Binary numbers are printed with the LSB at the right. These two conventions are in conflict when describing counters. Figure 11-23 solves this problem by rearranging the truth table columns. Transistor  $Q_A$  is the LSB and heads the right-hand column. Transistor  $Q_D$  is the MSB and heads the left-hand column.

Figure 11-23 is called a binary ripple counter because the count ripples from flip-flop to flip-flop. Check what happens on the eighth negative clock edge. Outputs A, B, and C all go low, and output D goes high. Will these four events occur simultaneously? No, the count will ripple from A to B to C and finally to D, and D will not go high until four propagation delays after the clock edge. The highfrequency performance of ripple counters is limited. Figure 11-24 illustrates a synchronous binary counter with better high-frequency performance. The clock is directly applied to each flip-flop. This means that every flip-flop can toggle at the same time (they are synchronous). Additional connections and some combinational logic are required to allow the synchronous counter to achieve the correct binary se-

Count 00 00 03 04 0 0 0 0

0 0 0 1

0 0 1 0 0 0 1 1

0 1 0 0

0 1 0 1 0 1 1 0

0

1 1

0 1 1

1 1 0

0

1 2

3

4

5

6

7 0 1

8 1 0 0 0 1

9 1 0

10 1 0 10

11 1 0 1 1 100

12 1

13 1

14 1

Fig. 11-23 Binary ripple counter.

11

Cloc

Fig. 11-24 Synchronous binary counter.

quence. The  $Q_A$  output also goes to the J and K inputs of flip-flop B. If you check the timing diagram from Fig. 11-23 you will see that QB is supposed to toggle only on those edges when QA is high before the edge. Also notice that Qc toggles only on the edges where both A and B are high before the edge. Finally, note that QD toggles only on those edges where A, B, and C are high before the edges. It should now be clear how the connections and AND gates of Fig. 11-24 function.

The natural modulus of a counter is 2<sup>N</sup>. It is possible to use feedback to reduce the natural modulus.

285

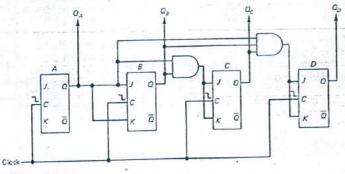

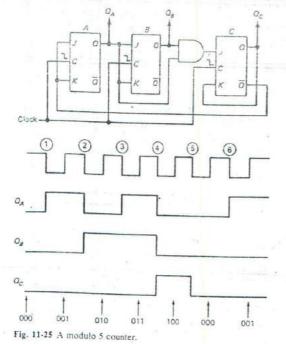

For example, Fig. 11-25 shows a modulo 5 counter. It uses three flip-flops, and the natural modulus is  $2^3 = 8$ . However, feedback from flip-flop C to flipflop A and from Q to K at flip-flop C reduces the natural modulus, and the counter has only five unique states. They range from binary 000 to 100. The counter does not advance from binary 100 to binary 101; instead it resets to 000. As in the last circuit, QA feeds the J and K inputs of flip-flop B and QA is ANDed with QB to control the J input of flipflop C. The timing diagram follows a natural pattern up to the fifth negative clock edge. At the fifth edge, QA does not toggle. This is because NOT Qc was low before the edge and the feedback put flip-flop A into the inhibit mode. Also note that Qc does toggle on the fifth edge because Qc was high before the clock edge, and so was the K input of the flip-flop. With J = 0 and K = 1, the flip-flop is in the reset mode.

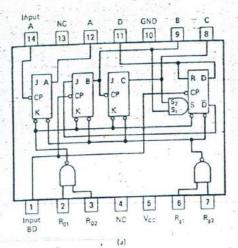

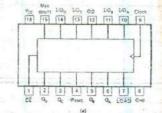

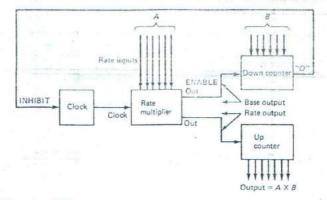

A modulo 5 counter can be combined with a modulo 2 counter to make a modulo 10 counter. Counters with 10 states are called *decade counters*; if they follow the BCD count sequence, they are called *BCD counters*. Figure 11-26 shows the pinout, count sequence, and reset truth table for a 74LS90 decade counter. The output of the modulo 2 counter is pin 12 and is connected to the input of the modulo 5 counter at pin I when the device is to be used as a BCD counter. The clock is applied to pin 14. You will recall that binary-coded decimal follows the standard binary sequence up to a count of 1001. The BCD count sequence is indicated in Fig. 11-26(b). For some applications, the count sequence is not important, but the division and the output waveform are. The BCD count sequence shows that the frequency at output D (pin 11) will be equal to onetenth the clock frequency, but the waveform will be a rectangular pulse of low duty cycle. It is possible to have the IC divide the input frequency by 10 and produce a square wave (50 percent duty cycle) at the output. This is accomplished by feeding the clock into pin 1, connecting pin 11 to pin 14, and taking the output signal from pin 12. The output from a modulo 2 counter is a square wave; therefore, dividing by 5 first and then by 2 produces the desired waveform. However, when this is done, the BCD count sequence is lost.

Figure 11-26 shows the truth table for the decade counter. It has four reset inputs. An X indicates a *don't care* condition, meaning that either a logic 0 or a logic 1 may be applied at that particular reset pin. There are three reset/preset combinations: two of them reset the counter to 0000 and one presets it to 1001. There are four count combinations, and any one of them may be used for counting.

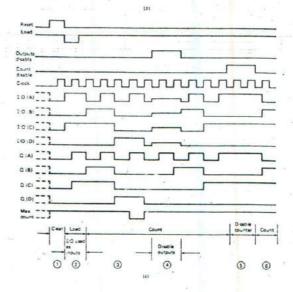

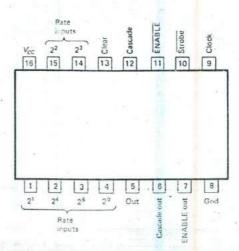

Some digital counters are programmable; Fig. 11-27 is an example. The DM8555 is a decade counter that can be preloaded (or preset) with a BCD number. It has a binary counterpart with the part number DM8556 that can be preloaded with a 4-bit binary number. This allows the modulus of the devices to be adjusted (programmed) by changing the number that is preloaded. For example, if the counter is preset to BCD 0111, the next count will be 1000, then 1001; then it can be preset again to 0111. In this case, the modulus has been programmed to 3. Counters with this capability are known as modulo-N counters. To facilitate presetting, the device has four I/O pins for loading data into the counter. Follow the typical timing diagram shown in Fig. 11-27(c). First, the counter is cleared to zero by applying a reset pulse to pin 4. Second, the counter is preset to BCD 5 by applying 0101 to I/O pins 14, 13, 11, and 10 and by applying a negative load pulse to pin 7. Note that this sets outputs QD through QA (pins 2, 3, 5, and 6) to 0101 and occurs at the positive clock edge (this is a synchronous load). Third, the count progresses 6, 7, 8, 9, 0, 1, 2, 3, 4, and 5. Fourth, during the count, the I/O pins are disabled for a period of time by applying a disable pulse to pin 12 (more on this later). Fifth, the counter is disabled for a time by applying a high pulse to pin 1. Sixth, the count resumes to BCD 6.

The DM8555 counter is very flexible and can be used in many ways. It also lends itself to bus-structured digital systems. A bus is an arrangement in which devices are connected in parallel on several circuit paths for binary information transfer. Many devices are typically connected to the bus and must be isolated from each other at times. For example, if one logic package tries to pull a bus line to logic high and another tries to pull a bus line to logic low, this precess creates a problem called bus con-

|       | Output |     |    |    |  |  |

|-------|--------|-----|----|----|--|--|

| Count | Ď      | С   | В  | A  |  |  |

| 0     | 0      | 0   | 0  | 0  |  |  |

| 1     | 0      | 0   | 0  | 1  |  |  |

| 2     | 0      | 0   | 1  | 0  |  |  |

| 3     | 0      | 0   | 1  | 1  |  |  |

| 4     | 0      | 1 - | 0  | 0  |  |  |

| 5.    | 0      | 1   | 0  | 1  |  |  |

| 6.    | 0      | 1   | 17 | 0  |  |  |

| 7     | 0      | 1   | 1  | 1  |  |  |

| . 8   | 1.     | D   | 0. | 0  |  |  |

| 9     | 1 1    | 0   | 0  | 11 |  |  |

|  | ÷. |  |

|--|----|--|

|     | Reset           | 1925 | 1               | Out                              | cout. | _ |   |  |

|-----|-----------------|------|-----------------|----------------------------------|-------|---|---|--|

| Rot | R <sub>02</sub> | R.,  | R <sub>g2</sub> | D                                | С     | В | A |  |

| 1   | 1               | 0    | X               | 0                                | 0     | D | 0 |  |

| 1   | 1               | x    | 0               | 0                                | 0     | 0 | 0 |  |

| x   | X               | 1    | 1               | 1                                | 0     | 0 | 1 |  |

| x   | 0               | x    | 0               | COUNT                            |       |   |   |  |

| 0   | x               | 0    | X.              | COUNT                            |       |   |   |  |

| 0   | x               | x    | 0               |                                  |       |   |   |  |

| x   | 0               | 0    | X               | COUNT<br>r a logical 0 may be pr |       |   |   |  |

(c)

Fig. 11-26 Decade counter. (a) Pinout. (b) Count sequence. (c) Reset/count.

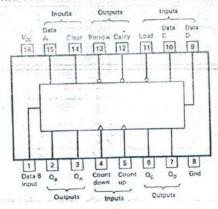

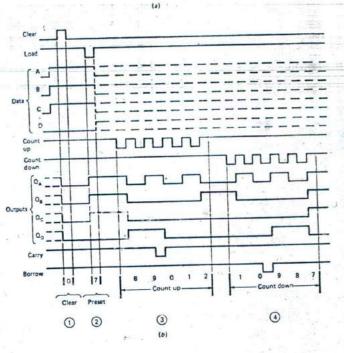

tention. Bus contention can be avoided by using logic devices with tri-state outputs. A tri-state output can be at one of three valid conditions: logic high, logic low, or high impedance (tri-stated). The four I/O pins on the DM8555 are tri-state. Any time that pin 12 (output disable) is at logic high, the I/O pins are disabled and go into their high-impedance state. This is shown with Zs in the truth table of Fig. 11-27(b). Thus, the I/O pins can be effectively disconnected from the bus, allowing some other logic package to place data on the bus without the problem of.bus contention. The four Q output pins of the DM8555 are standard totem pole outputs and cannot be tristated. All of the counters discussed to this point have been up counters, which show an increasing count with each clock pulse. Down counters, which show a decreasing count with each clock pulse, are also available. Figure 11-28 represents a 74LS192 up/ down BCD counter. It is also available in a 4-bit binary version with the part number 74LS193. Both versions are fully programmable and can be used as modulo-N counters. Each output can be set to a high or a low by entering the desired data at the inputs and then pulsing the load input low. This is an asynchronous load since it is independent of the clock inputs. Figure 11-28(b) is a typical timing diagram. First, the outputs are reset to 0 by applying a clear

- Califo

|      | Ca | intro: Inp | uts |       |     | 1/0/ | torts           |      |    | Active | Outputs         |                 |

|------|----|------------|-----|-------|-----|------|-----------------|------|----|--------|-----------------|-----------------|

| LOAD | ĈĒ | CLK        | 00  | Reset | 10, | 1/0, | 1/0_            | 1/05 | 0. | ٩,     | Q.              | C <sub>o</sub>  |

| н    | x  | X          | L   | н     | L   | L    | L               | L    | L  | L      | - 1             | L               |

| H    | x  | x          | н   | н     | z   | z    | z               | Z    | L. | 1      | - 1             | 1               |

| H    | ×  | L          | L   | L     | 0.0 | Q.a  | Q <sub>op</sub> | Que  | 0  | Gue    | R.a.            | Q <sub>pc</sub> |

| H    | ×  | L          | н   | 1     | z   | z    | 2               | z    | 0  | 0      | Q <sub>co</sub> | 0,00            |

| L    | н  | 1          | 6   | L     |     | b    | c               | d    | A  | B      | C               | D               |

| н    | L  | t          | L   | L     |     | COL  | UNT             | 100  |    | CON    | INT             |                 |

| H    | L  | t.         | н   | L     | z   | z    | z               | z    |    | CO     |                 |                 |

The LIO pins are used as inputs when they are TRI-STATED, and LOAD input is Low. They are outputs and activ The LO pine are used as inputs when may set introduced to use used as inputs when the CAR Down in High and Ob a Low. N = Kiph Lowi (Direct) Straty (Strat) X = Cont The Straty (Strat) X = Cont Cher Instand (Strate) that inputs A, B, C, D respectively  $Q_{ab}, Q_{ab}, Q_{ab}, Q_{ab}$  The level of  $Q_a, Q_c, Q_c$ , respectively, before the lack and and the strategy of the level of  $Q_a, Q_c, Q_c$ ,  $Q_c$ , respectively, before the lack and and the strategy of the lack of the strategy of the lack of the lack of the lack of the strategy of the lack of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the strategy of the lack of the strategy of the lack of the strategy of the strategy of t

Fig. 11-27 DM8555 programmable decade counter. (a) Pinout. (n) Truth table. (c) Typical timing diagram.

pulse to pin 14. Second, the counter is preset to BCD 7 by applying 0111 to the data pins and pulsing pin 11 low. Third, the count progresses upward to 8, 9, carry, 0, 1, and 2 as count-up pin 5 is clocked. Fourth, the count progresses down to 1, 0, borrow, 9, 8, and 7 as count-down pin 4 is clocked. The carry and borrow pins are used to cascade more than one device. Cascading is accomplished by feeding the carry and borrow outputs to the count-up and countdown inputs, respectively, of the succeeding counter.

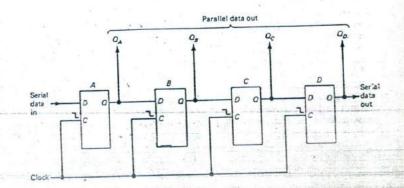

Shift registers constitute another category of digital circuits based on sequential logic elements. They are useful for temporary storage, change of data from one format to another, and sequence control and timing. Figure 11-29 shows a 4-bit serial load shift register. Data are clocked into the register at the data input of D flip-flop A. Four clock pulses are required to load a 4-bit word into the register. Then the data are available in parallel form at the Q outputs. The first data bit entered is available at output Qn, and the last, or fourth data bit, is available at output QA. The shift register is useful for converting serial data (one bit at a time) to parallel data (all bits at a time). It is also useful for temporary storage of data. If the data are needed later, they can be retrieved in serial form at output QD. The first bit that was loaded is immediately available at the serial data output. Then, three clock polses will be required to shift the other CHAPTER 11 DIGITAL CIRCUITS AND DEVICES 289

Fig. 11-28 74LS192 synchronous up/down counter. (a) Pinout. (b) Typical timing diagram.

Fig. 11-29 Shift register.

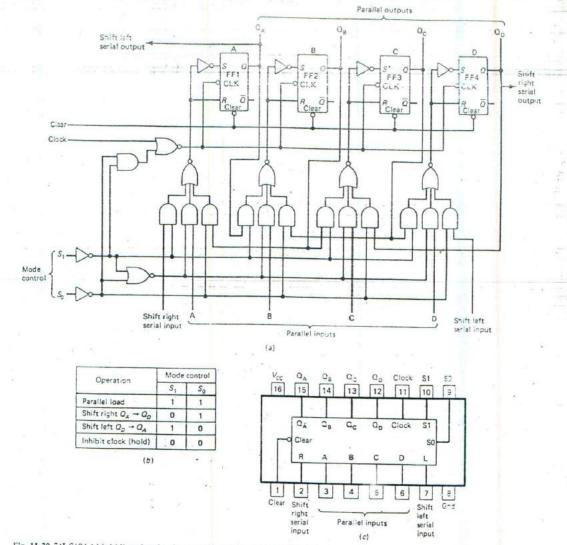

Fig. 11-30 74LS194 4-bit bidirectional universal shift register. (a) Logic diagram. (b) Mode control. (c) Pinout.

3 bits to the output. A register of this type is sometimes called a *first-in first-out* (FIFO) register.

A much more versatile device is shown in Fig. 11-30. It is a 74LS194 universal 4-bit shift register. It is capable of shift right, shift left, and parallel loading and has parallel outputs. Figure 11-30(b) shows the truth table for the two mode control pins  $S_1$  and  $S_2$ . When both mode control pins are high, parallel data are loaded into the register. This occurs because a NOR gate senses the inverted mode signals. With both mode inputs high, both NOR gate inputs are low. The output of the NOR gate is therefore high.

and it supplies a logic high to one lead of each of the center AND gates at the bottom of the logic diagram. The output of each AND gate will follow the data applied at the parallel inputs. The data reach each flip-flop through a NOR gate and an inverter and are loaded on the first positive clock edge. With the mode control in the shift right pattern ( $S_1 = 0$  and  $S_0 = 1$ ), a high is supplied to one input of every left-hand AND gate in the bottom group. The shift right serial input is now active, and data can be clocked into flip-flop A. The data from A will shift to B since its AND gate is also active, and so on. Reversing the

| O <sub>A</sub> | 0, | 0 <sub>c</sub> | 0, | OE | Clock<br>pulse | -         |

|----------------|----|----------------|----|----|----------------|-----------|

| 1              | 0  | 0              | 0  | 0  | 0              |           |

| 0              | 1  | 0              | 0  | 0  | 1              | -         |

| 0              | 0  | 1              | c  | 0  | 2              | } N<br>51 |

| 0              | 0  | C              | 1  | C  | 3              |           |

| 0              | 0  | 0              | 0  | 1  | 4              |           |

| 1              | 0  | 0              | 0  | 0  | 5              |           |

Fig. 11-31 Circulating shift register (ring counter).

mode control pattern ( $S_1 = I$  and  $S_2 = 0$ ) places a logic high at one input of each right-hand AND gate in the bottom group. This activates the shift left serial input, and data are clocked into flip-flop *D*. The output of *D* is clocked into *C* since its AND gate provides a data path to the left, and so on. With both mode control pins low, the shift register is inhibited because the clock cannot get through the NOR gate at the left of the diagram. Note that the other NOR gate input is from an AND gate which has both inputs high when the mode control pins are both low. The AND gate output will be high, holding the clock NOR gate output low.

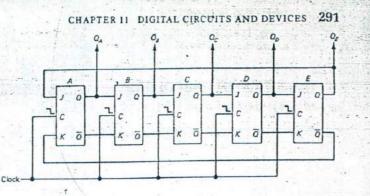

The output from a shift register can be connected back to the input. The data will circulate endlessly in this case as the register is clocked. Refer to Fig. 11-31. This circuit is known as a ring counter. Assume the initial condition is that flip-flop A is set and all others are reset. On the first negative clock edge, the high bit will shift to the right by one position. It will shift to the right again on the second negative edge. When the fifth clock pulse comes along, the high bit shifts from flip-flop E to A. Note that ring counters have N unique states, where N is the number of flip-flops. Ring counters are sometimes used as control sequencers: one operation follows another, followed by another, and so on, until the process restarts, and the first operation is performed again. The circuit of Fig. 11-31 is not complete since some means of establishing the initial condition must be added. For example, some means will be required to preset one flip-flop and clear all the others. Also, the circuit may get into an illegal mode (more than one high bit) because of noise or a momentary power dip. For this reason, the circuit may also require extra logic to detect illegal modes and correct them.

nique

#### **REVIEW QUESTIONS**

23. Refer to Fig. 11-23. If the clock frequency is 10 MHz, what is the output frequency at Q<sub>D</sub>?

24. Do all of the flip-flops in Fig. 11-23 change state at the same time on the 16th negative clock edge? Why?

25. Refer to Fig. 11-26. Can this IC be used as a BCD divider and output a square wave of one-tenth the input frequency?

26. Refer to Fig. 11-27. What happens to the I/O pins when a logic 1 is applied to pin 12?

27. Refer to Fig. 11-27. Is the load function synchronous or asynchronous?

28. Refer to Fig. 11-27. Can  $Q_A$  through  $Q_D$  be tri-stated? Which device pins would be appropriate for connecting to a bus that has other device outputs connected to it?

29. Refer to Fig. 11-28. Is the load function synchronous or asynchronous?

30. Refer to Fig. 11-28. What number should the counter be preset with to use it as a modulo 8 device in the up-count mode?

31. Refer to Fig. 11-29. What will the parallel data output be if the data input is held low for four clock edges?

Refer to Fig. 11-30. Both mode control pins are high. When are the data loaded?

# 11-5 MULTIPLEXERS AND DECODERS

A digital multiplexer is a "several into one" circuit. Multiplexers are used to select data from one of several sources and output those data onto a single line. They are also called *data selectors*. The typical multiplexer IC uses select pins to determine which of the inputs will be connected to the output. For example, a four-line to one-line multiplexer will have two select pins. The binary pattern at these pins will range from 00 (input 0 is selected) to 11 (input 3 is selected).

It is possible to use a multiplexer as a parallel-toserial data converter. For example, if a 4-bit word is applied to the data inputs of a four-line to one-line device and if the select pins are clocked by a twostage counter from binary 00 to binary 11, the word will appear in serial form at the output. The first input will appear first when the counter is at 00, then the next input will appear at a count of 01, and so on.

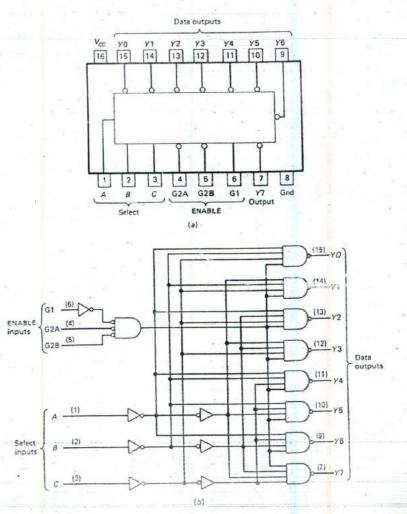

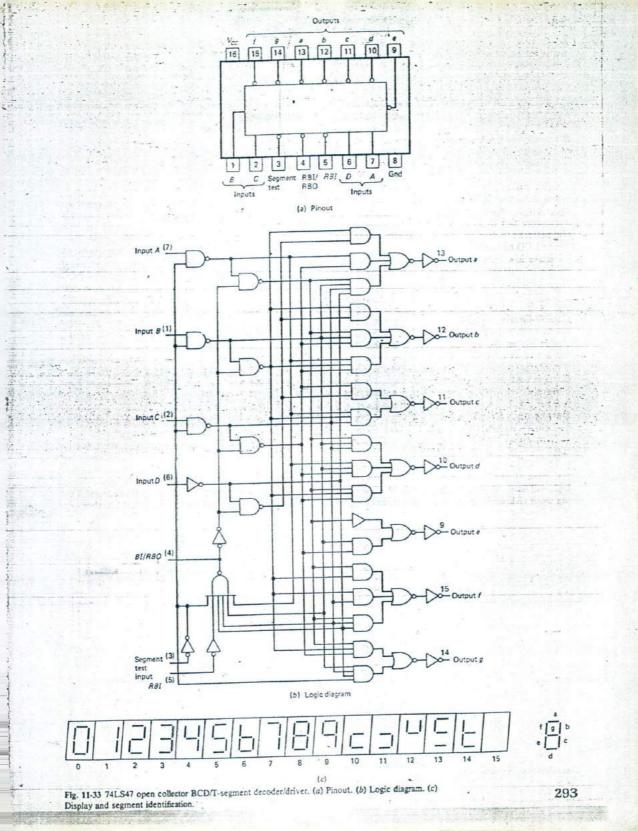

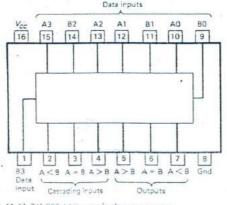

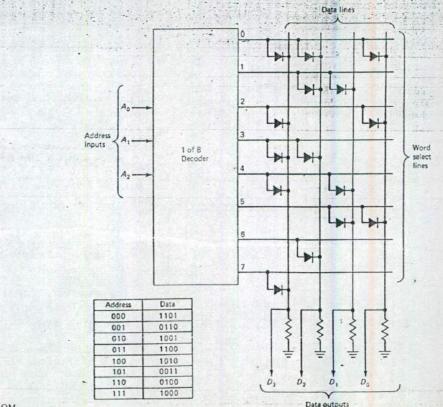

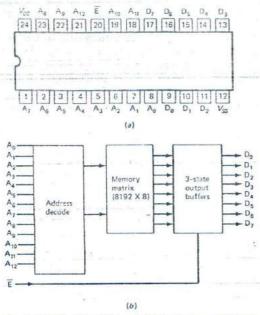

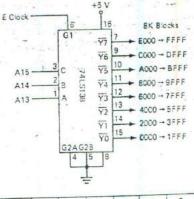

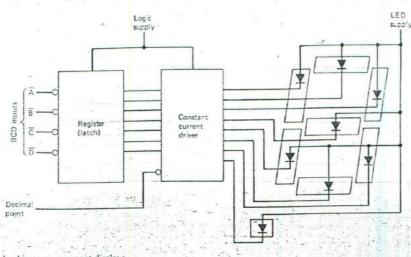

A demultiplexer represents an opposite function; it is a "one into several" logic circuit. Demultiplexers take data from a single source and distribute them to one of several output lines. They are also known as data distributors. Figure 11-32 shows the pinout and the logic diagram for a 74LS138 decoder/demultiplexer. It is used for memory decoding and datarouting applications. (Another type of decoder is shown in Fig. 11-33.) The 74LS138 distributes to one of eight output lines, depending upon the logic conditions at its three select inputs. When all three select

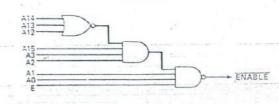

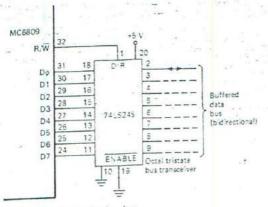

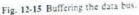

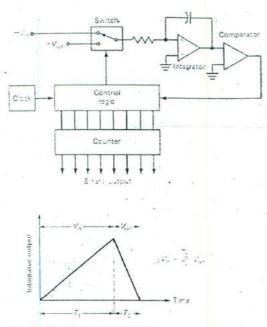

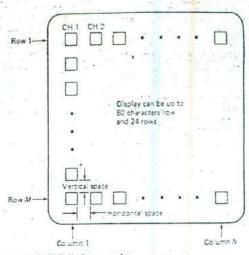

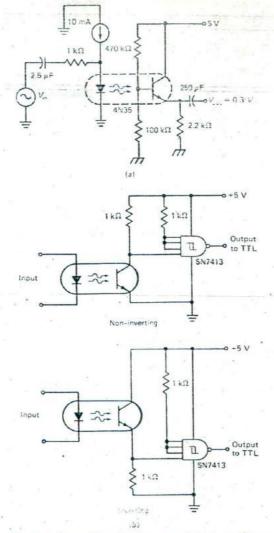

Fig. 11-32 74LS138 decoder/demultiplexer. (a) P' out. (b) Logie diagram.

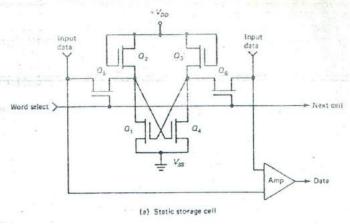

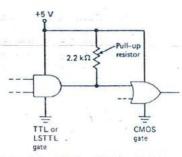

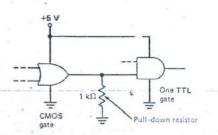

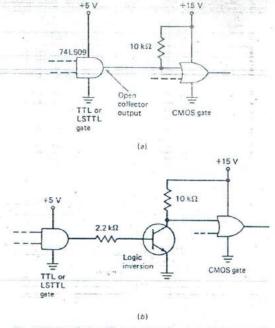

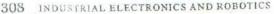

inputs are at logic 0, output Y0 is selected. If select A is high and B and C are low, output Y1 is selected. The LSB of the select word is A, and C is the MSB. Any one of the three enable inputs can be used for data input for demultiplexing operations. Two of the enable inputs are active low (G2A and G2B), and the other is active high (G1). The G1 input should be used if the data do not require inversion, and the other enable inputs should be grounded.