# IN THIS CHAPTER

| 5-1  | Instruction Codes             |

|------|-------------------------------|

| 5-2  | Computer Registers            |

| 5-3  | Computer Instructions         |

| 5-4  | Timing and Control            |

| 5-5  | Instruction Cycle             |

| 5-6  | Memory-Reference Instructions |

| 5-7  | Input-Output and Interrupt    |

| 5-8  | Complete Computer Description |

| 5-9  | Design of Basic Computer      |

| 5-10 | Design of Accumulator Lagia   |

# 5-1 Instruction Codes

In this chapter we introduce a basic computer and show how its operation can be specified with register transfer statements. The organization of the computer is defined by its internal registers, the timing and control structure, and the set of instructions that it uses. The design of the computer is then carried out in detail. Although the basic computer presented in this chapter is very small compared to commercial computers, it has the advantage of being simple enough so we can demonstrate the design process without too many complications.

The internal organization of a digital system is defined by the sequence of microoperations it performs on data stored in its registers. The generalpurpose digital computer is capable of executing various microoperations and, in addition, can be instructed as to what specific sequence of operations it must perform. The user of a computer can control the process by means of a program. A program is a set of instructions that specify the operations, operands, and the sequence by which processing has to occur. The dataprocessing task may be altered by specifying a new program with different instructions or specifying the same instructions with different data.

A computer instruction is a binary code that specifies a sequence of microoperations for the computer. Instruction codes together with data are stored in memory. The computer reads each instruction from memory and places it in a control register. The control then interprets the binary code of the instruction and proceeds to execute it by issuing a sequence of microoperations. Every computer has its own unique instruction set. The ability to store and execute instructions, the stored program concept, is the most important property of a general-purpose computer.

An instruction code is a group of bits that instruct the computer to perform a specific operation. It is usually divided into parts, each having its own particular interpretation. The most basic part of an instruction code is its operation part. The operation code of an instruction is a group of bits that define such operations as add, subtract, multiply, shift, and complement. The number of bits required for the operation code of an instruction depends on the total number of operations available in the computer. The operation code must consist of at least n bits for a given 2" (or less) distinct operations. As an illustration, consider a computer with 64 distinct operations, one of them being an ADD operation. The operation code consists of six bits, with a bit configuration 110010 assigned to the ADD operation. When this operation code is decoded in the control unit, the computer issues control signals to read an operand from memory and add the operand to a processor register.

At this point we must recognize the relationship between a computer operation and a microoperation. An operation is part of an instruction stored in computer memory. It is a binary code that tells the computer to perform a specific operation. The control unit receives the instruction from memory and interprets the operation code bits. It then issues a sequence of control signals to initiate microoperations in internal computer registers. For every operation code, the control issues a sequence of microoperations needed for the hardware implementation of the specified operation. For this reason, an operation code is sometimes called a macrooperation because it specifies a set of microoperations.

The operation part of an instruction code specifies the operation to be performed. This operation must be performed on some data stored in processor registers or in memory. An instruction code must therefore specify not only the operation but also the registers or the memory words where the operands are to be found, as well as the register or memory word where the result is to be stored. Memory words can be specified in instruction codes by their address. Processor registers can be specified by assigning to the instruction another binary code of k bits that specifies one of  $2^k$  registers. There are many variations for arranging the binary code of instructions, and each computer has its own particular instruction code format. Instruction code formats are con-

instruction code

operation code

ceived by computer designers who specify the architecture of the computer. In this chapter we choose a particular instruction code to explain the basic organization and design of digital computers.

# Stored Program Organization

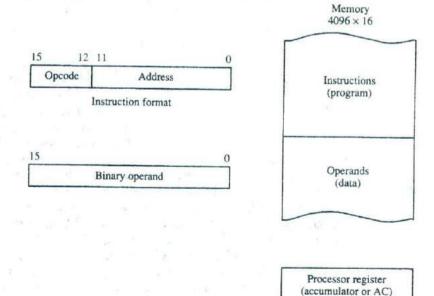

The simplest way to organize a computer is to have one processor register and an instruction code format with two parts. The first part specifies the operation to be performed and the second specifies an address. The memory address tells the control where to find an operand in memory. This operand is read from memory and used as the data to be operated on together with the data stored in the processor register.

Figure 5-1 depicts this type of organization. Instructions are stored in one section of memory and data in another. For a memory unit with 4096 words we need 12 bits to specify an address since  $2^{12} = 4096$ . If we store each instruction code in one 16-bit memory word, we have available four bits for the operation code (abbreviated opcode) to specify one out of 16 possible operations, and 12 bits to specify the address of an operand. The control reads a 16-bit instruction from the program portion of memory. It uses the 12-bit address part of the instruction to read a 16-bit operand from the data portion of memory. It then executes the operation specified by the operation code.

opcode

accumulator (AC)

Computers that have a single-processor register usually assign to it the name accumulator and label it AC. The operation is performed with the memory operand and the content of AC.

If an operation in an instruction code does not need an operand from memory, the rest of the bits in the instruction can be used for other purposes. For example, operations such as clear AC, complement AC, and increment AC operate on data stored in the AC register. They do not need an operand from memory. For these types of operations, the second part of the instruction code (bits 0 through 11) is not needed for specifying a memory address and can be used to specify other operations for the computer.

### Indirect Address

It is sometimes convenient to use the address bits of an instruction code not as an address but as the actual operand. When the second part of an instruction code specifies an operand, the instruction is said to have an immediate operand. When the second part specifies the address of an operand, the instruction is said to have a direct address. This is in contrast to a third possibility called indirect address, where the bits in the second part of the instruction designate an address of a memory word in which the address of the operand is found. One bit of the instruction code can be used to distinguish between a direct and an indirect address.

As an illustration of this configuration, consider the instruction code format shown in Fig. 5-2(a). It consists of a 3-bit operation code, a 12-bit address, and an indirect address mode bit designated by I. The mode bit is 0 for a direct address and 1 for an indirect address. A direct address instruction is shown in Fig. 5-2(b). It is placed in address 22 in memory. The I bit is 0, so the instruction is recognized as a direct address instruction. The opcode specifies an ADD instruction, and the address part is the binary equivalent of 457. The control finds the operand in memory at address 457 and adds it to the content of AC. The instruction in address 35 shown in Fig. 5-2(c) has a mode bit I = 1. Therefore, it is recognized as an indirect address instruction. The address part is the binary equivalent of 300. The control goes to address 300 to find the address of the operand. The address of the operand in this case is 1350. The operand found in address 1350 is then added to the content of AC. The indirect address instruction needs two references to memory to fetch an operand. The first reference is needed to read the address of the operand; the second is for the operand itself. We define the effective address to be the address of the operand in a computation-type instruction or the target address in a branch-type instruction. Thus the effective address in the instruction of Fig. 5-2(b) is 457 and in the instruction of Fig 5-2(c) is 1350.

The direct and indirect addressing modes are used in the computer presented in this chapter. The memory word that holds the address of the operand in an indirect address instruction is used as a pointer to an array of

immediate instruction

effective address

#### SECTION 5-2 Computer Registers

Figure 5-2 Demonstration of direct and indirect address.

data. The pointer could be placed in a processor register instead of memory as done in commercial computers.

#### **Computer Registers** 5-2

Computer instructions are normally stored in consecutive memory locations and are executed sequentially one at a time. The control reads an instruction from a specific address in memory and executes it. It then continues by reading the next instruction in sequence and executes it, and so on. This type of instruction sequencing needs a counter to calculate the address of the next instruction after execution of the current instruction is completed. It is also necessary to provide a register in the control unit for storing the instruction

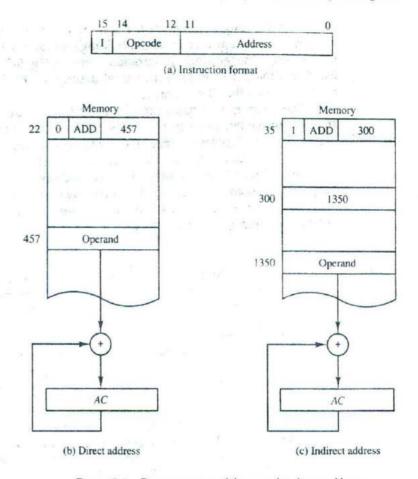

code after it is read from memory. The computer needs processor registers for manipulating data and a register for holding a memory address. These requirements dictate the register configuration shown in Fig. 5-3. The registers are also listed in Table 5-1 together with a brief description of their function and the number of bits that they contain.

The memory unit has a capacity of 4096 words and each word contains 16 bits. Twelve bits of an instruction word are needed to specify the address of an operand. This leaves three bits for the operation part of the instruction and a bit to specify a direct or indirect address. The data register (DR) holds the operand read from memory. The accumulator (AC) register is a generalpurpose processing register. The instruction read from memory is placed in the instruction register (IR). The temporary register (TR) is used for holding temporary data during the processing.

|     | gister<br>mbol | Number<br>of bits | Register name        | Function                     |

|-----|----------------|-------------------|----------------------|------------------------------|

| DI  | R              | 16                | Data register        | Holds memory operand         |

| AF  | 2              | 12                | Address register     | Holds address for memory     |

| AC  | 2              | 16                | Accumulator          | Processor register           |

| IR  |                | 16                | Instruction register | Holds instruction code       |

| PC  |                | 12                | Program counter      | Holds address of instruction |

| TR  | 1              | 16                | Temporary register   | Holds temporary data         |

| IN. | PR             | 8                 | Input register       | Holds input character        |

| 01  | JTR            | 8                 | Output register      | Holds output character       |

TABLE 5-1 List of Registers for the Basic Computer

program counter (PC)

The memory address register (AR) has 12 bits since this is the width of a memory address. The program counter (PC) also has 12 bits and it holds the address of the next instruction to be read from memory after the current instruction is executed. The PC goes through a counting sequence and causes the computer to read sequential instructions previously stored in memory. Instruction words are read and executed in sequence unless a branch instruction is encountered. A branch instruction calls for a transfer to a nonconsecutive instruction in the program. The address part of a branch instruction is transferred to PC to become the address of the next instruction. To read an instruction, the content of PC is taken as the address for memory and a memory read cycle is initiated. PC is then incremented by one, so it holds the address of the next instruction in sequence.

Two registers are used for input and output. The input register (INPR) receives an 8-bit character from an input device. The output register (OUTR) holds an 8-bit character for an output device.

Figure 5-3 Basic computer registers and memory.

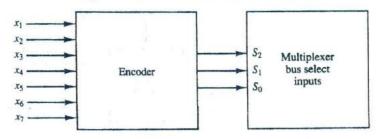

### Common Bus System

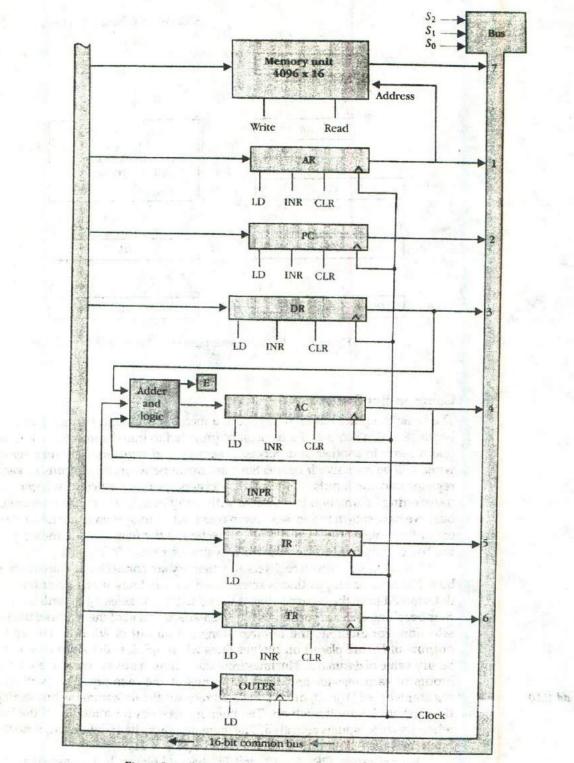

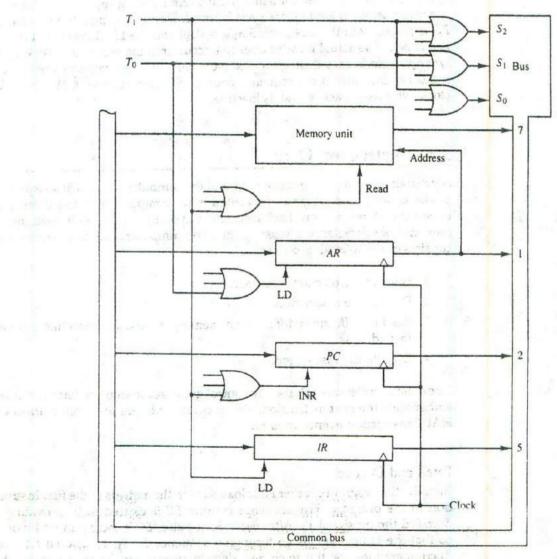

The basic computer has eight registers, a memory unit, and a control unit (to be presented in Sec. 5-4). Paths must be provided to transfer information from one register to another and between memory and registers. The number of wires will be excessive if connections are made between the outputs of each register and the inputs of the other registers. A more efficient scheme for transferring information in a system with many registers is to use a common bus. We have shown in Sec. 4-3 how to construct a bus system using multiplexers or three-state buffer gates. The connection of the registers and memory of the basic computer to a common bus system is shown in Fig. 5-4.

The outputs of seven registers and memory are connected to the common bus. The specific output that is selected for the bus lines at any given time is determined from the binary value of the selection variables  $S_2$ ,  $S_1$ , and  $S_0$ . The number along each output shows the decimal equivalent of the required binary selection. For example, the number along the output of *DR* is 3. The 16-bit outputs of *DR* are placed on the bus lines when  $S_2S_1S_0 = 011$  since this is the binary value of decimal 3. The lines from the common bus are connected to the inputs of each register and the data inputs of the memory. The particular register whose LD (load) input is enabled receives the data from the bus during the next clock pulse transition. The memory receives the contents of the bus when its write input is activated. The memory places its 16-bit output onto the bus when the read input is activated and  $S_2S_1S_0 = 111$ .

Four registers, DR, AC, IR, and TR, have 16 bits each. Two registers, AR

load (LD)

and *PC*, have 12 bits each since they hold a memory address. When the contents of *AR* or *PC* are applied to the 16-bit common bus, the four most significant bits are set to 0's. When *AR* or *PC* receive information from the bus, only the 12 least significant bits are transferred into the register.

The input register *INPR* and the output register *OUTR* have 8 bits each and communicate with the eight least significant bits in the bus. *INPR* is connected to provide information to the bus but *OUTR* can only receive information from the bus. This is because *INPR* receives a character from an input device which is then transferred to *AC*. *OUTR* receives a character from *AC* and delivers it to an output device. There is no transfer from *OUTR* to any of the other registers.

The 16 lines of the common bus receive information from six registers and the memory unit. The bus lines are connected to the inputs of six registers and the memory. Five registers have three control inputs: LD (load), INR (increment), and CLR (clear). This type of register is equivalent to a binary counter with parallel load and synchronous clear similar to the one shown in Fig. 2-11. The increment operation is achieved by enabling the count input of the counter. Two registers have only a LD input. This type of register is shown in Fig. 2-7.

The input data and output data of the memory are connected to the common bus, but the memory address is connected to *AR*. Therefore, *AR* must always be used to specify a memory address. By using a single register for the address, we eliminate the need for an address bus that would have been needed otherwise. The content of any register can be specified for the memory data input during a write operation. Similarly, any register can receive the data from memory after a read operation except *AC*.

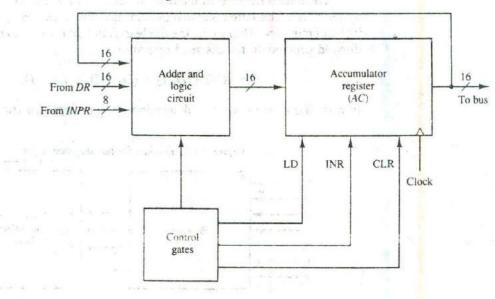

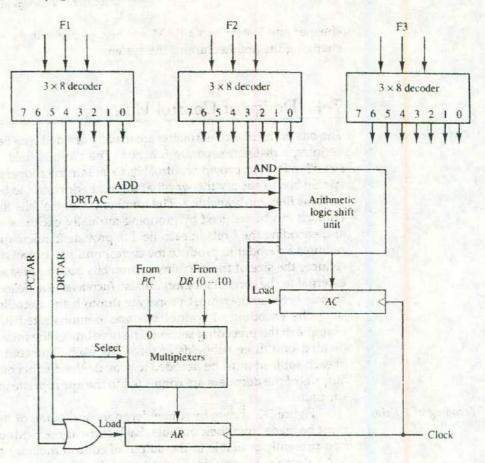

The 16 inputs of AC come from an adder and logic circuit. This circuit has three sets of inputs. One set of 16-bit inputs come from the outputs of AC. They are used to implement register microoperations such as complement AC and shift AC. Another set of 16-bit inputs come from the data register DR. The inputs from DR and AC are used for arithmetic and logic microoperations, such as add DR to AC or AND DR to AC. The result of an addition is transferred to AC and the end carry-out of the addition is transferred to flip-flop E (extended AC bit). A third set of 8-bit inputs come from the input register INPR. The operation of INPR and OUTR is explained in Sec. 5-7.

Note that the content of any register can be applied onto the bus and an operation can be performed in the adder and logic circuit during the same clock cycle. The clock transition at the end of the cycle transfers the content of the bus into the designated destination register and the output of the adder and logic circuit into AC. For example, the two microoperations

$DR \leftarrow AC$  and  $AC \leftarrow DR$

can be executed at the same time. This can be done by placing the content of AC on the bus (with  $S_2S_1S_0 = 100$ ), enabling the LD (load) input of DR, trans-

memory address

ferring the content of DR through the adder and logic circuit into AC, and enabling the LD (load) input of AC, all during the same clock cycle. The two transfers occur upon the arrival of the clock pulse transition at the end of the clock cycle.

#### 5-3 **Computer Instructions**

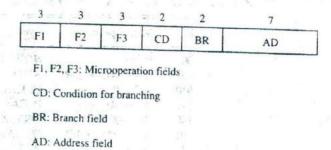

#### Instruction format

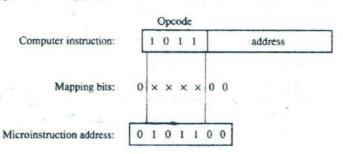

The basic computer has three instruction code formats, as shown in Fig. 5-5. Each format has 16 bits. The operation code (opcode) part of the instruction contains three bits and the meaning of the remaining 13 bits depends on the operation code encountered. A memory-reference instruction uses 12 bits to specify an address and one bit to specify the addressing mode I. I is equal to 0 for direct address and to 1 for indirect address (see Fig. 5-2). The registerreference instructions are recognized by the operation code 111 with a 0 in the leftmost bit (bit 15) of the instruction. A register-reference instruction specifies an operation on or a test of the AC register. An operand from memory is not needed; therefore, the other 12 bits are used to specify the operation or test to be executed. Similarly, an input-output instruction does not need a reference to memory and is recognized by the operation code 111 with a 1 in the leftmost bit of the instruction. The remaining 12 bits are used to specify the type of input-output operation or test performed.

The type of instruction is recognized by the computer control from the four bits in positions 12 through 15 of the instruction. If the three opcode bits in positions 12 though 14 are not equal to 111, the instruction is a memory-reference type and the bit in position 15 is taken as the addressing mode I. If the 3-bit opcode is equal to 111, control then inspects the bit in position 15. If this bit is 0, the

Figure 5-5 Basic computer instruction formats. 15 14 12 11 0 Opcode Address (Opcode = 000 through 110)(a) Memory - reference instruction 15 12 11 0 0 1 1 1 Register operation (Opcode = 111, l = 0)(b) Register - reference instruction 15 12 11 ĩ ĩ i 1/0 operation (Opcode = 111, l = 1)

(c) Input - output instruction

132

instruction is a register-reference type. If the bit is 1, the instruction is an input-output type. Note that the bit in position 15 of the instruction code is designated by the symbol *I* but is not used as a mode bit when the operation code is equal to 111.

Only three bits of the instruction are used for the operation code. It may seem that the computer is restricted to a maximum of eight distinct operations. However, since register-reference and input-output instructions use the remaining 12 bits as part of the operation code, the total number of instructions can exceed eight. In fact, the total number of instructions chosen for the basic computer is equal to 25.

The instructions for the computer are listed in Table 5-2. The symbol designation is a three-letter word and represents an abbreviation intended for

| Hexadecimal code |              | imal code    |                                      |

|------------------|--------------|--------------|--------------------------------------|

| Symbol           | <i>l</i> = 0 | <i>I</i> = 1 | Description                          |

| AND              | 0xxx         | 8xxx         | AND memory word to AC                |

| ADD              | 1xxx         | 9xxx         | Add memory word to AC                |

| LDA              | 2xxx         | Axxx         | Load memory word to AC               |

| STA              | 3xxx         | Bxxx         | Store content of AC in memory        |

| BUN              | 4xxx         | Cxxx         | Branch unconditionally               |

| BSA              | 5xxx         | Dxxx         | Branch and save return address       |

| ISZ              | 6xxx         | Exxx         | Increment and skip if zero           |

| CLA              | 78           | 00           | Clear AC                             |

| CLE              | 74           | 00           | Clear E                              |

| CMA              | 72           | 00           | Complement AC                        |

| CME              | 710          | 00           | Complement E                         |

| CIR              | 70           | 30           | Circulate right AC and E             |

| CIL              | 70-          | 40           | Circulate left AC and E              |

| INC              | 702          | 20           | Increment AC                         |

| SPA              | 701          | 10           | Skip next instruction if AC positive |

| SNA              | 700          | )8           | Skip next instruction if AC negative |

| SZA              | 700          | )4           | Skip next instruction if AC zero     |

| SZE              | 700          | )2           | Skip next instruction if $E$ is 0    |

| HLT              | 7001         |              | Halt computer                        |

| INP              | F80          | 00           | Input character to AC                |

| OUT              | F400         |              | Output character from AC             |

| SKI              | F20          | 00           | Skip on input flag                   |

| SKO              | F10          | 00           | Skip on output flag                  |

| ION              | FO           | 30           | Interrupt on                         |

| IOF              | F04          | 10           | Interrupt off                        |

TABLE 5-2 Basic Computer Instructions

#### hexadecimal code

programmers and users. The hexadecimal code is equal to the equivalent hexadecimal number of the binary code used for the instruction. By using the hexadecimal equivalent we reduced the 16 bits of an instruction code to four digits with each hexadecimal digit being equivalent to four bits. A memory-reference instruction has an address part of 12 bits. The address part is denoted by three x's and stand for the three hexadecimal digits corresponding to the 12-bit address. The last bit of the instruction is designated by the symbol *I*. When I = 0, the last four bits of an instruction have a hexadecimal digit equivalent from 0 to 6 since the last bit is 0. When I = 1, the hexadecimal digit equivalent of the last four bits of the instruction ranges from 8 to *E* since the last bit is 1.

Register-reference instructions use 16 bits to specify an operation. The leftmost four bits are always 0111, which is equivalent to hexadecimal 7. The other three hexadecimal digits give the binary equivalent of the remaining 12 bits. The input-output instructions also use all 16 bits to specify an operation. The last four bits are always 1111, equivalent to hexadecimal F.

# Instruction Set Completeness

Before investigating the operations performed by the instructions, let us discuss the type of instructions that must be included in a computer. A computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable. The set of instructions are said to be complete if the computer includes a sufficient number of instructions in each of the following categories:

- 1. Arithmetic, logical, and shift instructions

- 2. Instructions for moving information to and from memory and processor registers

- 3. Program control instructions together with instructions that check status conditions

- 4. Input and output instructions

Arithmetic, logical, and shift instructions provide computational capabilities for processing the type of data that the user may wish to employ. The bulk of the binary information in a digital computer is stored in memory, but all computations are done in processor registers. Therefore, the user must have the capability of moving information between these two units. Decisionmaking capabilities are an important aspect of digital computers. For example, two numbers can be compared, and if the first is greater than the second, it may be necessary to proceed differently than if the second is greater than the first. Program control instructions such as branch instructions are used to change the sequence in which the program is executed. Input and output instructions are needed for communication between the computer and the user. Programs and data must be transferred into memory and results of computations must be transferred back to the user.

The instructions listed in Table 5-2 constitute a minimum set that provides all the capabilities mentioned above. There is one arithmetic instruction, ADD, and two related instructions, complement AC(CMA) and increment AC(INC). With these three instructions we can add and subtract binary numbers when negative numbers are in signed-2's complement representation. The circulate instructions, CIR and CIL, can be used for arithmetic shifts as well as any other type of shifts desired. Multiplication and division can be performed using addition, subtraction, and shifting. There are three logic operations: AND, complement AC(CMA), and clear AC(CLA). The AND and complement provide a NAND operation. It can be shown that with the NAND operation it is possible to implement all the other logic operations with two variables (listed in Table 4-6). Moving information from memory to AC is accomplished with the load AC(LDA) instruction. Storing information from AC into memory is done with the store AC(STA) instruction. The branch instructions BUN, BSA, and ISZ, together with the four skip instructions, provide capabilities for program control and checking of status conditions. The input (INP) and output (OUT) instructions cause information to be transferred between the computer and external devices.

Although the set of instructions for the basic computer is complete, it is not efficient because frequently used operations are not performed rapidly. An efficient set of instructions will include such instructions as subtract, multiply, OR, and exclusive-OR. These operations must be programmed in the basic computer. The programs are presented in Chap. 6 together with other programming examples for the basic computer. By using a limited number of instructions it is possible to show the detailed logic design of the computer. A more complete set of instructions would have made the design too complex. In this way we can demonstrate the basic principles of computer organization and design without going into excessive complex details. In Chap. 8 we present a complete list of computer instructions that are included in most commercial computers.

The function of each instruction listed in Table 5-2 and the microoperations needed for their execution are presented in Secs. 5-5 through 5-7. We delay this discussion because we must first consider the control unit and understand its internal organization.

# 5-4 Timing and Control

The timing for all registers in the basic computer is controlled by a master clock generator. The clock pulses are applied to all flip-flops and registers in the system, including the flip-flops and registers in the control unit. The clock pulses do not change the state of a register unless the register is enabled by

clock pulses

a control signal. The control signals are generated in the control unit and provide control inputs for the multiplexers in the common bus, control inputs in processor registers, and microoperations for the accumulator.

hardwired control

microprogrammed control

control unit

timing signals

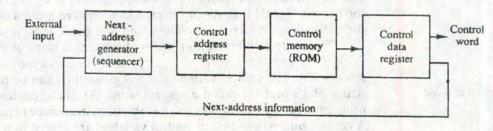

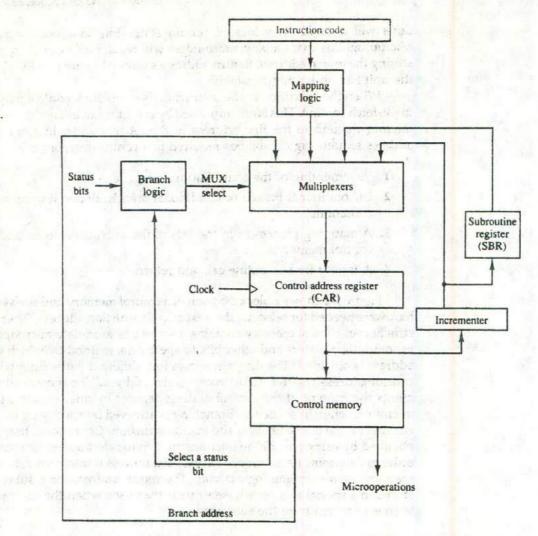

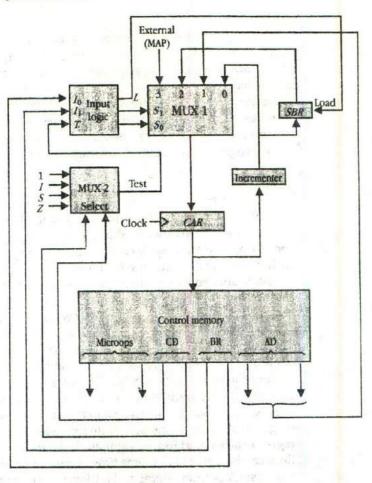

There are two major types of control organization: hardwired control and microprogrammed control. In the hardwired organization, the control logic is implemented with gates, flip-flops, decoders, and other digital circuits. It has the advantage that it can be optimized to produce a fast mode of operation. In the microprogrammed organization, the control information is stored in a control memory. The control memory is programmed to initiate the required sequence of microoperations. A hardwired control, as the name implies, requires changes in the wiring among the various components if the design has to be modified or changed. In the microprogrammed control, any required changes or modifications can be done by updating the microprogram in control memory. A hardwired control for the basic computer is presented in this section. A microprogrammed control unit for a similar computer is presented in Chap. 7.

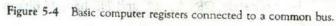

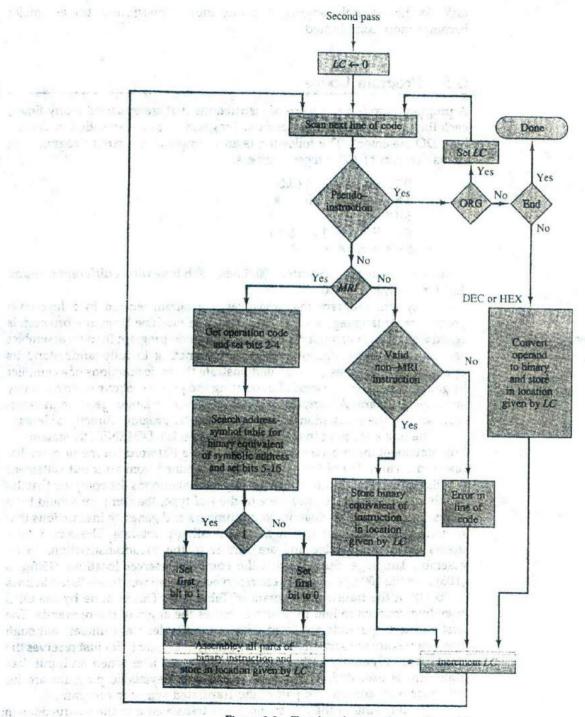

The block diagram of the control unit is shown in Fig. 5-6. It consists of two decoders, a sequence counter, and a number of control logic gates. An instruction read from memory is placed in the instruction register (*IR*). The position of this register in the common bus system is indicated in Fig. 5-4. The instruction register is shown again in Fig. 5-6, where it is divided into three parts: the *I* bit, the operation code, and bits 0 through 11. The operation code in bits 12 through 14 are decoded with a  $3 \times 8$  decoder. The eight outputs of the decoder are designated by the symbols  $D_0$  through  $D_7$ . The subscripted decimal number is equivalent to the binary value of the corresponding operation code. Bit 15 of the instruction is transferred to a flip-flop designated by the symbol *I*. Bits 0 through 11 are applied to the control logic gates. The 4-bit sequence counter can count in binary from 0 through 15. The outputs of the counter are decoded into 16 timing signals  $T_0$  through  $T_{15}$ . The internal logic of the control gates will be derived later when we consider the design of the computer in detail.

The sequence counter SC can be incremented or cleared synchronously (see the counter of Fig. 2-11). Most of the time, the counter is incremented to provide the sequence of timing signals out of the 4 × 16 decoder. Once in awhile, the counter is cleared to 0, causing the next active timing signal to be  $T_0$ . As an example, consider the case where SC is incremented to provide timing signals  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ , and  $T_4$  in sequence. At time  $T_4$ , SC is cleared to 0 if decoder output  $D_3$  is active. This is expressed symbolically by the statement

$$D_3T_4$$

: SC  $\leftarrow 0$

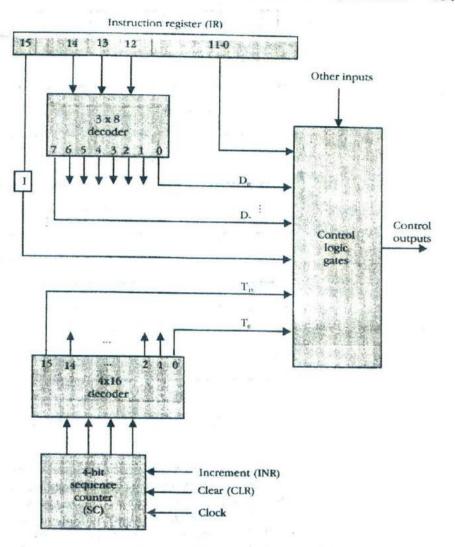

The timing diagram of Fig. 5-7 shows the time relationship of the control signals. The sequence counter SC responds to the positive transition of the clock. Initially, the CLR input of SC is active. The first positive transition of the

Figure 5-6 Control unit of basic computer.

clock clears SC to 0, which in turn activates the timing signal  $T_0$  out of the decoder.  $T_0$  is active during one clock cycle. The positive clock transition labeled  $T_0$  in the diagram will trigger only those registers whose control inputs are connected to timing signal  $T_0$ . SC is incremented with every positive clock transition, unless its CLR input is active. This produces the sequence of timing signals  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ , and so on, as shown in the diagram. (Note the relationship between the timing signal and its corresponding positive clock transition.) If SC is not cleared, the timing signals will continue with  $T_5$ ,  $T_6$ , up to  $T_{15}$  and back to  $T_0$ .

Figure 5-7 Example of control timing signals.

The last three waveforms in Fig. 5-7 show how SC is cleared when  $D_3T_4 = 1$ . Output  $D_3$  from the operation decoder becomes active at the end of timing signal  $T_2$ . When timing signal  $T_4$  becomes active, the output of the AND gate that implements the control function  $D_3T_4$  becomes active. This signal is applied to the CLR input of SC. On the next positive clock transition (the one marked  $T_4$  in the diagram) the counter is cleared to 0. This causes the timing signal  $T_0$  to become active instead of  $T_5$  that would have been active if SC were incremented instead of cleared.

A memory read or write cycle will be initiated with the rising edge of a timing signal. It will be assumed that a memory cycle time is less than the clock cycle time. According to this assumption, a memory read or write cycle initiated by a timing signal will be completed by the time the next clock goes through its positive transition. The clock transition will then be used to load the memory word into a register. This timing relationship is not valid in many computers because the memory cycle time is usually longer than the processor clock cycle. In such a case it is necessary to provide wait cycles in the processor

until the memory word is available. To facilitate the presentation, we will assume that a wait period is not necessary in the basic computer.

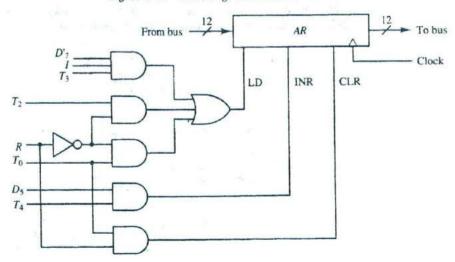

To fully comprehend the operation of the computer, it is crucial that one understands the timing relationship between the clock transition and the timing signals. For example, the register transfer statement

$$T_0: AR \leftarrow PC$$

specifies a transfer of the content of *PC* into *AR* if timing signal  $T_0$  is active.  $T_0$  is active during an entire clock cycle interval. During this time the content of *PC* is placed onto the bus (with  $S_2S_1S_0 = 010$ ) and the LD (load) input of *AR* is enabled. The actual transfer does not occur until the end of the clock cycle when the clock goes through a positive transition. This same positive clock transition increments the sequence counter *SC* from 0000 to 0001. The next clock cycle has  $T_1$  active and  $T_0$  inactive.

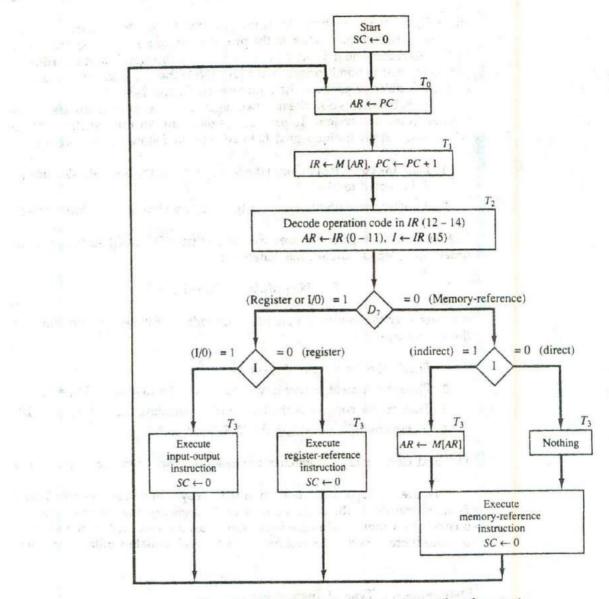

# 5-5 Instruction Cycle

A program residing in the memory unit of the computer consists of a sequence of instructions. The program is executed in the computer by going through a cycle for each instruction. Each instruction cycle in turn is subdivided into a sequence of subcycles or phases. In the basic computer each instruction cycle consists of the following phases:

- 1. Fetch an instruction from memory.

- 2. Decode the instruction.

- Read the effective address from memory if the instruction has an indirect address.

- 4. Execute the instruction.

Upon the completion of step 4, the control goes back to step 1 to fetch, decode, and execute the next instruction. This process continues indefinitely unless a HALT instruction is encountered.

## Fetch and Decode

Initially, the program counter *PC* is loaded with the address of the first instruction in the program. The sequence counter *SC* is cleared to 0, providing a decoded timing signal  $T_0$ . After each clock pulse, *SC* is incremented by one, so that the timing signals go through a sequence  $T_0$ ,  $T_1$ ,  $T_2$ , and so on. The microoperations for the fetch and decode phases can be specified by the following register transfer statements.

$T_0: AR \leftarrow PC$  $T_1: IR \leftarrow M[AR], PC \leftarrow PC + 1$  $T_2: D_0, \ldots, D_7 \leftarrow \text{Decode } IR(12-14), AR \leftarrow IR(0-11), I \leftarrow IR(15)$

Since only AR is connected to the address inputs of memory, it is necessary to transfer the address from PC to AR during the clock transition associated with timing signal  $T_0$ . The instruction read from memory is then placed in the instruction register IR with the clock transition associated with timing

Figure 5-8 Register transfers for the fetch phase.

140

## SECTION 5-5 Instruction Cycle 141

signal  $T_1$ . At the same time, *PC* is incremented by one to prepare it for the address of the next instruction in the program. At time  $T_2$ , the operation code in *IR* is decoded, the indirect bit is transferred to flip-flop *I*, and the address part of the instruction is transferred to *AR*. Note that *SC* is incremented after each clock pulse to produce the sequence  $T_0$ ,  $T_1$ , and  $T_2$ .

Figure 5-8 shows how the first two register transfer statements are implemented in the bus system. To provide the data path for the transfer of *PC* to *AR* we must apply timing signal  $T_0$  to achieve the following connection:

- 1. Place the content of *PC* onto the bus by making the bus selection inputs  $S_2S_1S_0$  equal to 010.

- 2. Transfer the content of the bus to AR by enabling the LD input of AR.

The next clock transition initiates the transfer from PC to AR since  $T_0 = 1$ . In order to implement the second statement

$$T_1: IR \leftarrow M[AR], PC \leftarrow PC + 1$$

it is necessary to use timing signal  $T_1$  to provide the following connections in the bus system.

1. Enable the read input of memory.

2. Place the content of memory onto the bus by making  $S_2S_1S_0 = 111$ .

3. Transfer the content of the bus to IR by enabling the LD input of IR.

4. Increment PC by enabling the INR input of PC.

The next clock transition initiates the read and increment operations since  $T_1 = 1$ .

Figure 5-8 duplicates a portion of the bus system and shows how  $T_0$  and  $T_1$  are connected to the control inputs of the registers, the memory, and the bus selection inputs. Multiple input OR gates are included in the diagram because there are other control functions that will initiate similar operations.

#### Determine the Type of Instruction

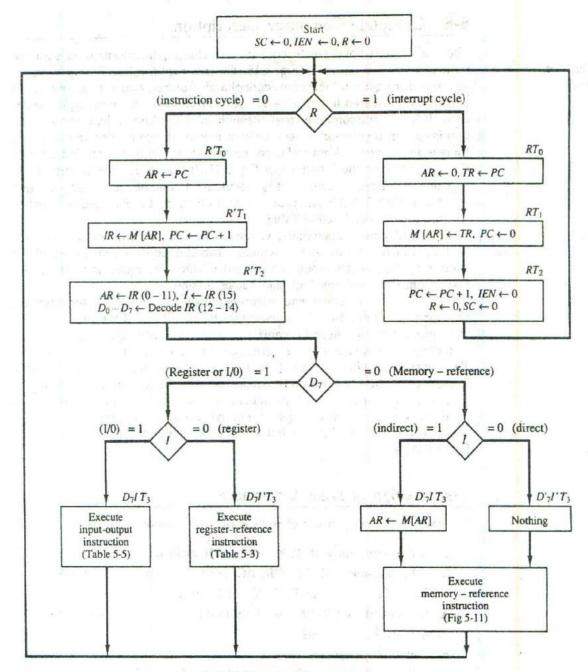

The timing signal that is active after the decoding is  $T_3$ . During time  $T_3$ , the control unit determines the type of instruction that was just read from memory. The flowchart of Fig. 5-9 presents an initial configuration for the instruction cycle and shows how the control determines the instruction type after the decoding. The three possible instruction types available in the basic computer are specified in Fig. 5-5.

Decoder output  $D_7$  is equal to 1 if the operation code is equal to binary 111. From Fig. 5-5 we determine that if  $D_7 = 1$ , the instruction must be a

Figure 5-9 Flowchart for instruction cycle (initial configuration).

register-reference or input-output type. If  $D_7 = 0$ , the operation code must be one of the other seven values 000 through 110, specifying a memory-reference instruction. Control then inspects the value of the first bit of the instruction, which is now available in flip-flop *I*. If  $D_7 = 0$  and I = 1, we have a memoryreference instruction with an indirect address. It is then necessary to read the indirect address

effective address from memory. The microoperation for the indirect address condition can be symbolized by the register transfer statement

#### $AR \leftarrow M[AR]$

Initially, *AR* holds the address part of the instruction. This address is used during the memory read operation. The word at the address given by *AR* is read from memory and placed on the common bus. The LD input of *AR* is then enabled to receive the indirect address that resided in the 12 least significant bits of the memory word.

The three instruction types are subdivided into four separate paths. The selected operation is activated with the clock transition associated with timing signal  $T_3$ . This can be symbolized as follows:

| $D_{7}' IT_{3}:$                  | $AR \leftarrow M[AR]$                    |

|-----------------------------------|------------------------------------------|

| $D_{7}^{\prime}I^{\prime}T_{3}$ : | Nothing                                  |

| $D_7 I'T_3$ :                     | Execute a register-reference instruction |

| $D_7 IT_3$ :                      | Execute an input-output instruction      |

When a memory-reference instruction with I = 0 is encountered, it is not necessary to do anything since the effective address is already in AR. However, the sequence counter SC must be incremented when  $D'_{7}T_{3} = 1$ , so that the execution of the memory-reference instruction can be continued with timing variable  $T_{4}$ . A register-reference or input-output instruction can be executed with the clock associated with timing signal  $T_{3}$ . After the instruction is executed, SC is cleared to 0 and control returns to the fetch phase with  $T_{0} = 1$ .

Note that the sequence counter SC is either incremented or cleared to 0 with every positive clock transition. We will adopt the convention that if SC is incremented, we will not write the statement  $SC \leftarrow SC + 1$ , but it will be implied that the control goes to the next timing signal in sequence. When SC is to be cleared, we will include the statement  $SC \leftarrow 0$ .

The register transfers needed for the execution of the register-reference instructions are presented in this section. The memory-reference instructions are explained in the next section. The input-output instructions are included in Sec. 5-7.

#### **Register-Reference Instructions**

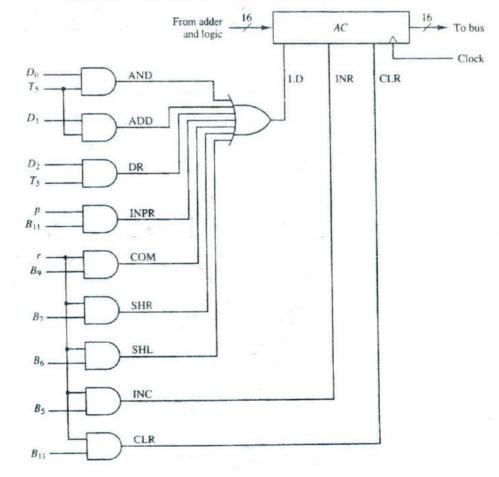

Register-reference instructions are recognized by the control when  $D_7 = 1$  and I = 0. These instructions use bits 0 through 11 of the instruction code to specify one of 12 instructions. These 12 bits are available in IR(0-11). They were also transferred to AR during time  $T_2$ .

The control functions and microoperations for the register-reference in-

structions are listed in Table 5-3. These instructions are executed with the clock transition associated with timing variable  $T_3$ . Each control function needs the Boolean relation  $D_7I'T_3$ , which we designate for convenience by the symbol r. The control function is distinguished by one of the bits in IR(0-11). By assigning the symbol  $B_i$  to bit i of IR, all control functions can be simply denoted by  $rB_i$ . For example, the instruction CLA has the hexadecimal code 7800 (see Table 5-2), which gives the binary equivalent 0111 1000 0000 0000. The first bit is a zero and is equivalent to I'. The next three bits constitute the operation code and are recognized from decoder output  $D_7$ . Bit 11 in IR is 1 and is recognized from  $B_{11}$ . The execution of a register-reference instruction is completed at time  $T_3$ . The sequence counter SC is cleared to 0 and the control goes back to fetch the next instruction with timing signal  $T_0$ .

The first seven register-reference instructions perform clear, complement, circular shift, and increment microoperations on the AC or E registers. The next four instructions cause a skip of the next instruction in sequence when a stated condition is satisfied. The skipping of the instruction is achieved by incrementing PC once again (in addition, it is being incremented during the fetch phase at time  $T_1$ ). The condition control statements must be recognized as part of the control conditions. The AC is positive when the sign bit in AC(15) = 0; it is negative when AC(15) = 1. The content of AC is zero (AC = 0) if all the flip-flops of the register are zero. The HLT instruction clears a start-stop flip-flop S and stops the sequence counter from counting. To restore the operation of the computer, the start-stop flip-flop must be set manually.

#### TABLE 5-3 Execution of Register-Reference Instructions

|      |                           | mmon to all register-reference instructions)<br>bit in $IR(0-11)$ that specifies the operation] |                  |

|------|---------------------------|-------------------------------------------------------------------------------------------------|------------------|

| M(l) | - 5/[0                    | in in m(0-11) that specifies the operation]                                                     |                  |

|      | <i>r</i> :                | $SC \leftarrow 0$                                                                               | Clear SC         |

| CLA  | <i>rB</i> <sub>11</sub> : | $AC \leftarrow 0$                                                                               | Clear AC         |

| CLE  | rB10:                     | $E \leftarrow 0$                                                                                | Clear E          |

| CMA  | $rB_9$ :                  | $AC \leftarrow \overline{AC}$                                                                   | Complement AC    |

| CME  | rB8:                      | $E \leftarrow \overline{E}$                                                                     | Complement E     |

| CIR  | rB7:                      | $AC \leftarrow \text{shr } AC, AC(15) \leftarrow E, E \leftarrow AC(0)$                         | Circulate right  |

| CIL  | rB6:                      | $AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15)$                                 | Circulate left   |

| INC  | rBs:                      | $AC \leftarrow AC + 1$                                                                          | Increment AC     |

| SPA  | $rB_4$ :                  | If $(AC(15) = 0)$ then $(PC \leftarrow PC + 1)$                                                 | Skip if positive |

| SNA  | $rB_3$ :                  | If $(AC(15) = 1)$ then $(PC \leftarrow PC + 1)$                                                 | Skip if negative |

| SZA  | $rB_2$ :                  | If $(AC = 0)$ then $PC \leftarrow PC + 1$                                                       | Skip if AC zero  |

| SZE  | rB1:                      | If $(E = 0)$ then $(PC \leftarrow PC + 1)$                                                      | Skip if $E$ zero |

| HLT  | $rB_0$ :                  | $S \leftarrow 0$ (S is a start-stop flip-flop)                                                  | Halt computer    |

# 5-6 Memory-Reference Instructions

In order to specify the microoperations needed for the execution of each instruction, it is necessary that the function that they are intended to perform be defined precisely. Looking back to Table 5-2, where the instructions are listed, we find that some instructions have an ambiguous description. This is because the explanation of an instruction in words is usually lengthy, and not enough space is available in the table for such a lengthy explanation. We will now show that the function of the memory-reference instructions can be defined precisely by means of register transfer notation.

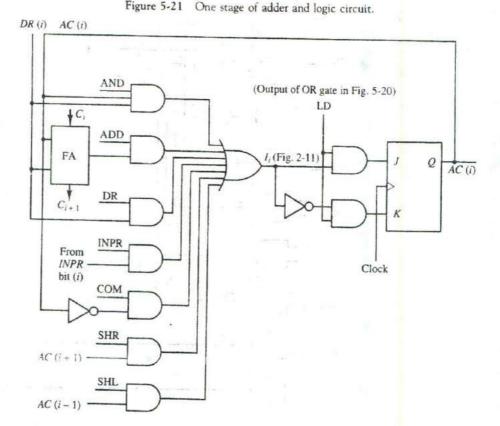

Table 5-4 lists the seven memory-reference instructions. The decoded output  $D_i$  for i = 0, 1, 2, 3, 4, 5, and 6 from the operation decoder that belongs to each instruction is included in the table. The effective address of the instruction is in the address register AR and was placed there during timing signal  $T_2$  when I = 0, or during timing signal  $T_3$  when I = 1. The execution of the memory-reference instructions starts with timing signal  $T_4$ . The symbolic description of each instruction is specified in the table in terms of register transfer notation. The actual execution of the instruction in the bus system will require a sequence of microoperations. This is because data stored in memory cannot be processed directly. The data must be read from memory to a register where they can be operated on with logic circuits. We now explain the operation of each instruction and list the control functions and microoperations needed for their execution. A flowchart that summarizes all the microoperations is presented at the end of this section.

| Symbol | Operation<br>decoder | Symbolic description                             |

|--------|----------------------|--------------------------------------------------|

| AND    | $D_0$                | $AC \leftarrow AC \land M[AR]$                   |

| ADD    | $D_1$                | $AC \leftarrow AC + M[AR], E \leftarrow C_{out}$ |

| LDA    | $D_2$                | $AC \leftarrow M[AR]$                            |

| STA    | $D_3$                | $M[AR] \leftarrow AC$                            |

| BUN    | $D_4$                | $PC \leftarrow AR$                               |

| BSA    | $D_5$                | $M[AR] \leftarrow PC$ , $PC \leftarrow AR + 1$   |

| ISZ    | $D_6$                | $M[AR] \leftarrow M[AR] + 1,$                    |

|        |                      | If $M[AR] + 1 = 0$ then $PC \leftarrow PC + 1$   |

#### TABLE 5-4 Memory-Reference Instructions

## AND to AC

This is an instruction that performs the AND logic operation on pairs of bits in AC and the memory word specified by the effective address. The result of

effective address

the operation is transferred to AC. The microoperations that execute this instruction are:

The control function for this instruction uses the operation decoder  $D_0$  since this output of the decoder is active when the instruction has an AND operation whose binary code value is 000. Two timing signals are needed to execute the instruction. The clock transition associated with timing signal  $T_4$  transfers the operand from memory into DR. The clock transition associated with the next timing signal  $T_5$  transfers to AC the result of the AND logic operation between the contents of DR and AC. The same clock transition clears SC to 0, transferring control to timing signal  $T_0$  to start a new instruction cycle.

# ADD to AC

This instruction adds the content of the memory word specified by the effective address to the value of AC. The sum is transferred into AC and the output carry  $C_{out}$  is transferred to the E (extended accumulator) flip-flop. The microoperations needed to execute this instruction are

$D_1T_4: DR \leftarrow M[AR]$  $D_1T_5: AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0$

The same two timing signals,  $T_4$  and  $T_5$ , are used again but with operation decoder  $D_1$  instead of  $D_0$ , which was used for the AND instruction. After the instruction is fetched from memory and decoded, only one output of the operation decoder will be active, and that output determines the sequence of microoperations that the control follows during the execution of a memory-reference instruction.

### LDA: Load to AC

This instruction transfers the memory word specified by the effective address to AC. The microoperations needed to execute this instruction are

$$D_2T_4: DR \leftarrow M[AR]$$

$$D_2T_5: AC \leftarrow DR, SC \leftarrow 0$$

Looking back at the bus system shown in Fig. 5-4 we note that there is no direct path from the bus into AC. The adder and logic circuit receive information from DR which can be transferred into AC. Therefore, it is necessary to read the

memory word into DR first and then transfer the content of DR into AC. The reason for not connecting the bus to the inputs of AC is the delay encountered in the adder and logic circuit. It is assumed that the time it takes to read from memory and transfer the word through the bus as well as the adder and logic circuit is more than the time of one clock cycle. By not connecting the bus to the inputs of AC we can maintain one clock cycle per microoperation.

# STA: Store AC

This instruction stores the content of *AC* into the memory word specified by the effective address. Since the output of *AC* is applied to the bus and the data input of memory is connected to the bus, we can execute this instruction with one microoperation:

$$D_3T_4$$

:  $M[AR] \leftarrow AC$ ,  $SC \leftarrow 0$

## **BUN: Branch Unconditionally**

This instruction transfers the program to the instruction specified by the effective address. Remember that *PC* holds the address of the instruction to be read from memory in the next instruction cycle. *PC* is incremented at time  $T_1$  to prepare it for the address of the next instruction in the program sequence. The BUN instruction allows the programmer to specify an instruction out of sequence and we say that the program branches (or jumps) unconditionally. The instruction is executed with one microoperation:

$$D_4T_4$$

:  $PC \leftarrow AR$ ,  $SC \leftarrow 0$

The effective address from AR is transferred through the common bus to PC. Resetting SC to 0 transfers control to  $T_0$ . The next instruction is then fetched and executed from the memory address given by the new value in PC.

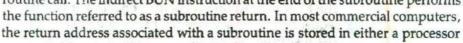

#### BSA: Branch and Save Return Address

This instruction is useful for branching to a portion of the program called a subroutine or procedure. When executed, the BSA instruction stores the address of the next instruction in sequence (which is available in PC) into a memory location specified by the effective address. The effective address plus one is then transferred to PC to serve as the address of the first instruction in the subroutine. This operation was specified in Table 5-4 with the following tegisler transfer

$$M[AR] \leftarrow PC, PC \leftarrow AR + 1$$

A numerical example that demonstrates how this instruction is used with a subroutine is shown in Fig. 5-10. The BSA instruction is assumed to be in memory at address 20. The I bit is 0 and the address part of the instruction has the binary equivalent of 135. After the fetch and decode phases, PC contains 21, which is the address of the next instruction in the program (referred to as the return address). AR holds the effective address 135. This is shown in part (a) of the figure. The BSA instruction performs the following numerical operation:

$$M[135] \leftarrow 21, PC \leftarrow 135 + 1 = 136$$

The result of this operation is shown in part (b) of the figure. The return address 21 is stored in memory location 135 and control continues with the subroutine program starting from address 136. The return to the original program (at address 21) is accomplished by means of an indirect BUN instruction placed at the end of the subroutine. When this instruction is executed, control goes to the indirect phase to read the effective address at location 135, where it finds the previously saved address 21. When the BUN instruction is executed, the effective address 21 is transferred to PC. The next instruction cycle finds PC with the value 21, so control continues to execute the instruction at the return address.

The BSA instruction performs the function usually referred to as a subroutine call. The indirect BUN instruction at the end of the subroutine performs

Figure 5-10 Example of BSA instruction execution.

(a) Memory, PC, and AR at time T<sub>4</sub>

(b) Memory and PC after execution

return address

subroutine call

#### SECTION 5-6 Memory-Reference Instructions 149

register or in a portion of memory called a stack. This is discussed in more detail in Sec. 8-7.

It is not possible to perform the operation of the BSA instruction in one clock cycle when we use the bus system of the basic computer. To use the memory and the bus properly, the BSA instruction must be executed with a sequence of two microoperations:

$D_5T_4$ :  $M[AR] \leftarrow PC$ ,  $AR \leftarrow AR + 1$  $D_5T_5$ :  $PC \leftarrow AR$ ,  $SC \leftarrow 0$

Timing signal  $T_4$  initiates a memory write operation, places the content of *PC* onto the bus, and enables the INR input of *AR*. The memory write operation is completed and *AR* is incremented by the time the next clock transition occurs. The bus is used at  $T_5$  to transfer the content of *AR* to *PC*.

#### ISZ: Increment and Skip if Zero

This instruction increments the word specified by the effective address, and if the incremented value is equal to 0, *PC* is incremented by 1. The programmer usually stores a negative number (in 2's complement) in the memory word. As this negative number is repeatedly incremented by one, it eventually reaches the value of zero. At that time *PC* is incremented by one in order to skip the next instruction in the program.

Since it is not possible to increment a word inside the memory, it is necessary to read the word into *DR*, increment *DR*, and store the word back into memory. This is done with the following sequence of microoperations:

#### **Control Flowchart**

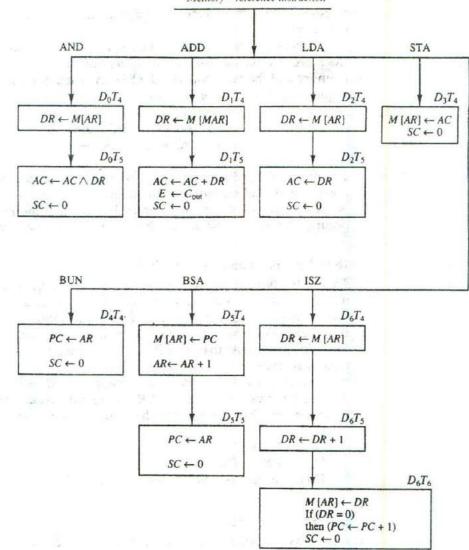

A flowchart showing all microoperations for the execution of the seven memory-reference instructions is shown in Fig. 5-11. The control functions are indicated on top of each box. The microoperations that are performed during time  $T_4$ ,  $T_5$ , or  $T_6$  depend on the operation code value. This is indicated in the flowchart by six different paths, one of which the control takes after the instruction is decoded. The sequence counter *SC* is cleared to 0 with the last timing signal in each case. This causes a transfer of control to timing signal  $T_0$ to start the next instruction cycle

Note that we need only seven timing signals to execute the longest instruction (ISZ). The computer can be designed with a 3-bit sequence counter. The reason for using a 4-bit counter for SC is to provide additional timing signals for other instructions that are presented in the problems section.

Memory - reference instruction

#### Input-Output and Interrupt 5-7

A computer can serve no useful purpose unless it communicates with the external environment. Instructions and data stored in memory must come from some input device. Computational results must be transmitted to the user through some output device. Commercial computers include many types of input and output devices. To demonstrate the most basic requirements for input and output communication, we will use as an illustration a terminal unit with a keyboard and printer. Input-output organization is discussed further in Chap. 11.

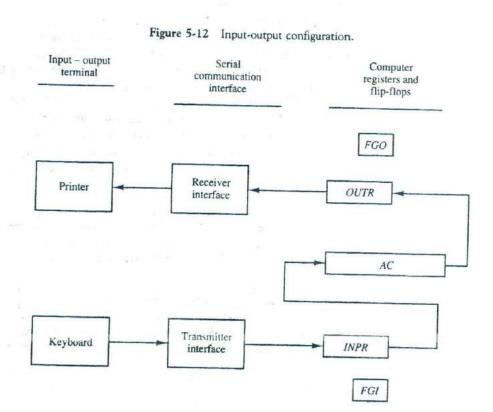

# Input-Output Configuration

The terminal sends and receives serial information. Each quantity of information has eight bits of an alphanumeric code. The serial information from the keyboard is shifted into the input register *INPR*. The serial information for the printer is stored in the output register *OUTR*. These two registers communicate with a communication interface serially and with the *AC* in parallel. The input–output configuration is shown in Fig. 5-12. The transmitter interface receives serial information from the keyboard and transmits it to *INPR*. The receiver interface receives information from *OUTR* and sends it to the printer serially. The operation of the serial communication interface is explained in Sec. 11-3. The input register *INPR* consists of eight bits and holds an alphanumeric

input information. The 1-bit input flag FGI is a control flip-flop. The flag bit is

input register

set to 1 when new information is available in the input device and is cleared to 0 when the information is accepted by the computer. The flag is needed to synchronize the timing rate difference between the input device and the computer. The process of information transfer is as follows. Initially, the input flag *FGI* is cleared to 0. When a key is struck in the keyboard, an 8-bit alphanumeric code is shifted into *INPR* and the input flag *FGI* is set to 1. As long as the flag is set, the information in *INPR* cannot be changed by striking another key. The computer checks the flag bit; if it is 1, the information from *INPR* is transferred in parallel into *AC* and *FGI* is cleared to 0. Once the flag is cleared, new information can be shifted into *INPR* by striking another key.

output register

The output register OUTR works similarly but the direction of information flow is reversed. Initially, the output flag FGO is set to 1. The computer checks the flag bit; if it is 1, the information from AC is transferred in parallel to OUTR and FGO is cleared to 0. The output device accepts the coded information, prints the corresponding character, and when the operation is completed, it sets FGO to 1. The computer does not load a new character into OUTR when FGO is 0 because this condition indicates that the output device is in the process of printing the character.

#### Input-Output Instructions

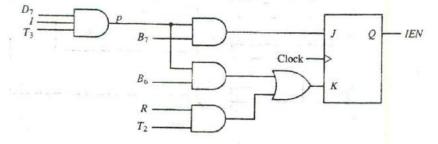

Input and output instructions are needed for transferring information to and from AC register, for checking the flag bits, and for controlling the interrupt facility. Input-output instructions have an operation code 1111 and are recognized by the control when  $D_7 = 1$  and I = 1. The remaining bits of the instruction specify the particular operation. The control functions and microoperations for the input-output instructions are listed in Table 5-5. These instructions are executed with the clock transition associated with timing signal  $T_3$ . Each control function needs a Boolean relation  $D_7IT_3$ , which we designate for convenience by the symbol p. The control function is distinguished by one of the bits in IR(6-11). By assigning the symbol  $B_i$  to bit i of IR, all control functions

TABLE 5-5 Input-Output Instructions

$D_7 I T_3 = p$  (common to all input-output instructions)  $IR(i) = B_i$  [bit in IR(6-11) that specifies the instruction]

|     | <i>p</i> : | <i>SC</i> ←0                                 | Clear SC             |

|-----|------------|----------------------------------------------|----------------------|

| INP | pB11:      | $AC(0-7) \leftarrow INPR, FGI \leftarrow 0$  | Input character      |

| OUT |            | $OUTR \leftarrow AC(0-7), FGO \leftarrow 0$  | Output character     |

| SKI | $pB_9$ :   |                                              | Skip on input flag   |

| SKO | DBa:       | If $(FGO = 1)$ then $(PC \leftarrow PC + 1)$ | Skip on output flag  |

| ION | pB7:       | $IEN \leftarrow 1$                           | Interrupt enable on  |

| IOF | pB.:       | 1EN ←0                                       | Interrupt enable off |

can be denoted by  $pB_i$  for i = 6 though 11. The sequence counter SC is cleared to 0 when  $p = D_7 IT_3 = 1$ .

The INP instruction transfers the input information from *INPR* into the eight low-order bits of *AC* and also clears the input flag to 0. The OUT instruction transfers the eight least significant bits of *AC* into the output register *OUTR* and clears the output flag to 0. The next two instructions in Table 5-5 check the status of the flags and cause a skip of the next instruction it the flag is 1. The instruction that is skipped will normally be a branch instruction to return and check the flag again. The branch instruction is not skipped if the flag is 0. If the flag is 1, the branch instruction is skipped and an input or output instruction is executed. (Examples of input and output programs are given in Sec. 6-8.) The last two instructions set and clear an interrupt enable flipflop *IEN*. The purpose of *IEN* is explained in conjunction with the interrupt operation.

#### Program Interrupt

The process of communication just described is referred to as programmed control transfer. The computer keeps checking the flag bit, and when it finds it set, it initiates an information transfer. The difference of information flow rate between the computer and that of the input-output device makes this type of transfer inefficient. To see why this is inefficient, consider a computer that can go through an instruction cycle in 1  $\mu$ s. Assume that the input-output device can transfer information at a maximum rate of 10 characters per second. This is equivalent to one character every 100,000  $\mu$ s. Two instructions are executed when the computer checks the flag bit and decides not to transfer the information. This means that at the maximum rate, the computer will check the flag 50,000 times between each transfer. The computer is wasting time while checking the flag instead of doing some other useful processing task.

An alternative to the programmed controlled procedure is to let the external device inform the computer when it is ready for the transfer. In the meantime the computer can be busy with other tasks. This type of transfer uses the interrupt facility. While the computer is running a program, it does not check the flags. However, when a flag is set, the computer is momentarily interrupted from proceeding with the current program and is informed of the fact that a flag has been set. The computer deviates momentarily from what it is doing to take care of the input or output transfer. It then returns to the current program to continue what it was doing before the interrupt.

The interrupt enable flip-flop *IEN* can be set and cleared with two instructions. When *IEN* is cleared to 0 (with the IOF instruction), the flags cannot interrupt the computer. When *IEN* is set to 1 (with the ION instruction), the computer can be interrupted. These two instructions provide the programmer with the capability of making a decision as to whether or not to use the interrupt facility.

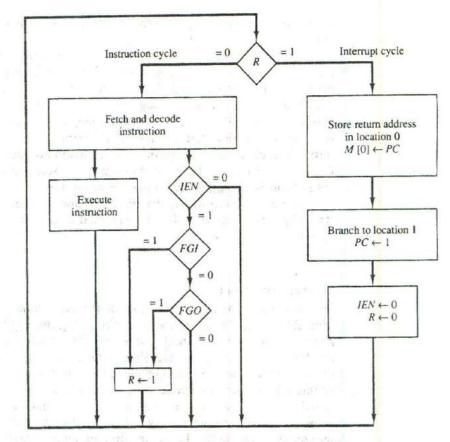

Figure 5-13 Flowchart for interrupt cycle.

The way that the interrupt is handled by the computer can be explained by means of the flowchart of Fig. 5-13. An interrupt flip-flop R is included in the computer. When R = 0, the computer goes through an instruction cycle. During the execute phase of the instruction cycle IEN is checked by the control. If it is 0, it indicates that the programmer does not want to use the interrupt, so control continues with the next instruction cycle. If IEN is 1, control checks the flag bits. If both flags are 0, it indicates that neither the input nor the output registers are ready for transfer of information. In this case, control continues with the next instruction cycle. If either flag is set to 1 while IEN = 1, flip-flop R is set to 1. At the end of the execute phase, control checks the value of R, and if it is equal to 1, it goes to an interrupt cycle instead of an instruction cycle.

interrupt cycle

The interrupt cycle is a hardware implementation of a branch and save return address operation. The return address available in PC is stored in a specific location where it can be found later when the program returns to the instruction at which it was interrupted. This location may be a processor

register, a memory stack, or a specific memory location. Here we choose the memory location at address 0 as the place for storing the return address. Control then inserts address 1 into *PC* and clears *IEN* and *R* so that no more interruptions can occur until the interrupt request from the flag has been serviced.

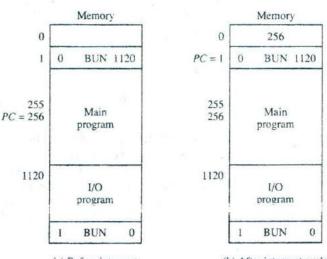

An example that shows what happens during the interrupt cycle is shown in Fig. 5-14. Suppose that an interrupt occurs and R is set to 1 while the control is executing the instruction at address 255. At this time, the return address 256 is in *PC*. The programmer has previously placed an input-output service program in memory starting from address 1120 and a BUN 1120 instruction at address 1. This is shown in Fig. 5-14(a).

When control reaches timing signal  $T_0$  and finds that R = 1, it proceeds with the interrupt cycle. The content of *PC* (256) is stored in memory location 0, *PC* is set to 1, and *R* is cleared to 0. At the beginning of the next instruction cycle, the instruction that is read from memory is in address 1 since this is the content of *PC*. The branch instruction at address 1 causes the program to transfer to the input–output service program at address 1120. This program checks the flags, determines which flag is set, and then transfers the required input or output information. Once this is done, the instruction ION is executed to set *IEN* to 1 (to enable further interrupts), and the program returns to the location where it was interrupted. This is shown in Fig. 5-14(b).

The instruction that returns the computer to the original place in the main program is a branch indirect instruction with an address part of 0. This instruction is placed at the end of the I/O service program. After this instruction is

Figure 5-14 Demonstration of the interrupt cycle.

(a) Before interrupt

(b) After interrupt cycle

read from memory during the fetch phase, control goes to the indirect phase (because I = 1) to read the effective address. The effective address is in location 0 and is the return address that was stored there during the previous interrupt cycle. The execution of the indirect BUN instruction results in placing into *PC* the return address from location 0.

#### Interrupt Cycle

We are now ready to list the register transfer statements for the interrupt cycle. The interrupt cycle is initiated after the last execute phase if the interrupt flip-flop R is equal to 1. This flip-flop is set to 1 if IEN = 1 and either *FGI* or *FGO* are equal to 1. This can happen with any clock transition except when timing signals  $T_0$ ,  $T_1$ , or  $T_2$  are active. The condition for setting flip-flop R to 1 can be expressed with the following register transfer statement:

#### $T'_0T'_1T'_2(IEN)(FGI + FGO): R \leftarrow 1$

The symbol + between *FGI* and *FGO* in the control function designates a logic OR operation. This is ANDed with *IEN* and  $T'_0T'_1T'_2$ .

modified fetch phase

We now modify the fetch and decode phases of the instruction cycle. Instead of using only timing signals  $T_0$ ,  $T_1$ , and  $T_2$  (as shown in Fig. 5-9) we will AND the three timing signals with R' so that the fetch and decode phases will be recognized from the three control functions  $R'T_0$ ,  $R'T_1$ , and  $R'T_2$ . The reason for this is that after the instruction is executed and SC is cleared to 0, the control will go through a fetch phase only if R = 0. Otherwise, if R = 1, the control will go through an interrupt cycle. The interrupt cycle stores the return address (available in *PC*) into memory location 0, branches to memory location 1, and clears *IEN*, *R*, and SC to 0. This can be done with the following sequence of microoperations:

During the first timing signal AR is cleared to 0, and the content of PC is transferred to the temporary register TR. With the second timing signal, the return address is stored in memory at location 0 and PC is cleared to 0. The third timing signal increments PC to 1, clears IEN and R, and control goes back to  $T_0$  by clearing SC to 0. The beginning of the next instruction cycle has the condition  $R'T_0$  and the content of PC is equal to 1. The control then goes through an instruction cycle that fetches and executes the BUN instruction in location 1.

# 5-8 Complete Computer Description

flowchart for basic computer

The final flowchart of the instruction cycle, including the interrupt cycle for the basic computer, is shown in Fig. 5-15. The interrupt flip-flop R may be set at any time during the indirect or execute phases. Control returns to timing signal  $T_0$  after SC is cleared to 0. If R = 1, the computer goes through an interrupt cycle. If R = 0, the computer goes through an instruction cycle. If the instruction is one of the memory-reference instructions, the computer first checks if there is an indirect address and then continues to execute the decoded instruction according to the flowchart of Fig. 5-11. If the instruction is one of the register-reference instructions, it is executed with one of the microoperations listed in Table 5-3. If it is an input-output instruction, it is executed with one of the microoperations listed in Table 5-5.

Instead of using a flowchart, we can describe the operation of the computer with a list of register transfer statements. This is done by accumulating all the control functions and microoperations in one table. The entries in the table are taken from Figs. 5-11 and 5-15, and Tables 5-3 and 5-5.

The control functions and microoperations for the entire computer are summarized in Table 5-6. The register transfer statements in this table describe in a concise form the internal organization of the basic computer. They also give all the information necessary for the design of the logic circuits of the computer. The control functions and conditional control statements listed in the table formulate the Boolean functions for the gates in the control unit. The list of microoperations specifies the type of control inputs needed for the registers and memory. A register transfer language is useful not only for describing the internal organization of a digital system but also for specifying the logic circuits needed for its design.

# 5-9 Design of Basic Computer

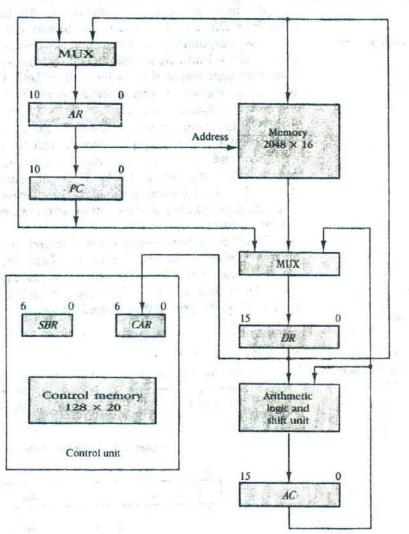

The basic computer consists of the following hardware components:

- A memory unit with 4096 words of 16 bits each

- 2. Nine registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC

- 3. Seven flip-flops: I, S, E, R, IEN, FGI, and FGO

- 4. Two decoders: a 3  $\times$  8 operation decoder and a 4  $\times$  16 timing decoder

- 5. A 16-bit common bus

- 6. Control logic gates

- 7. Adder and logic circuit connected to the input of 40

The memory unit is a standard component that can be obtained readily from a commercial source. The registers are of the type shown in Fig. 2-11 and

#### Figure 5-15 Flowchart for computer operation.

| Fetch                    | R'To:                                 | $AR \leftarrow PC$                                                                      |

|--------------------------|---------------------------------------|-----------------------------------------------------------------------------------------|

| Section 1                |                                       | $IR \leftarrow M[AR], PC \leftarrow PC + 1$                                             |

| Decode                   | $R'T_2$ :                             | $D_0, \ldots, D_7 \leftarrow \text{Decode } IR(12-14),$                                 |

| Testiment                | DUT                                   | $AR \leftarrow IR(0-11),  I \leftarrow IR(15)$                                          |

| Indirect .<br>Interrupt: | $D'_7 I T_3$ :                        | $AR \leftarrow M[AR]$                                                                   |

| ToT'T2(IEN)(FGI          | + FGO):                               | $R \leftarrow 1$                                                                        |

|                          | RTo:                                  | $AR \leftarrow 0, TR \leftarrow PC$                                                     |

|                          | $RT_1$ :                              | $M[AR] \leftarrow TR, PC \leftarrow 0$                                                  |

|                          | RT2:                                  | $PC \leftarrow PC + 1$ , $IEN \leftarrow 0$ , $R \leftarrow 0$ , $SC \leftarrow 0$      |

| Memory-reference:        |                                       |                                                                                         |

| AND                      | $D_0T_4$ :                            | $DR \leftarrow M[AR]$                                                                   |

|                          | DoTs:                                 | $AC \leftarrow AC \land DR, SC \leftarrow 0$                                            |

| ADD                      | $D_1T_4$ :                            | $DR \leftarrow M[AR]$                                                                   |

|                          | $D_1T_5$ :                            | $AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0$                          |

| LDA                      | $D_2T_4$ :                            | $DR \leftarrow M[AR]$                                                                   |

|                          | $D_2T_5$ :                            | $AC \leftarrow DR$ , $SC \leftarrow 0$                                                  |

| STA                      |                                       | $M[AR] \leftarrow AC, SC \leftarrow 0$                                                  |

| BUN                      |                                       | $PC \leftarrow AR, SC \leftarrow 0$                                                     |

| BSA                      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | $M[AR] \leftarrow PC, AR \leftarrow AR + 1$                                             |

|                          | D.T.:                                 | $PC \leftarrow AR, SC \leftarrow 0$                                                     |

| ISZ                      |                                       | $DR \leftarrow M[AR]$                                                                   |

|                          | $D_6T_5$ :                            | $DR \leftarrow DR + 1$                                                                  |

|                          | DoTo:                                 | $M[AR] \leftarrow DR$ , if $(DR = 0)$ then $(PC \leftarrow PC + 1)$ , $SC \leftarrow 0$ |

| Register-reference:      |                                       |                                                                                         |

| 0                        | $D_7 I'T_3$                           | = r (common to all register-reference instructions)                                     |