# 1

# **COMPUTER BASICS**

#### 1.0. INTRODUCTION

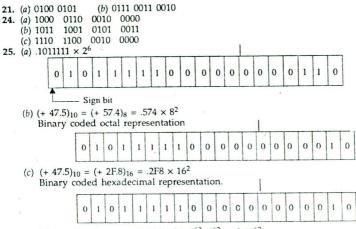

Every organisation regardless of its size or purpose is concerned with processing of facts or data for its smooth and efficient functioning. With the ever-increasing amount of data to be processed in shortest possible time, organisations felt the need for faster, cheaper and more efficient methods of processing data. To fill this need various types of automated devices were developed and foremost among them was the introduction of the electronic computer in the later half of the 20th century. Nowadays, the computers have come up in such a big way that their presence is felt in every sphere of life like education, business, research, medicine, banking, airflight, etc., to mention a few. This chapter deals with basics of computer.

## 1.1. DATA, INFORMATION AND DATA PROCESSING

The word data is the plural of datum, which means facts. The term *data* includes all facts and figures or description of an idea, object, condition or situation. Every field of activity produces data—names of employees, marks obtained by students, details of purchase made, etc.

Information is processed data that is organized and meaningful to the person receiving it. Data is thus a raw material that is transformed into information by processing. For example, the temperature the atmospheric pressure, humidity, etc., at a certain place represent data item. These data items when processed become more meaningful and predict the weather as Sunny day, Cloudy day, Rainy day, etc., which is an information.

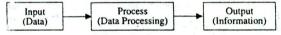

Data processing is a process that converts the data into information.

### Fig. 1.1: Information by processing data

With the development of electronic computer, the data processing is done by computer system in many ways. Thus, when we talk of data processing, it is in reference to the computer data processing.

#### 1.2. WHAT IS A COMPUTER?

(The computer is an automatic machine made up of electronic and electro-mechanical devices/that processes data under program control to generate meaningful information with speed and accuracy. Thus, the computer can be called as "Electronic Data Processor" (EDP) or an "Automatic Data Processor")

## 1.3. CHARACTERISTICS OF COMPUTERS

(a) Speech As the  $\epsilon$  imputer is electronic, its internal speed is virtually instantaneous. The speed of execution of operations by modern computer is several million operations per second. The time required for computers to execute basic operations, such as addition and subtraction, varies from a few microseconds (10<sup>-6</sup>) for small computers to nanoseconds (10<sup>-9</sup>) and for large ones even the picoseconds (10<sup>-12</sup>).

### Elements of Computer Science

(b) Automatic operation: Computers are automatic in operation. Once data and program are fed to a computer, operation of the computer is automatic in the sequence of steps defined by the program as opposed to mechanical or electronic calculator in which operator intervention is required.

(c) Storage: For automatic processing of data at a very high speed by the computer, it is necessary that both data and specified sequence of instructions to be performed be stored somewhere within the computer in advance. Modern supercomputers have several millions of words of primary memory. Large volume of data can be conveniently stored, accessed and altered.

(d) Versatility: Computers are extremely versatile, and are capable of performing almost any task, provided that the task can be reduced to a series of logical steps. The machine can be used to solve problems relating to various different fields like complex scientific problems, business problems, the problem of traffic at an airport, etc.

(e) Diligence: A computer, being a machine, does not suffer from boredom, tiredness or lack of concentration even if it has to work for long hours. Moreover, even after working for long hours, there is no loss of accuracy in its results. Thus, if a computer is to perform millions of calculations, it will perform the last calculation with the same accuracy and perfection as it will do the first one.

(f) Reliability: Today's computers are extremely reliable and results are always same as per design. There are two sources of errors: (i) Human error in program design and logic, (ii) Machine error but due to increased efficiency in error-detecting techniques, these seldom lead to false results.

### **1.4. TYPES OF COMPUTER**

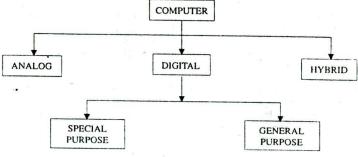

Computers are of two main types—Analog and Digital, although there are Hybric computers with features of both.

#### 1.4.1. Analog Computer

Analog is a Greek word which means establishing similarities between two quantities. The analog computers work on the principle of measurement. In analog computers the physical processes such as pressure, acceleration, power, force, viscosity, etc., are represented by electrical current or voltage signals. When physical parameter is continuously varying, its analogous electrical parameter also will be continuously varying. Such a continuously varying electrical voltage is fed as input to the analog computer which are then manipulated using various electronic modules such as inverters, comparators, summers, multipliers and integrators, etc., and the results are obtained. These results are measured and displayed by meters, oscilloscopes. The computing units of analog computers are able to respond immediately to changes which they detect in the input variables and can perform very complex arithmetical functions at high speed while the actual process in the operation. This ability to operate in real-time means that these computers have many applications in the scientific and industrial fields in stimulating various physical systems or automatically controlling industrial processes. The sequence of steps that the machine has to execute in solving the problem is permanently wired into the circuitry of the machine.

### 1.4.2. Digital Computer

Digital computers work on the principle of counting. These computer operate on discrete numbers represented by a finite sequence of digits. In other words, a digital computer accepts discrete numbers as input and after performing the desired processing (operations) on these numbers, produces discrete numbers as output.

Since digital computers work directly on the variables of the problem, rather than on some equivalent continuous variables, they are more accurate than analog computers.

#### **Computer Basics**

In analog computers, the degree of accuracy depends upon the instrument and the operator.

Depending on the flexibility in operation, digital computers are either special purpose or general purpose.

Fig. 1.2 : Types of computers

Special purpose computers (dedicated computers): They are designed to solve a restricted class of problems. They are designed and built to cater to the requirements of a particular task or application. It incorporates the instructions needed into the design of internal circuitry so that it can perform the task  $x_{i}$  a simple command quickly and efficiently. These dedicated systems may reduce the processing load on large computer.

Examples are: computers meant for process control in industry, computers meant for air traffic control, Robots, etc.

General purpose computers : They are designed to solve wide variety of problems to meet the needs of many different applications. The instructions needed to perform a particular task are not wired permanently into the internal storage. They are read from an input device and placed into the internal memory until they are needed. Examples are: payroll, sales analysis, etc.

# 1.4.3. Hybrid Computer

Hybrid computer is another type of computer which combines the features of both analog and digital computers. In many cases, a hybrid computer is an analog computer controlled by a digital computer instead of human beings. For example, in an intensive care unit, analog devices measure a patient's heart function, temperature and other vital signs. These measurements are then converted into numbers and supplied to digital components that monitor the patients vital signs and signals a nurse's station if abnormal readings are detected. Hybrid computers are used only for special applications. Main areas of their applications are aerospace and process control.

Normally, when we speak of a computer, it is understood as a digital computer. Nowadays, these are the most widely used machines. Essentially, a computer performs three functions:

- (i) It accepts data (Input);

- (ii) It processes data by performing desired arithmetic and logical operations (Processing); and

- (iii) It generates data in the desired form (Output).

Five basic units are required for performing the above three functions.

# 1.5. DIFFERENCES BETWEEN ANALOG AND DIGITAL COMPUTERS

The digital computer is basically a counting device. Hence, presence, absence, and repetition rate of the signal are the important factors, and not the amplitudes of the signal.

The analog computer is fundamentally a measuring device. It operates simultaneously on the input data, interprets their changes, and indicates the resulting variations in the response of the system. Hence, the amplitude of the signal is an important factor.

In the case of digital computer, a problem changes results in the writing of a new program; the internal structure of the machine does not get altered. In the analog computer, inter-connections between the functional units represent the details of the problem. Hence, a new problem results in a new type of inter-connections within the machine.

The precision of a digital computer can be adjusted to suit the problem to any significant figure, whereas in analog computer, it depends on the accuracy of the components and the measuring device, and is usually of the order of 0.1 per cent.

Problems, involving large amount of data in discrete form, are most readily solved on digital computer. Differential equations and problems involving integration of continuous data are more readily solved on analog computer.

### 1.6. BASIC COMPONENTS (ORGANIZATION) OF A COMPUTER SYSTEM

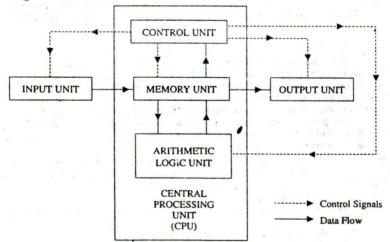

Computer system consists of five basic units:

| 1. | Input Unit :                    | Input data are fed into con puter.               |

|----|---------------------------------|--------------------------------------------------|

| 2. | Memory Unit :                   | Both program and data are stored for processing. |

| 3. | Arithmetic Logic Unit:<br>(ALU) | Data are actually processed.                     |

| 4  | Outmut Linit                    | Output data and more all dis the                 |

- 4. Output Unit : Output data are presented to the user.

- 5. Control Unit : Controls all the operations of the computer.

The control unit, together with the ALU and memory units, constitutes the Central Processing Unit (CPU).

Fig. 1.3 : Block diagram of a digital computer

### Computer Basics .

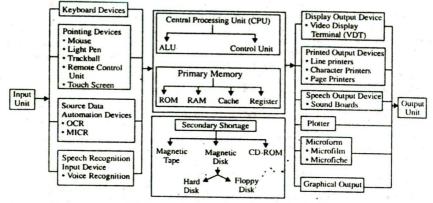

Input unit: An input unit is a device which accepts instructions and data in a form understandable to human beings, converts it into a machine readable form and transmits to the memory unit of the computer.

Some input devices require data to be stored in a medium like punched card, paper tape, magnetic tape, floppy disk, magnetic disk, etc., and data is read and transmitted by input devices like card reader, paper-tape reader, magnetic-tape reader, disk drives, etc., into a form understandable by the computer. The input can also be transmitted directly to the computer using a keyboard terminal. Currently available input devices are optical mark reader (OMR) and optical character reader (OCR), in which input is scanned by an array of photocells, converted into machine code and transmitted to the memory of the computer for processing. On identical principles bar-code readers read the information prepared in bar-code for application of computers in libraries, general stores, etc. Also, with the help of available magnetic ink character reader (MICR), information written/printed in magnetic ink is read and transmitted directly to the memory for processing. Electronic mouse, touch screens, light pens are also used as input device.

Memory unit: A computer system also has storage areas, often referred to as memory. The memory unit stores the information to be processed by the CPU. This information consists of the program as well as data. The memory can receive data, hold them and deliver them when instructed to do so. In modern computers, the internal memory consists of microelectronic semiconductor storage circuitry. The storage available in the memory is also known as main storage or primary storage. The data can be processed only when it is available in the main memory. Main memory is finite. It may be augmented by adding auxiliary or secondary storage, such as magnetic tapes, magnetic disks and drums which can store thousands of millions of characters. The information stored in the auxiliary storage can be transferred to the main memory for processing at a high speed.

Arithmetic logic unit (ALU): The ALU performs the actual processing of data including addition, subtraction, multiplication and also division. This unit also performs certain logical operations such as comparing two numbers to see one is larger than the other or if they are equal. Arithmetic or logic operation is performed by bringing the required operands into ALU. Suppose two numbers located in the main memory are to be added. They are brought into the arithmetic unit and temporarily stored in registers or in accumulators associated with this unit where the actual addition is carried out. The result is placed in one of the registers and subsequently transferred to the memory.

Control unit: The control unit directs and coordinates all activities of the computer system including the following:

- 1. Control of input/output devices.

- 2. Entry and retrieval of information from storage.

- 3. Routing of information between storage and the arithmetic logic unit.

- 4. Direction of arithmetic and logical operations.

Although control section does not process data, it acts as a central nervous system for the other data manipulating components of the computer. At the beginning of the processing the first program instruction is selected and fed into the control section from the program storage area. There it is interpreted, and from there signals are sent to other components to execute the necessary action.

Output unit: After a program is executed and the results computed, the results must be made available in a readable form. The computer system needs an output device to communicate the processed information to the user. The output device translates processed data from a machine coded form to a form that can be read and used by people. The most common types of output devices are the monitor, which resembles 'a television screen and the printer. Another common output device is the graphics plotter, which produces graphs, charts, or technical drawings on paper. An illustration is shown in Fig. 1.4.

Fig. 1.4: Basic components of a computer system

### **1.7. COMPUTER SYSTEM**

A system is composed of a set of interacting parts which operate together to achieve some objective. Since a computer is composed of a set of parts like CPU, input/output devices, storage devices integrated together to process the data under program control. The term computer system rather than the term computer is used.

### 1.7.1. Computer Hardware and Software

The data are processed by a collection of electronic circuits and other devices that make up the computer system. The physical equipment and components which one can see, touch and feel in the computer system are called hardware. Mechanical, magnetic, electrical or optical devices used in the computer system are examples of computer hardware.

Computer hardware as a machine cannot solve a given problem on its own. The physical components are to be properly instructed to work in the desired way. Sets of

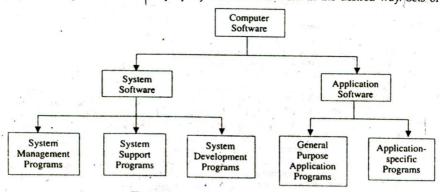

Fig. 1.5: An overview of computer software

### **Computer Basics**

programmed, instructions which enable the hardware units to perform tasks constitute a computer's software which is, in a sense, the interface between a computer hardware and its users. Software is mainly divided into two categories: (i) Application software, and (ii) System software.

Application software: It refers to the programs that the programmer's write to accomplish (i) General purpose application programs such as word processing, electronic spreadsheet, graphics, etc., and (ii) Application specific programs such as inventory control, payroll, railway reservation, etc.

System software: The system software refers to the programs written for a specific computer to aid programmers/users of that computer. It controls all processing activities and make sure that the resources and the power of the computer are used in a most efficient way. It includes (i) System management programs such as operating systems, database management systems, etc., (ii) System support programs such as system utilities, system security monitors, and (iii) System development programs like language processors, Computer Aided Software Engineering (CASE) packages, etc.

# Distinction between a Computer and an Electronic Calculator (AMIE, W '97)

A calculator only computes, whereas a computer can perform other functions which a calculator cannot. These differences are slowly decreasing with the advent of advanced programmable calculators.

The following areas distinguish a computer from a calculator:

| Electronic Calculator                                                | Computer                                                                                                |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 1. Generally non-programmable.                                       | 1. Always programmable.                                                                                 |

| 2. Contains no secondary storage.                                    | 2. Generally have some secondary storage.<br>External storage capacity is almost<br>limitless.          |

| <ol><li>No operating system/command interprete<br/>needed.</li></ol> | r 3. Existence of operating system alongwith command interpreter is essential.                          |

| 4. A small built-in display window.                                  | <ol> <li>A separate device, like a TV, enables it to<br/>display data and other information.</li> </ol> |

| 5. Does not have the capability of text processing.                  | 5. Text processing is exclusively done.                                                                 |

### **REVIEW QUESTIONS SET**

1. What are data? What is information? Explain the difference between these two terms.

- 2. Define a computer (What do you understand by data processing?)

- 3. What is a computer? Explain briefly the working principle of various types of computers?

- 4. Define the term 'hardware' and 'software'.

- 5. What is meant by the following:

- (a) Computer system (b) Peripheral devices (c) Computer configuration.

- 6. List the basic components of a computer system and explain them.

- 7. Draw the block diagram of a computer and explain briefly the functions of each unit.

(AMIE, S '96, W '97)

8. Differentiate the following:

(a) General purpose vs Special purpose computer (b) Digital vs Analog computer.

- 9. What are the major characteristics of a computer? Explain briefly each of them.

- 10. Write short notes on:

- (a) Application software, and (b) System software.

- Name the major elements and state their functions in a general purpose digital computer. With a neat sketch, indicate how these elements are connected. (AMIE, W '93)

- 12. How do you classify the digital computers according to their applications?

- How the programming languages are classified according to applications? Give salient features of each application. (AMIE, W '97)

# HISTORY, GENERATIONS AND CLASSIFICATION OF COMPUTERS

# 2.0. INTRODUCTION

This chapter deals with historical development of computers, computer generations which are characterised by hardware and software technology and the classification of computers as micro, mini, mainframe and supercomputer.

# 2.1. HISTORY OF COMPUTING

Although the abacus is not a computer, the history of computing really began with this device. It was used in China and Japan for thousands of years before Christ. The abacus is a manual device combining two fundamental concepts. First, numerical information can be represented in a physical form. Second, this information can be manipulated in the physical form to produce the required result.

Fig. 2.1: Abacus

The abacus is essentially a collection of beads strung on parallel rods fixed in a frame. (There are two portions. The beads in the upper portion count five each and those in the lower portion count one each. Arithmetic calculations are performed by manipulating those beads.

### 2.1.1. Mechanical Calculators

The first machine to add numbers mechanically was invented by Pascal, (the French mathematician and philosopher in 1643. His machine consisted mainly of a row of toothed wheels. These teeth were numbered from 0 to 9. The machine could add eight columns of numbers. It sets a milestone in the development of

Fig. 2.2: Mechanical calculator

computers. Later in the same century German mathematician Leibnitz added the facility of multiplication and division as well.

# 2,1.2. Charles Babbage-Nis Engines

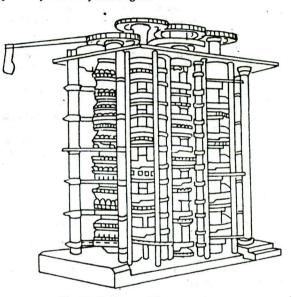

Charles Babbage, a Professor of Mathematics at Cambridge University, England, attempted in 1812 to build a difference engine, a machine that could add, subtract, multiply, divide and perform a sequence of steps automatically. Babbage called his machine a difference engine because he attempted to use it to compute mathematical tables by adding differences.

#### History, Generations and Classification of Computers

Babbage failed to get the necessary fund for his machine and in 1833 the project was dropped. Babbage was also thinking of making a analytical engine with store (memory), mill (arithmetic) and sequence of machanism (control). He did not gain necessary fund for this project even though his concepts were sound in every respect. It is generally stated that the technology in Babbage time just did not permit the development of instruments with the precision required by his analytical engine.

### 2.1.3. Punched Card Machine

In weaving, the chief problem weavers face was the control of a number of shuttles for creating designs. The whole operation was cumbersome and expensive. Jacquard devised a method. He took a card and punched holes in it wherever the shuttles had to go through. He punched different sets of holes on different cards which resulted in producing different patterns.

A major development occurred in 1886 when Herman Hollerith devised a system based on the principle of punching holes into cards, similar to Jacquard's idea. Hollerith had the idea that these holes could be sensed by a machine, a new way to handle large volume of data. Jacquard and Charles Babbage

Fig. 2.3 : Babbage's difference engine

had used punched cards and operated them by mechanical devices. The first card machine which was electrically activated was used by Hollerith to compute the statistics of the 1890 United States census. Till 1960s the punched card system was the chief mode of processing data.

#### 2.1.4. First Digital Computer

In 1937, Howard A. Aiken of Harvard University began work on the design of fully automatic calculating machine using the concepts of Babbage and punch cards in collaboration with the IBM (International Business Machine). Seven years later in January 1944 the design became a reality and was named MARK I. This was considered to be the first digital computer. MARK I could accept data from punch cards, store them in memory, make calculations by means of automatically controlled electromagnetic relays and arithmetic counters which were mechanical. It could be programmed, *i.e.*, given a set of commands to carry out certain operations. It performed arithmetic and logical operations and solved scientific problems.

# 2.1.5. First Electronic Computer

ENIAC (Electronic Numerical Integrator and Calculator): The innovation of very high speed vacuum tube, a built in device, led to the first all electronic computer in the year 1947. It contains vacuum tubes, registers, capacitors and switches and it was much faster than the MARK I.

9

### 2.1.6. First Computer to use Stored Program

EDSAC (Electronic Delayed Storage Automatic Computer): Earlier machines could be programmed but the idea of storing instructions in the computer memory was not there. Von Neumann, referred to as the father of modern computers, was the first to introduce the concept of stored program around the same time. EDSAC is the first computer to use the stored program concept and was designed and completed in 1949 at the Cambridge University, England. The program was set into the storage unit by means of paper tape. EDSAC also used vacuum tubes and was a little faster than the ENIAC.

### 2.1.7. First Commercially Produced Computer

UNIVAC I (Universal Automatic Computer): The first computer to use magnetic tape for data input and output was UNIVAC I. It was built in 1946. The first UNIVAC computer was installed at the United States Bureau of the Censor in 1951. It was the first computer to be produced commercially. It could process numeric as well as alphabetic data. Vacuum tubes were used in this system also.

After the discovery of the transistor, vacuum tubes were replaced by smaller size transistors. Many drawbacks of the vacuum tubes were eliminated with the use of transistors. With further advancement in electronics technology, transistors have been replaced by extremely superior solid state devices. The fabrication of large number of circuits on very small silicon chips has led to the reduction in the size, cost of computers and enhancement of speed.

### 2.2. COMPUTER GENERATIONS

Electronic Numerical Integrator and Calculator (ENIAC) was the first general purpose electronic digital computer and was developed in 1946. Today it has become antique as science has developed to such an extent that we have a pocket computer which is more powerful in comparison. As efficiency in terms of speed, storage capacity and reliability of computers increased with time; the size, computing time and cost decreased. This growth is divided into different generations which are characterised by hardware and software technology.

### 2.2.1. First Generation (1942-55) (The era of the vacuum tube)

The first generation of computers was marked by the use of vacuum tubes and by the use of either electrostatic tubes (CRT) or mercury delay lines for storage. Punched card and punched paper tape were used for input and output of data. These include UNIVAC I, ENIAC, EDSAC, IBM 650 and 701. On the first generation machines, programs were written in machine language, and read into the computers memory as a stored program. Disadvantages with the use of vacuum tubes are: (i) size of the computer becomes large, thereby lot of space is required for their storage and is non-portable, (ii) constant main-ditioning is required, (iii) switching time of the tubes is very high and the speed of the computer is slow.

### 2.2.2. Second Generation (1956-65)

The second generation machines were initially marked by either magnetic drum or magnetic (ferrite) core storage and later by the use of the transistor (a small piece of germanium metal suitably duped with impurities) in place of vacuum tubes. The transistor performs the same function as the vacuum tube but smaller, less expensive, generates almost no heat and requires little power. Second generation computers were substantially reduced in size, required less 'power and were more reliable. Examples are IBM 1401, Borroughs B 5000, CDC 1604.

#### History, Generations and Classification of Computers

People began to realise that the software was going to play a major role in computing. Standardized high level languages such as COBOL, FORTRAN and AIGOL were developed to take care of the rapid growth in the number of applications that were being computerised. With higher speed CPUs and the advent of magnetic tape and disk storage, operating systems were developed. Computing in real time (applications that require a response within a short period of time) was starting to become popular.

#### 2.2.3. Third Generation (1966-75)

The third generation computers are characterized by miniaturised circuits, the integration of hardware with software and an orientation of data communication and the handling of more than one operation simultaneously. The speed is faster, prices are lower, e.g., ICL 1900 series, system 4, IBM 360, Honeywell 6000. The transistors were replaced by small integrated circuits (ICs). Instead of having one transistor of its own, several transistors along with other components integrated on a single silicon chip are known as integrated circuits (ICs). These IC-based systems were more economical and powerful in all respect. The effect of increasing switching speed of transistors, the reliability, the reduction of power dissipation and size were the emergence of extremely powerful CPUs with the capacity of carrying out one million instructions per second. Time sharing became the buzzword of the third generation. The combination of hardware and software allows a central computer to serve many users at what appears to be at the same time.

In high level languages, improved FORTRAN IV was developed, COBOL 68 was standardized by the American National Standard Institute and PL/I of IBM was emerged as a powerful language.

### 2.2.4. Fourth Generation (1975 onwards)

After development of ICs, they were further integrated to form Large-scale Integration (LSI) and Very Large-Scale Integration (VLSI) and resulted in the development of microprocessors. The latest microprocessor of Intel's 8086 family, 1586 contains more than three million transistors. Microprocessor-based computers are characterized by their smaller size, lower cost, larger memory and faster speed. The computers of today are members of the fourth generation. Some of the computers which belong to this generation are PARAM, PC-AT 486, MIGBTY-FRAME 1, MACINTOSH, CRAY XMP 14, etc.

Packaged software-programs like electronic spread-sheets and data management packages that are already written, tested and able to be purchased from the shelf in retail computer stores is creating an independent software industry. Another important development is interactive graphic devices and language interfaces to graphic systems. The emergence of graphics has given a great impetus to computer-aided engineering design.

Vacuum tube (First generation)

Transistor (Second generation)

Integrated circuitry (IC) (Third generation)

Large Scale Integration (LSI) (Fourth generation)

Fig. 2.4: Electronic devices of different generations

Elements of Computer Science

| S.<br>No. | Generations                      | l<br>(1942-55)                                              | II<br>(1956-65)                                                                 | III<br>(1966-75)                                                   | IV<br>(1975 Onwards)                                                     |

|-----------|----------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------|

| 1.        | Technologies                     | Vacuum tubes:<br>acoustic<br>memories, CRT<br>memories      | Transistors, ferrite<br>cores magnetic<br>disks                                 | Integrated<br>circuits (ICs)                                       | LSI circuits and<br>VLSI circuits,<br>semiconductor<br>memories          |

| 2.        | Software                         | Machine<br>Language<br>(low-level),<br>Assembly<br>Language | COBOL, ALGOL<br>FORTRAN (high-<br>level language),<br>Batch operating<br>system | FORTRAN-IV<br>COBOL-68,<br>PL/1 Time<br>shared<br>operating system | PASCAL,<br>FORTRAN 77<br>ADA, COBOL 74                                   |

| 3.        | Number of users                  | 1                                                           | 1                                                                               | Multiple user<br>community                                         | Remote users                                                             |

| 4.        | Nature of inputs                 | Torn tapes                                                  | Punched cards,<br>Magnetic tape,<br>Disks, etc.                                 | Cards, Magnetic<br>tapes, Disks                                    | VDUs, Floppies,<br>Optical Disks                                         |

| 5.        | Nature of<br>Processing          | Serial                                                      | Serial                                                                          | Serial                                                             | Serial/Parallel                                                          |

| 6.        | Execution<br>Speed<br>measure    | Milliseconds<br>(thousandth of<br>a second)                 | Microseconds<br>(Millionth of a<br>second)                                      | Nanoseconds<br>(billionth of a<br>second)                          | Picoseconds .<br>(trillionth of a second)                                |

| 7.        | Represen-<br>tative<br>Computers | UNIVAC I, IBM<br>650, ENIAC                                 | IBM 7094<br>CDC 1604                                                            | IBM 360<br>DECPOP-8/11<br>Burroughs<br>6700/7700<br>CDC 6000/7000  | IBM 370<br>CRAY XMP 14<br>PC-AT 486<br>ETA-10                            |

| 8.        | Applications                     | Mostly scientific,<br>simple business<br>application        | Extensive business<br>application,<br>Scientific research                       | Database<br>management<br>systems, on line<br>system               | Personal<br>computer,<br>Integrated<br>CAD/CAM,<br>Distributed<br>system |

Table 2.1: Comparison of Computer Generations

### 2.2.5. Fifth Generation

The fifth generation computers are under development. Japan and USA have undertaken to design and develop such computers. It appears that the fifth generation computers will have at least three important characteristics: (i) mega-chip memories, (ii) the ability to extensive use of parallel processing, and (iii) artificial intelligence. The design approach of the CPU of these computers will be conceptually different from that of the earlier four generations of computers of Von Neuman architecture in which processor executes simple instructions in sequence. In new design, processing units may not be centralized but distributed in the computer system. All data may not be stored in the main memory. The data may flow through the processing units activating each of them as needed. These computers will be knowledge-based and will be used for Information Management, Natural Language Processing, Speech, Character and Image Recognition and such other artificial intelligence applications.

# 2.3. CLASSIFICATION OF COMPUTERS

Based on the size of primary storage, the capabilities in terms of processing speed, the

### History, Generations and Classification of Computers

range of applications and the number and type of peripheral devices, the computers may be divided into following different classes:

- 1. Micro Computers

- 2. Mini Computers

- 3. Mainframe Computers

- 4. Supercomputers

### 2.3.1. Micro Computers

It is the smallest and cheapest category of digital computers. It is called micro because of its miniature size and using of a microprocessor. A micro computer consists of a main microprocessor (a CPU on a chip), several support microprocessors and associated control, primary storage and a variety of input/output and secondary storage devices.

Computers of this category are supported by single user operating system. This category is further sub-divided into (a) Home computers, and (b) Personal computers.

(a) Home computers are used for entertainment, education, training and for home management. The word length of these computers is 8 bit. They have a keyboard integrated with the CPU in one box which is interfaced with an ordinary colour television to act as the VDU and an audio cassette recorder to act as the secondary storage device. Examples are TRS-80, UNICORN.

(b) Personal computers (PCs) are meant for professionals, small business units and for office automation systems. The following are three categories of PC:

- (i) PC-This uses 8086 or 8088 microprocessor.

- (ii) PC-XT—This is a PC with an extended technology. It uses 8088 microprocessor and a fixed inbuilt disk known as hard disk. PC and PC-XT are single user system.

- (iii) PC-AT—This is a PC with an advanced technology and it uses 80286, 80386, 80486 or 1586 microprocessor and hard disk drive. Its CPU is powerful than PC-XT. Four terminals can be connected to make it multiuser. The following are the major features of these computers:

| CPU speed                   | : | 500 KIPS                                                                                                                                          |

|-----------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Word length                 | : | 8 to 16/32 bits                                                                                                                                   |

| Storage capacity ·          | : | 256 KB to 16 MB                                                                                                                                   |

| Secondary storage           | : | Floppy disk, hard disk, magnetic tape, optical disk                                                                                               |

| Input/Output devices        | : | Keyboard, electronic mouse, light pen, optical<br>and voice input devices, video display monitors<br>and printers are the most widely used output |

|                             |   | devices                                                                                                                                           |

| Major areas of applications | : | Word processing, database management,<br>accounting and financial analysis, engineering<br>and scientific applications                            |

| Commonly used machines      | : | IBM-PC, Apple, BBC Micro, Radio Shak TRS-80, etc.                                                                                                 |

### 2.3.2. Mini Computers

The mini computers are slightly bigger in size, memory and speed compared to microcomputers. Mini computers are multi-user systems. This means that more than one user can use the computer system at the same time.

The major features of these computer are given below:

•

CPU speed

### 10 to 30 MIPS

Elements of Computer Science

| Word length                 | : | 16 to 32 bits                                                                                      |

|-----------------------------|---|----------------------------------------------------------------------------------------------------|

| Storage capacity            | : | 8 MB to 96 MB                                                                                      |

| Input/Output devices        | ÷ | Winchester hard disk, magnetic tapes, high speed line printers, plotters, etc.                     |

| Major areas of applications |   | Process control in industries, high-performance<br>workstations with graphics input/output display |

| Commonly used machines      | : | engineering and scientific research<br>PDP 11, HP 2000, IBM SYS/3, etc.                            |

## 2.3.3. Mainframe Computers

Mainframe computers are larger than micros and minis, and usually have one or more central processors. Normally, mainframe manufacturers produce families of computers with models ranging in size from small to very large. Most models in family are compatible, *i.e.*, programs written for one model can be run on other. The major features of these computers are given below:

| CPU speed :                   | 30 to 100 MIPS                                                                                                                   |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Word length :                 | 32 to 64 bits                                                                                                                    |

| Storage capacity              | 8 MB to 256 MB                                                                                                                   |

| Input/Output devices :        | 1000 MB to 10 GB hard disks, high speed magnetic tapes, fast line printer, laser printer, mini computers as front end processors |

| Major areas of applications : | Research organisations, large industries and govern-<br>ment organisations, large-scale on line reservation<br>systems           |

| Commonly used machines :      | IBM 4300 series, HP 9000 model, CYBER-170,<br>BORROUGHS 7800                                                                     |

|                               |                                                                                                                                  |

# 2.3.4. Super Computers

Supercomputers are very big in memory size, perform billion of operations per second. The high speed in these computers is due to use of a number of processors working in parallel and high storage densities are obtained by using magnetic bubble memories.

The main features of these computers are given below:

| CPU speed :                   | 400 MIPS to 10,000 MIPS                                                                                                                  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Word length                   | 64 bits to 96 bits                                                                                                                       |

| Storage capacity :            | 256 MB and more                                                                                                                          |

| Input/Output devices :        | Very high speed 1000 MB hard disks, very high<br>speed tapes, large size computers as front end<br>processors, high speed laser printers |

| Major areas of applications : | Defence research, weather forecasting, space<br>research, etc.                                                                           |

| Commonly used machines:       | CRAY XMP-14, GDC Cyber 205 family,<br>CRAY YMP series, ETA 10, etc.                                                                      |

|                               |                                                                                                                                          |

### **REVIEW QUESTIONS SET**

1. What do the following names stand for : ENIAC, EDSAC, UNIVAC.

What is meant by the term generation in computer technology? How many computer generations are there till now? Explain each generation briefly.

3. Explain the disadvantages of using vacuum tubes. How have they been overcome?

4. How are third generation computers superior to second generation computers?

# History, Generations and Classification of Computers

- 5. How do you differentiate between: (a) Micro

- (b) Mini

- (c) Mainframe computer? Write their field of applications. ٠

- 6. What are the characteristics of a microcomputer?

- 7. Write short notes on :

- (a) Mini Computers

- (b) Mainframe Computers

- (c) Supercomputers

- 8. Write a short note on Personal Computer.

# NUMBER SYSTEMS

# 3.0. INTRODUCTION

The knowledge of number systems is essential because the design and organisation of a computer is dependent upon the number systems. The binary system has proven the most natural and efficient system for computer use. This chapter describes number systems used in computer technology.

# 3.1. NUMBER SYSTEMS

A number system consists of a set of symbols and rules for representing any number. There are mainly two types of number systems: (i) Non-positional systems, and (ii) Positional systems.

# 3.1.1. Non-positional Systems

In the non-positional systems, the characters used are I for 1, II for 2, etc., and are of positional invariant, *i.e.*, each symbol represents the same value regardless of its position in the number. Since it is very difficult to perform arithmetic calculations with such a number system, positional number systems were developed.

### 3.1.2. Positional Systems

A number system with a specified number as the base is called a positional number system. Any positional number system requires only a finite number of symbols, called the digits, of the system to represent arbitrarily large number. The total number of digits in the system is called its base or radix. The value of each digit in such a number is determined by

- (a) the digit itself,

- (b) the position of the digit in the number, and

(c) the base of the number system.

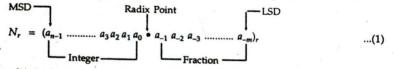

In general, the positional and polynomial form of a number in fixed point form is

where the radix (or base) r is the total number of digits in the number system and a is a digit in the set defined for radix r. Here the radix point separates n integer digits on the left from m fraction digits on the right. Notice that  $a_{n-1}$  is the most significant (highest order) digit, called MSD and that  $a_{-m}$  is the least significant (lowest order) digit, denoted by LSD.

The value of the number in Eq. (1) is given in polynomial form by

$$N_r = \sum_{i=-m}^{n-1} a_i r^i \qquad ...(2)$$

$= a_{n-1} r^{n-1} + \dots + a_2 r^2 + a_1 r^1 + a_0 r^0 + a_1 r^{-1} + a_2 r^2 + \dots + a_m r^m$ where  $a_i$  is the digit in the *i*th position with a weight  $r^i$ .

Application of Eqs. (1) and (2) follows directly. For the decimal system r = 10 indicates that there are 10 distinguishable characters. Consider a number 4625.735 in decimal system. The number can be expressed as

$(4625.735)_{10} = 4 \times 10^3 + 6 \times 10^2 + 2 \times 10^1 + 5 \times 10^0 + 7 \times 10^{-1} + 3 \times 10^{-2} + 5 \times 10^{-3}$ where 10<sup>3</sup>, 10<sup>2</sup>, 10<sup>1</sup>, 10<sup>0</sup>, 10<sup>-1</sup>, 10<sup>-2</sup> and 10<sup>-3</sup> are the place values of the digits from left. MSD and LSD for this number are 4 and 5, respectively. In order to identify the system, in which the numbers, is written, we write the base or radix along with the number. -Thus,  $(4625.735)_{10}$  is written in decimal system as its base is 10.

The same number in octal system (base 8) can be expressed in decimal equivalent as  $(4625.735)_8 = 4 \times 8^3 + 6 \times 8^2 + 2 \times 8^1 + 5 \times 8^0 + 7 \times 8^{-1} + 3 \times 8^{-2} + 5 \times 8^{-3}$

Here  $8^3$ ,  $8^2$ ,  $8^1$ ,  $8^0$ ,  $8^{-1}$ ,  $8^{-2}$  and  $8^{-3}$  are the place values of the various position of the digits. The four number systems that are commonly used are shown in Table 3.1.

| Number system             | Base/Radix | Digit for the number system  |

|---------------------------|------------|------------------------------|

| Binary                    | 2 •        | 0, 1                         |

| Octal                     | 8          | 0, 1, 2, 3, 4, 5, 6, 7       |

| Decimal                   | 10         | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 |

| Haxadecimal               | 16         | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 |

| Contraction of the second |            | A, B, C, D, E, F             |

| Tal | )le | 3.1 |

|-----|-----|-----|

|-----|-----|-----|

## 3.1.2.1. Binary System

The binary number system, as the name suggests, consists of only two digits, namely 0 and 1. Since the system uses only two digits, its base is 2 and all the numbers in the system are written as a string of 0's and 1's. The binary digits 0 and 1 are generally referred to the cor mon abbreviation bit. For example, a binary number is shown below:

| 1           | 1 | 1 | 0 | 1           |

|-------------|---|---|---|-------------|

| 1           |   |   |   | 1           |

| Most        |   |   |   | Least       |

| significant |   |   |   | significant |

| bit         |   |   |   | bit         |

The right most bit is called the least significant bit and the left most bit, the most significant bit. The binary numbers are usually written with the base as a subscript in the form  $1101_2$  or  $(1101)_2$ .

The weights in the binary system are the powers of the base 2 just as the weights in the decimal system are the power of the base 10. The weights of the digits of the integral part are  $2^{9}$ ,  $2^{1}$ ,  $2^{2}$ , ... from right to left and the weights of the digits of the fractional system are the power of the base 10. The weights of the digits of the fractional system are  $2^{9}$ ,  $2^{1}$ ,  $2^{2}$ , ... from right to left and the weights of the digits of the fractional system are set in decimal equivalent as

> $(1)_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$ = 16 + 0 + 4 + 0 + 1 = (21)\_{10}

### 3.1.2.2. Octal Number System

The octal number system consist of 8 digits : 0, 1, 2, 3, 4, 5, 6, 7. Since the system uses 8 digits, the base of the system is 8 and each position in an octal number represents a power of the base (8). Thus, the octal number 7312 can be expressed in decimal equivalent as

$$(7312)_8 = 7 \times 8^3 + 3 \times 8^2 + 1 \times 8^1 + 2 \times 8^0$$

= 7 \times 512 + 3 \times 64 + 1 \times 8 + 2 \times 1

= 3584 + 192 + 8 + 2

= (3786)\_{10}

### 3.1.2.3. Hexadecimal Number System

The hexadecimal number system consists of 16 single character digits or symbols, where A, B, C, D, E, F represents the decimal value 10, 11, 12, 13, 14, 15, respectively. Thus, the hexadecimal number  $D_3E_0$  can be expressed in decimal equivalent as

$(D3E0)_{16} = D \times 16^3 + 3 \times 16^2 + E \times 16^1 + 0 \times 16^0$ = 13 × 4096 + 3 × 256 + 14 × 16 + 0 × 1 = 53248 + 768 + 224 = (54240)\_{10}

Table 3.2 shows the first 20 digits of some number systems.

# 3.2. CONVERSION FROM ONE NUMBER SYSTEM TO OTHER

It is just not sufficient to represent numbers in variou: number systems but also there should be flexibility to convert numbers from one system to another. There are different methods to serve this purpose. Various methods of conversions are described here.

# 3.2.1. Conversion of Any Number System to Decimal System

A number represented in any number system can be converted in any other system. In the field of computer the input and output values are in decimal. Computer professionals are often required to convert number in other systems to decimal and *vice-versa*. A number represented in any number system can be converted to equivalent decimal number system by a method known as Polynomial Evaluation method.

| Radix 10<br>(Decimal) | Radix 2<br>(Binary) | Radix 3<br>(Ternary) | Radix 4<br>(Quarternary) | Radix 5<br>(Quintal) | Radix 8<br>(Octal) | Radix 16<br>(Hexadecimal) |

|-----------------------|---------------------|----------------------|--------------------------|----------------------|--------------------|---------------------------|

| 0                     | 0.                  | . 0                  | 0                        | 0                    | 0                  | 0                         |

| 1                     | 1 3                 | 1                    | 1                        | 1                    | 1                  | 1                         |

| 2                     | 10                  | 2                    | 2                        | 2                    | 2                  | 2                         |

| 3                     | 11                  | 10                   | . 3                      | 3                    | 3                  | 3                         |

| 4                     | 100                 | 11                   | 10                       | 4                    | 4                  | 4                         |

| 5                     | 101                 | 12                   | 11                       | 10                   | 5                  | 5                         |

| 6                     | 110                 | 20                   | 12                       | 11                   | 6                  | 6                         |

| 7                     | . 111               | 21                   | 13                       | 12                   | 7                  | . 7                       |

| 8                     | 1000                | 22                   | 20                       | 13                   | 10                 | 8                         |

| 9                     | 1001                | 100                  | 21                       | 14                   | 11                 | 9                         |

| 10                    | 1010                | 101                  | 22                       | 20                   | 12                 | A                         |

| 11                    | 1011                | 102                  | 23                       | 21                   | 13                 | B                         |

| 12                    | 1100                | 110                  | 30                       | 22                   | 14                 | C                         |

Table 3.2: First Twenty Digits of Some Number System

(Contd.)

| 13 | 1101  | 111 | 31  | 23 | 15 | 'n |

|----|-------|-----|-----|----|----|----|

| 14 | 1110  | 112 | 32  | 24 | 16 | E  |

| 15 | 1111  | 120 | 33  | 30 | 17 | E  |

| 16 | 10000 | 121 | 100 | 31 | 20 | 10 |

| 17 | 10001 | 122 | 101 | 32 | 21 | 10 |

| 18 | 10010 | 200 | 102 | 33 | 22 | 12 |

| 19 | 10011 | 201 | 103 | 34 | 23 | 12 |

In this method, each digit within a number is multiplied by the weight of its position and then all these values are added. The following examples will illustrate the method.

Example 3.1. Convert the following binary numbers into equivalent decimal: (i) (10101101), (ii) (11010.111), Solution. (i)  $(10101101)_2 = 1 \times 2^7 + 0 \times 2^6 + 1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 1 \times 2^2$  $+ 0 \times 2^{1} + 1 \times 2^{0}$  $= 128 + 0 + 32 + 0 + 8 + 4 + 0 + 1 = (173)_{10}$ (*ii*)  $(11010.111)_2 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 1 \times 2^{-1}$  $+1 \times 2^{-2} + 1 \times 2^{-3}$  $= 16 + 8 + 0 + 2 + 0 + 0.5 + 0.25 + 0.125 = (26.875)_{10}$ Example 3.2. Convert decimal equivalent of (736.5)8 and (3FA.8)16. [AMIE, S '94] Solution.  $(736.5)_{8} = 7 \times 8^{2} + 3 \times 8^{1} + 6 \times 8^{0} + 5 \times 8^{-1}$  $= 448 + 24 + 6 + 0.625 = (478.625)_{10}$  $(3 \text{ FA.8})_{16} = 3 \times 16^2 + \text{F} \times 16^1 + \text{A} \times 16^0 + 8 \times 16^{-1}$  $= 768 + 15 \times 16 + 10 \times 1 + 0.5$  $= 768 + 240 + 10 + 0.5 = (1018.5)_{10}$

# 3.2.2. Conversion of Decimal System to Any Other Number System

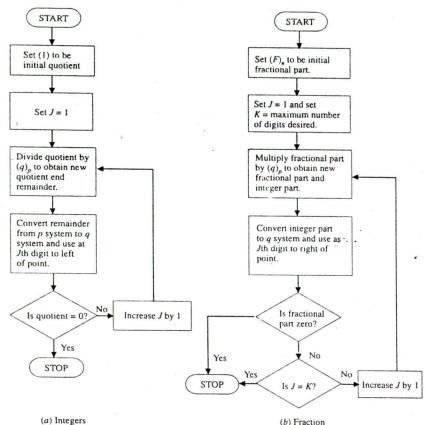

The conversion from decimal to other number system may be done by a method known as Dibble-Dabble method. In this method, the integer and fraction parts of the number are converted separately.

# 3.2.2.1. Conversion of Integer Part

In order to convert integer part of a decimal number to an equivalent number of other system of base b, divide the number (integer part) and each succeeding quotient by b until a zero quotient is obtained. The sequence of remainders, in reverse order, yields the base b representation of the number, *i.e.*, the least significant digit is the first remainder obtained and its most significant digit is the last remainder.

# 3.2.2.2. Conversion of Fractional Part

In order to convert fractional part of a decimal number to an equivalent number of other system of base *b*, multiply the number (fractional part) successively by base *b*. In each step the integer part obtained after multiplication is noted separately and the new fractional part is again used for new multiplication. The process continues until a zero fractional part or a duplicate fractional part or sufficient number of digits have been obtained. Then the sequence of integer parts of the products gives the base *b* representation of the fractional part. Then the first integer is the MSD and the last integer is the LSD of the fractional part of the convert number. The following examples will illustrate the method:

Example 3.3. Convert (a) the decimal number 41.6875 into a binary number, (b) the decimal number 153.513 into an octal number. Solution (c) The second seco

Solution. (a) The given number is (41.6875)10.

10.10.

Here integer part is 41 and fractional part .6875 For integer part,

| Base | Number |   |           | to national |

|------|--------|---|-----------|-------------|

| 2    | 41     |   | Remainder |             |

| 2    | . 20   |   | 1         | LSD         |

| 2    | 10     |   | 0         |             |

| 2    | 5      | - | 0         |             |

| 2    | 2      |   | 1         |             |

| 2    | 1      |   | 0         |             |

|      | 0      | _ |           | MSD         |

$<sup>(41)</sup>_{10} = (101001)_2$

### For fractional part,

| Number | · . | Base | k u | Product | Fractional<br>Part | Integer<br>Part |      |

|--------|-----|------|-----|---------|--------------------|-----------------|------|

| 0.0075 |     | 2    | -   | 1.3750  | .3750              | 1               | MSD  |

| 0.6875 | ×   | 2    |     | 0.7500  | .7500              | 0               |      |

| 0.3750 | ×   | 2    | =   |         |                    | 1               | 1.12 |

| 0.7500 | ×   | 2    | =   | 1.5000  | .5000              | 1               | LSD  |

| 0.5000 | ×   | 2    | =   | 1.0000  | .0000              | 1               | LSD  |

$(.6875)_{10} = (.1011)_2$

Hence,  $(41.6875)_{10} = (101001.1011)_2$

(b) The given number is  $(153.513)_{10}$

Here integer part is 153 and fractional part is .513 to more the more and For integer part,

| Base | Number |               | 8       |

|------|--------|---------------|---------|

| 8    | 153    | <br>Remainder |         |

| 8    | 19     | <br>1         | LSD     |

| 8    | 2      | <br>3         | 1. 1974 |

|      | 0      | <br>2         | MSD     |

|      |        |               |         |

$(153)_{10} = (231)_8$ For fractional part,

| Number |   | Base     | ~ 5    | Product             | Fractional<br>Part    | Integer<br>Part |

|--------|---|----------|--------|---------------------|-----------------------|-----------------|

| 0.513  | × | 8        | L = 1  | 4.104               | .104                  | Fact 4          |

| 0.104  | × | 8        | =      | 0.832               | .832                  | 0 10            |

| 0.832  | x | 8        | - 24   | 6.656               | .656                  | 6               |

|        |   | 8        |        | 5.248               | .248                  | ru /o * 5       |

| 0.656  | × | 0        | 1 arts | (12) A 1610 14      | mar + talk *          | At an in the    |

|        |   |          |        | A CONTRACTOR OF STR |                       | 计可定 输出的运行       |

| 96.3   |   | (.531)10 | =      | (.4065)8            | and the second second | and and         |

Hence,  $(153.531)_{10} = (231.4065 \dots)_8$ .

Example 3.4. Convert (0.2)10 to its octal form.

| Number |   | Base |   | Product | Fractional<br>Part | Integer<br>Part |     |

|--------|---|------|---|---------|--------------------|-----------------|-----|

| 0.2    | × | 8    | = | 1.6     | .6                 | 1               | MSD |

| 0.6    | × | 8    | = | 4.8     | .8                 | 4               |     |

| 0.8    | × | 8    | = | 6.4     | .4                 | 6               |     |

| 0.4    | × | 8    | = | 3.2     | .2                 | 3               |     |

| 0.2    | × | 8    | = | 1.6     | .6                 | 1               |     |

Solution.

At the fourth step we again obtain .2 as the fractional part, hence the digits 1463 will repeat, giving  $(0.2)_{10} = (0.1463 \ 1463 \ \dots )_8$ .

**Example 3.5.** Convert  $(429.32)_{10}$  into haxadecimal. Solution. The given number is  $(429.32)_{10}$ . Here integer part is 429 and fractional part .32 For integer part,

| Base | . Number |   |           |     |

|------|----------|---|-----------|-----|

| 16   | 429      |   | Remainder |     |

| 16   | 26       | _ | D         | LSD |

| 16   | 1        |   | Α         |     |

| *    | 0        |   | 1         | MSD |

For fractional part,

| Number |   | Base |   | Product           | Fractional<br>Part | Integer<br>Part | _   |

|--------|---|------|---|-------------------|--------------------|-----------------|-----|

| .32    | × | 16   | = | 5.12              | .12                | 5               | MSE |

| .12    | × | _16  | = | 1.92              | .92                | 1               |     |

| .92    | × | 16   | = | 14.52             | .52                | E               |     |

| •      |   |      |   | Up to third place |                    |                 |     |

Hence,  $(429.32)_{10} = (1 \text{ A D}, 5 1 \text{ E})_{16}$  up to third place.

### 3.3. DIRECT METHOD OF CONVERTING THE NUMBER FROM ONE SYSTEM TO OTHER

Whenever the radix of one system can be expressed in powers of the radix of other system, the system can be converted directly by forming pair of numbers 2, 3 or 4 noting the power of the radix.

#### 3.3.1. Conversion from Octal to Binary

The octal system is a system having base 8. Since  $8 = 2^3$ , each octal digit is a union of 3 bit representation. An octal number can be converted to binary number by converting each octal digit to its binary equivalent with 3 bits. The example below illustrate the method.

Example 3.6. Convert to binary form (a)  $(617025)_8$ , (b)  $(43.0276)_8$

Solution. (a)  $(617025)_8$  = (110 001 111 000 010 101 )<sub>2</sub>

(b)  $(43.0276)_8$  = (100 011 .000 010 111 110 )<sub>2</sub>

### 3.3.2. Conversion from Binary to Octal

A binary number can be converted to octal number by partitioning the number into 3 bit groups formed from left to right for the fractional part of the number and from right

(a) Integers

Fig. 3.1: Flow chart of radix conversion

to left for the integer part. If the number of bits in the integer part is not a multiple of 3, we insert leading 0s, as leading 0s have no significance for the integer part. If the number of bits in the fractional part is not a multiple of 3, then we introduce trailing 0s, as trailing 0s have no significance in the fractional part.

The following examples will illustrate the procedure.

Example 3.6. Convert (1101010)<sub>2</sub> into octal

$(1101010)_2 = 001 101 010$ Solution.

(Group three digits from right)

$= (152)_8$

(Convert each group to an octal digit)

Example 3.7. Convert (11 11 0101 111 . 10001)2 into octal.

Solution.  $(11110101111.10001)_2 = 011 110 101$ 111.100 010

> (Group three digits from left of the binary point)

(Group three digits from right of the binary point)

### $= (3657.42)_8$

(Convert each group to an octal digit)

#### 3.3.3. Conversion from Hexadecimal to Binary

The hexadecimal system is a system having base 16. Since  $16 = 2^4$ , each digit is an unique 4 bit representation. For conversion from hexadecimal to binary, each digit of hexadecimal number is to be replaced by its binary equivalent with 4 bits.

Example 3.8. Convert (2 AB)<sub>16</sub> into binary. Solution.  $(2AB)_{16} = \frac{0010}{2} \frac{1010}{A} \frac{1011}{B} = (0010101011)_2$

#### 3.3.4. Conversion from Binary to Hexadecimal

A binary number can be converted to hexadecimal number by partitioning the number into 4 bit groups starting from left to right for the fractional part of the number and from right to left for the integer part. If the number of bits in the integer part is not a multiple of 4, we insert leading 0s and if the number of bits in the fractional part is not a multiple of 4, then we introduce trailing 0s.

The following examples illustrate the method. Example 3.9. Convert  $(11011111)_2$  into hexadecimal system. Solution.  $(11011111)_2 = \underline{1101} \quad \underline{1111}$ (Group four digits from right)

$$= DF$$

(Convert each group to hexadecimal digits)

Hence,  $(11011111)_2 = (DF)_{16}$

#### 3.3.5. Conversion from Hexadecimal to Octal and vice-versa

For the conversion of number from hexadecimal system to octal system, hexadecimal number is first converted to binary and then binary number to octal and for the conversion from octal to hexadecimal, convert the given octal number to binary and then binary to hexadecimal.

The following examples will illustrate the procedure.

Example 3.10. Convert (IE.C)<sub>16</sub> to equivalent octal system.

Solution. (IE.C)<sub>16</sub> = 0001 1110 . 1100 =  $(00011110.1100)_2$ = 011 110 110 (grouping into three) =  $(36.6)_8$ The octal equivalent of (IE.C)<sub>16</sub> is  $(36.6)_8$ . Example 3.11. Convert (46.57)<sub>8</sub> to its equivalent hexadecimal number.

Solution.  $(46.57)_8 = 100 110 . 101 111$

$= (100110.101111)_{2}$

= 0010 0110 . 1011 1100 (grouping into four)

$= (26.BC)_{16}$

#### **3.4. BINARY ARITHMETIC**

Processors of computers perform arithmetic operations only on binary pumbers. We should thus know how four basic operations are performed using binary numbers.

### · 3.4.1. Addition

The rules of binary addition are

[AMIE, W '93]

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 0$  with a carry of 1

$1 + 1 + 1 = 1$  with a carry of 1

Carryovers are performed in the same manner as in decimal arithmetic. Since 1 is the largest digit in the binary system, any sum greater than 1 requires that a digit be carried over. The exact procedure is illustrated with examples.

Example 3.12. Perform  $(101)_2 + (001)_2$ Solution. Carry 1  $\frac{1 \ 0 \ 1}{1 \ 1 \ 0}$ Example 3.13. Perform  $(11011)_2 + (101011)_2$ Solution. Carry 1 1 1 1  $\frac{1 \ 0 \ 1 \ 0 \ 1 \ 1}{1 \ 0 \ 0 \ 0 \ 1 \ 1}$

### 3.4.2. Subtraction

The rules for binary subtraction are

0 - 0 = 0 1 - 0 = 1 1 - 1 = 00 - 1 = 1 w

0 - 1 = 1 with a borrow of 1 from the next column to the left (value borrowed is equal to 10).

Note that if the lower digit is larger than the upper digit, it is necessary to borrow from the column to the left, the value borrowed depends upon the base of the number and is always the decimal equivalent of the base, i.e., for binary system it is  $2(10_2)$ .

The exact procedure is illustrated with examples. **Example 3.14.** Perform  $(10110)_2 - (01001)_2$ . Solution. 0 0 1 0 1 1 0  $- \frac{0}{0} \frac{1}{1} \frac{0}{0} \frac{0}{1} \frac{1}{0} \frac{0}{1}$

**Explanation :** To explain the case when we cannot borrow 1 from the next column because the column contains 0, let us look the decimal difference.

|   | 6 | 9 | 9 | 9 |   |   |  |

|---|---|---|---|---|---|---|--|

|   | 7 | 0 | 0 | 0 | 4 | 3 |  |

| - | 4 | 8 | 4 | 3 | 5 | 1 |  |

| - | 2 | 1 | 5 | 6 | 9 | 2 |  |

|   |   |   |   |   |   | - |  |

We have borrowed from the sixth column for the second column since the third, fourth and fifth columns contained zeros. After borrowing, the third, fourth and fifth columns contain 10 - 1 = 9. The same thing happens in binary subtraction except that after borrowing the zero columns contain 10 - 1 = 1.

Example 3.15. Perform  $(110.001)_2 - (11.111)_2$ Solution. 0 0 1 1 1 1 0.0 0 1  $-\frac{1}{0}10.0010$

### 3.4.3. Multiplication

Multiplication is nothing but successive addition. Most of the computers perform multiplication operations in binary using additive approach. Multiplication in the binary system also follows the same general rules as for decimal multiplication.

The rules for binary multiplication are

| 0 | × | 0 | = | 0 |  |

|---|---|---|---|---|--|

| 1 | × | 0 | = | 0 |  |

| 0 | × | 1 | = | 0 |  |

| 1 | × | 1 | = | 1 |  |

The following examples illustrate binary multiplication.

Example 3.16. Perform (10110), × (1101),

|       |   |    |    |   |    | 1  | 0   | 1  | 1 | 0 |   |

|-------|---|----|----|---|----|----|-----|----|---|---|---|

|       |   |    |    |   |    | ٠x | 1   | 1  | 0 | 1 |   |

|       |   |    |    |   |    | 1  | 0   | 1  | 1 | 0 |   |

|       |   |    |    |   | 0  | 0  | 0   | 0  | 0 |   | 2 |

|       |   |    |    | 1 | 0  | 1  | 1   | 0  |   | • |   |

|       |   |    | 1  | 0 | 1  | 1  | 0   |    |   |   |   |

|       |   | 1  | 0  | 0 | 0  | 1  | 1   | 1  | 1 | 0 |   |

| 10110 | ~ | 11 | 01 | _ | 1/ | n  | 111 | 11 | 0 |   |   |

Hence,  $10110_2 \times 1101_2 = 100011110_2$

### 3.4.4. Division

Solution.

Division can be carried out by repetitive subtractions. Rules for binary division are

$\frac{0}{0} = \text{No meaning}$  $\frac{1}{0} = \text{No meaning}$  $\frac{0}{1} = 0$  $\frac{1}{1} = 1$

Following examples illustrate binary division. Example 3.17. Divide (i) (1100010)<sub>2</sub> by (111)<sub>2</sub>

| •         |     |        |           |        |          |               |      |           |      |

|-----------|-----|--------|-----------|--------|----------|---------------|------|-----------|------|

|           | 1   |        | (ii) (1   | 00001) | 2 by (11 | $(0)_{2}$     |      |           |      |

| Solution. | (i) | 111)   | 1100010   | (1110  |          | ( <i>ii</i> ) | 110) | 100001 (1 | 01.1 |

|           |     | ×.     | 111 .     |        |          |               |      | 110       |      |

|           |     |        | 01010     |        |          |               |      | 001001    |      |

|           |     |        | 111       |        |          |               |      | 110       |      |

|           |     |        | 00111     |        |          |               | ÷    | 00110     |      |

| × 1       |     |        | 111       |        |          |               |      | 110       |      |

|           |     |        | 000       |        |          |               |      | 000       |      |

|           | An  | s. (11 | $10)_{2}$ |        |          |               | Ans  | (101.1)   | *    |

| Example 3.18. | Divide | $(111011)_2$ by $(0111)_2$ . |

|---------------|--------|------------------------------|

| Solution.     | 0111 ) | 111011 ( 1000.011011         |

| 0111  |

|-------|

| 01100 |

| 111   |

| 1010  |

| 111   |

| 01100 |

| 111   |

| 1010  |

|       |

|       |

Ans. 1000.011

### 3.5. COMPLEMENTS

Subtraction of two numbers in a computer is complicated and expensive in terms of circuit specially for repeated borrowing from one column to another. Complements can be used to reduce from subtraction to addition. It avoids the possibility of repeated borrowing from one column to another and, hence, borrow circuits are eliminated, and cost is reduced.

There are two types of complements, the radixminus-one complement and r dix complement. In decimal system, they are called nines complement and tens complement. The nines complement of a number is obtained by subtracting each digit of the number from 9 and 10s complement of the number is its nines complement plus one. In binary system, they are called 1's complement and 2's complement.

#### 3.5.1. 1's Complement

The 1's complement of a binary number can be obtained by subtracting each digit of the number from 1 which is same as replacing 1 by 0 and 0 by 1. For example, 1's complement of 110101 is 001010.

### 3.5.2. 2's Complement

The 2's complement of a binary number can be obtained from either of the following procedure:

- (i) First complement each bit of the number (i.e., replace 1 by 0 and 0 by 1) to get 1's complement. Add 1 to this number to get 2's complement. For example, consider the number 13 whose binary representation is 1101. 1's complement is 0010. Now, adding 1 to this number gives 0011 which is 2's complement representation for -13.

- (ii) Scan the binary numbers from right to left and complement all bits appearing after the first appearance of 1. For example, 2's complement of 1 0 1 0 is 0 1 1 0.

First appearance of 1 from right to left.

### 3.5.3. Subtraction using Complements

If the number of digits of integer part in subtrahend is less than the number of digits in minuend, add 0 on the left hand of subtrahend to make equal number of digits and for fractional part add 0 on the right of subtrahend.

### 3.5.3.1. Using 1's Complement

Procedure : (a) Complement the subtrahend (the number to be subtracted)

(b) Add the complement with minuend (from the number to be subtracted)

(c) Delete the higher order carry, if any, and add to the sum obtained in (b). If there is no carry (when a larger number is subtracted from a smaller number), recomplement the sum and attach a negative sign to obtain the result.

Example 3.19. Perform  $(1101)_2 - (110)_2$  using one's complement.

Solution.

1 1 0 1 + 1 0 0 1 (1) 0 1 1 0 + 1 0 (1) 0 1 1 1 (1) 0 1 1 1 (1) 0 1 1 1 (1) 0 1 1 1 (1) 0 1 1 1

Ans. (0111)<sub>2</sub>

Example 3.20. Subtract  $(100011)_2$  from  $(010010)_2$  using one's complement. Solution. 0 1 0 0 1 0 Minuend

Solution.

+ 0 1 1 1 0 0 One's complement of subtrahend

101110

As there is no carry, the minuend is smaller than the subtrahend. Thus, it is required to complement the sum and attach a negative sign to obtain the result.

Ans.  $-(010001)_2$

### 3.3.3.2. Using 2's Complement

The procedure for subtraction using 2's complement is almost identical with 1's complement except that the higher order carry is ignored.

The following examples win illustrate the procedure.

Example 3.21. Perform (11010101)<sub>2</sub> - (10011010)<sub>2</sub> using 2's complement.

Solution. 1's complement of subtrahend 01100101

2's complement of subtrahend 01100110

1 1 0 1 0 1 0 1 Minuend

+ 0 1 1 0 0 1 1 0 2's complement of subtrahend

$(1) \overline{0} \overline{0} \overline{1} \overline{1} \overline{1} \overline{0} \overline{1} \overline{1}$

Î

#### Neglect carry

**Ans.**  $(00111011)_2$

Example 3.22. Subtract (01000)<sub>2</sub> from (01111)<sub>2</sub>

(i) using 1's complement

(ii) using 2's complement

Solution. (i) Complement of subtrahend 10111

01111 Minuend

+ 1 0 1 1 1 1's complement of subtrahend

(1) 0 0 1 1 0+ 10 0 1 1 1

Ans. (00111)<sub>2</sub>

(ii) 2's complement of subtrahend is 10111 (1's complement) + 1 = 11000

01111 Minuend

+ 1 1 0 0 0 2's complement of subtrahend

[AMIE, W '93]

# (1)0 0 1 1 1

#### Neglect carry

Ans. (00111)<sub>2</sub>

Example 3.23. Perform (101)<sub>2</sub> - (11011)<sub>2</sub>.

Solution.

101 Minuend

+ 0 0 1 0 1 2's complement of subtrahend

01010

As there is no final carry (the minuend is smaller than the subtrahend), taking 2's complement of 01010 and assigning a -ve sign provides the answer.

Ans.  $-(10110)_2$

# 3.6. COMPARISON BETWEEN 1'S AND 2'S COMPLEMENTS

A comparison between 1's and 2's complements reveals the advantages and disadvantages of each. The 1's complement has the advantage of being easier to implement by digital components since the only thing that must be done is to change 0's into 1's and 1's into 0's. The implementation of the 2's complement may be obtained in two ways: (a) by adding 1 to the least significant digit of the 1's complement, and (b) by scanning the number from right to left and complementing all bits appeared after the first appearance of 1. During subtraction of two numbers by complements, the 2's complement is advantageous in that only one arithmetic addition operation is required. The 1's complement requires two arithmetic addition when an end around carry occurs. The 1's complement has the additional disadvantage of possessing two arithmetic zeros, one with all 0's and one with all 1's which may complicate matters while 2's complement has only one zero representation.

# 3.7. REASONS FOR USE OF BINARY SYSTEM IN THE DESIGN OF COMPUTER

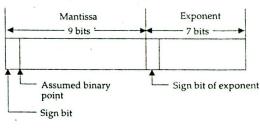

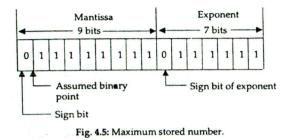

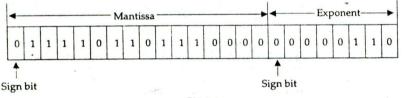

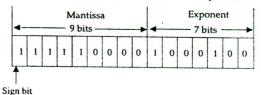

The reasons of using binary system by the computer are: